数电第7周周结_by_yc

一、通用双向移位寄存器:

- 功能描述:

4位的双向移位寄存器,含控制输入端(ctrl)、串行输入端(Dsl、Dsr)、4个并行输入端和4个并行输出端,要求实现5种功能:异步置零、同步置数、左移、右移和保持原状态不变,功能如下:

.center { width: auto; display: table; margin-left: auto; margin-right: auto }

| ctrl | action |

|---|---|

| 00 | 保持 |

| 01 | 右移 |

| 10 | 左移 |

| 11 | 并行输入 |

- 设计方案:

①异步置零:复位信号需放入敏感列表;

②优先级:reset>ctrl;

③ctrl的多方案可以用case来完成 - 关键代码:

always@(posedge clk or negedge reset) begin

if(~reset)

Dout <= 4'b0000; //Asynchronous zero setting

else begin

case(ctrl)

2'b00: Dout <= Dout; //remain

2'b01: Dout <= {Dsr, Dout[3:1]}; //shift right

2'b10: Dout <= {Dout[2:0], Dsl}; //Shift left

2'b11: Dout <= Din; //Parallel input

endcase

end

end

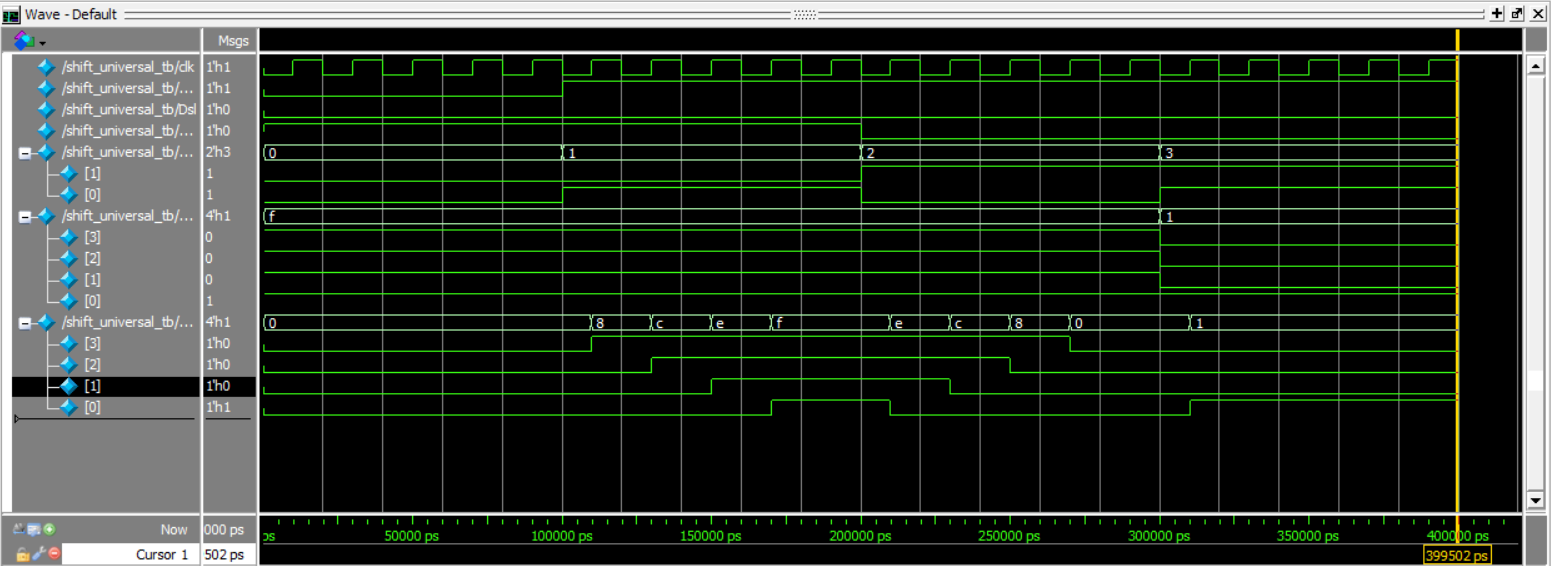

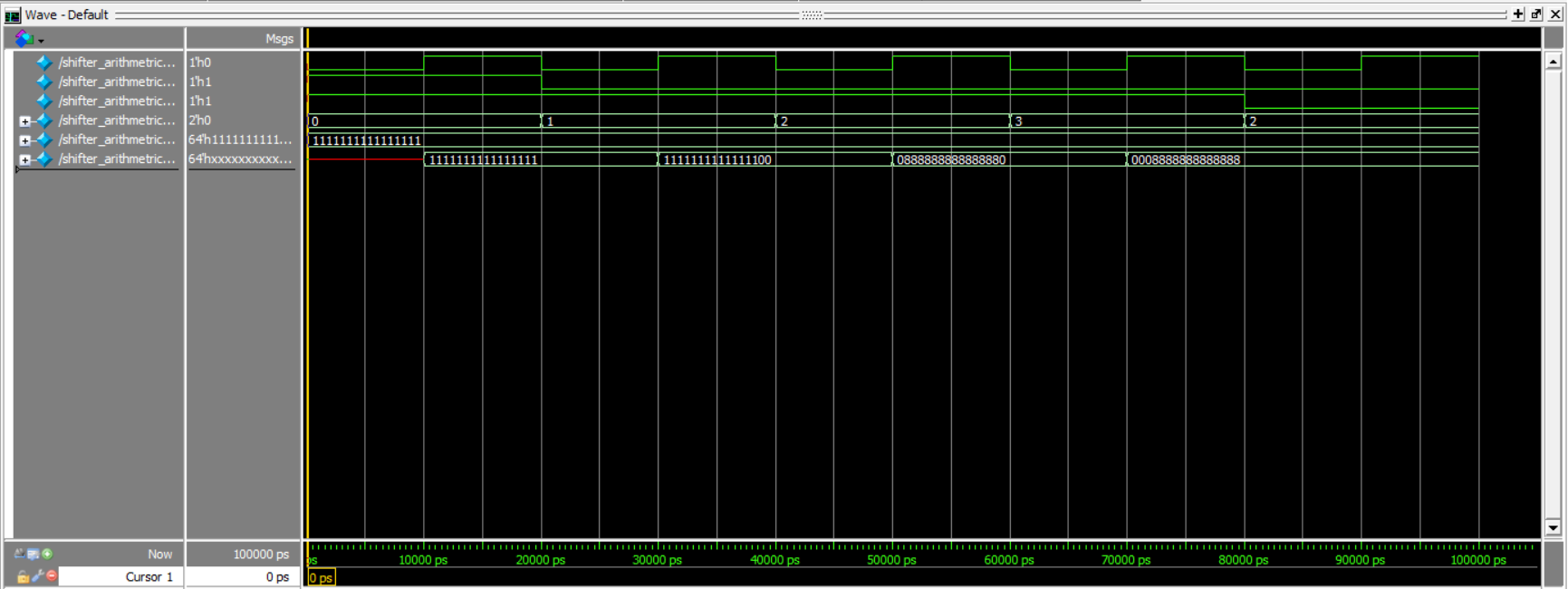

- 仿真验证:

分别控制实现保持、右移、左移和并行输入。

initial begin

clk=0;

forever #10 clk=~clk;

end

initial begin

reset=0; Dsl=0; Dsr=1; ctrl=2'b00; Din=4'b1111;

#100 reset=1; Dsl=0; Dsr=1; ctrl=2'b01; Din=4'b1111;

#100 reset=1; Dsl=0; Dsr=0; ctrl=2'b10; Din=4'b1111;

#100 reset=1; Dsl=0; Dsr=0; ctrl=2'b11; Din=4'b0001;

#100 $stop;

end

输出波形如下图所示,符合题意。

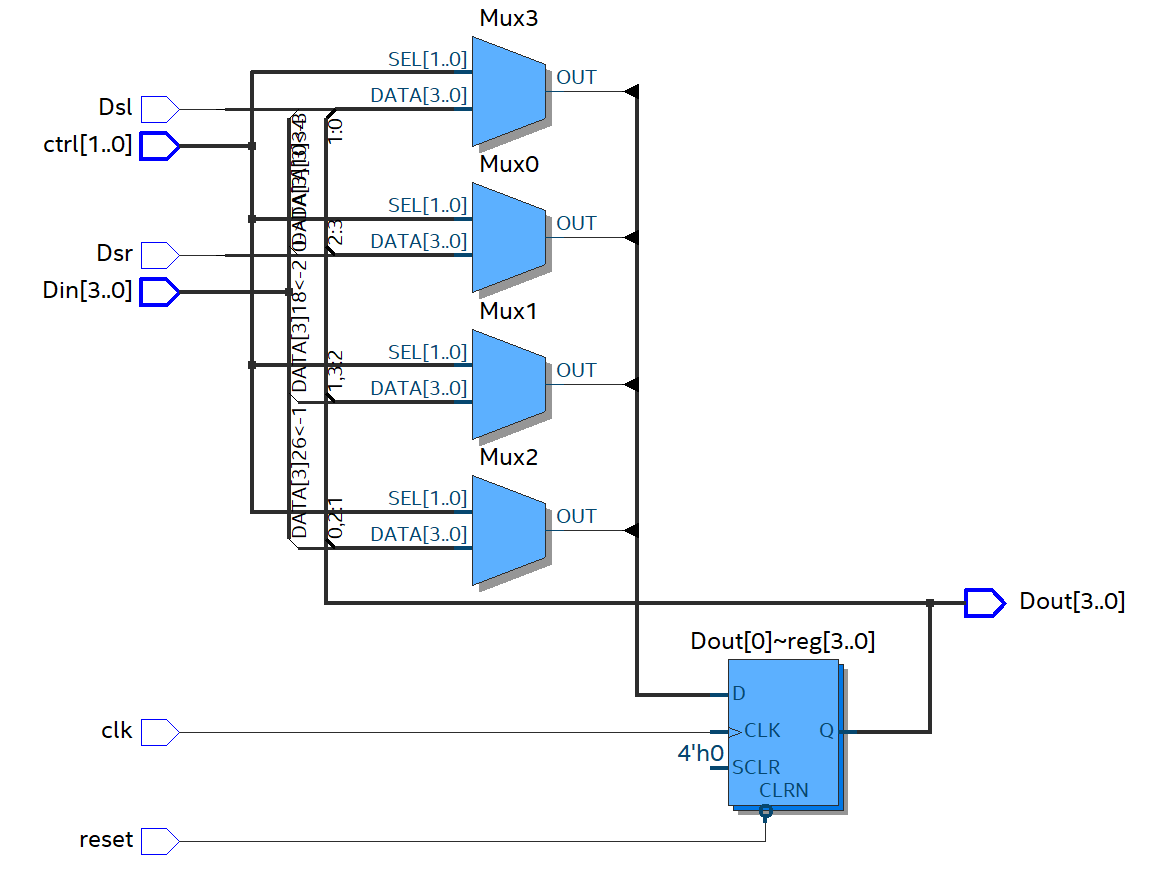

- 综合结果:

- 总结反思:

看好模块名称!!!

二、带控制组的触发器组:

功能描述:

16位D触发器,以byteena来控制寄存器的高低字节是否被写入。byteena[1]控制高字节d[15:8],而byteena[0]控制低字节d[7:0].resetn是低电平有效的同步复位信号.所有DFF由时钟的上升沿触发.设计方案:

①普通的16位同步复位D触发器,resetn不在敏感列表中

②优先级:reset>byteena;

③byteena的多方案可以用case来完成关键代码:

always @(posedge clk) begin

if(~resetn)

q <= 16'b0000000000000000;

else begin

case(byteena)

2'b00: q <= q;

2'b01: q <= {q[15:8],d[7:0]};

2'b10: q <= {d[15:8],q[7:0]};

2'b11: q <= d;

endcase

end

end

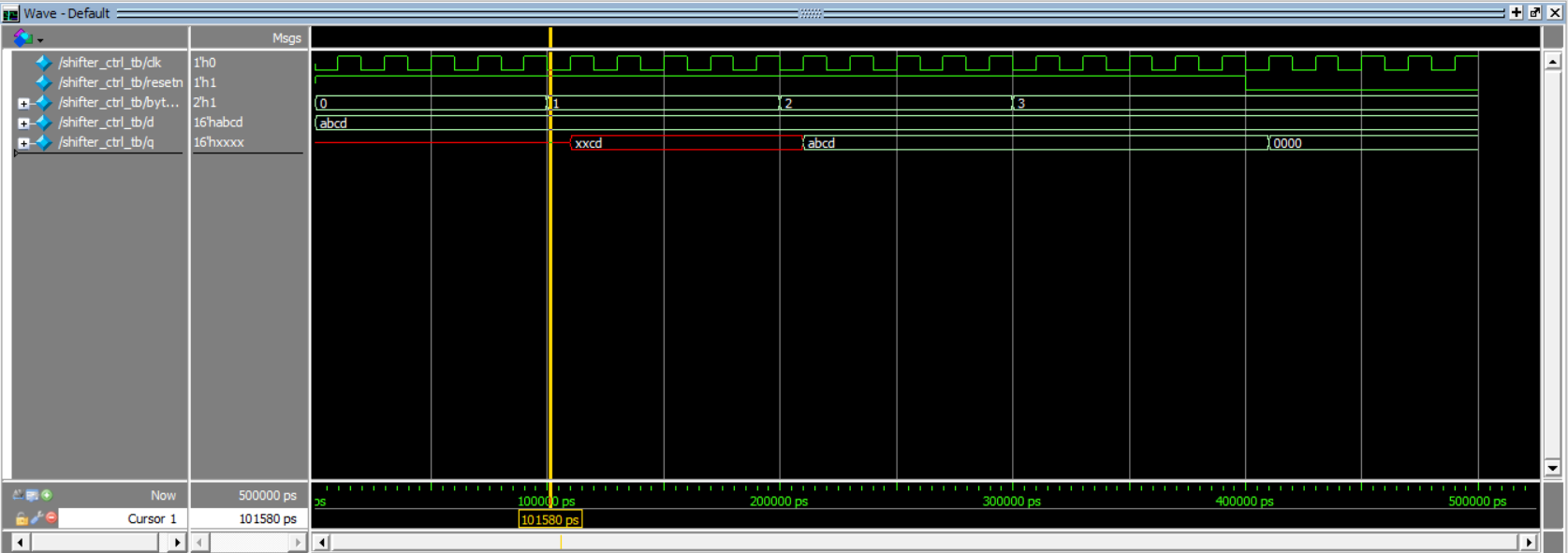

- 仿真验证:

依次设计进行:不赋值、低位赋值、高位赋值、全部赋值

initial begin

clk=0;

forever #10 clk=~clk;

end

initial begin

resetn=1; byteena=2'b00; d=16'b1010101111001101;

#100 resetn=1; byteena=2'b01; d=16'b1010101111001101;

#100 resetn=1; byteena=2'b10; d=16'b1010101111001101;

#100 resetn=1; byteena=2'b11; d=16'b1010101111001101;

#100 resetn=0;

#100 $stop;

end

如图,在第一个大周期内,输出悬空,未赋值;第二个时钟周期内,完成了低位赋值,高位悬空;三四周期依次完成了高位赋值和全赋值,符合题意。

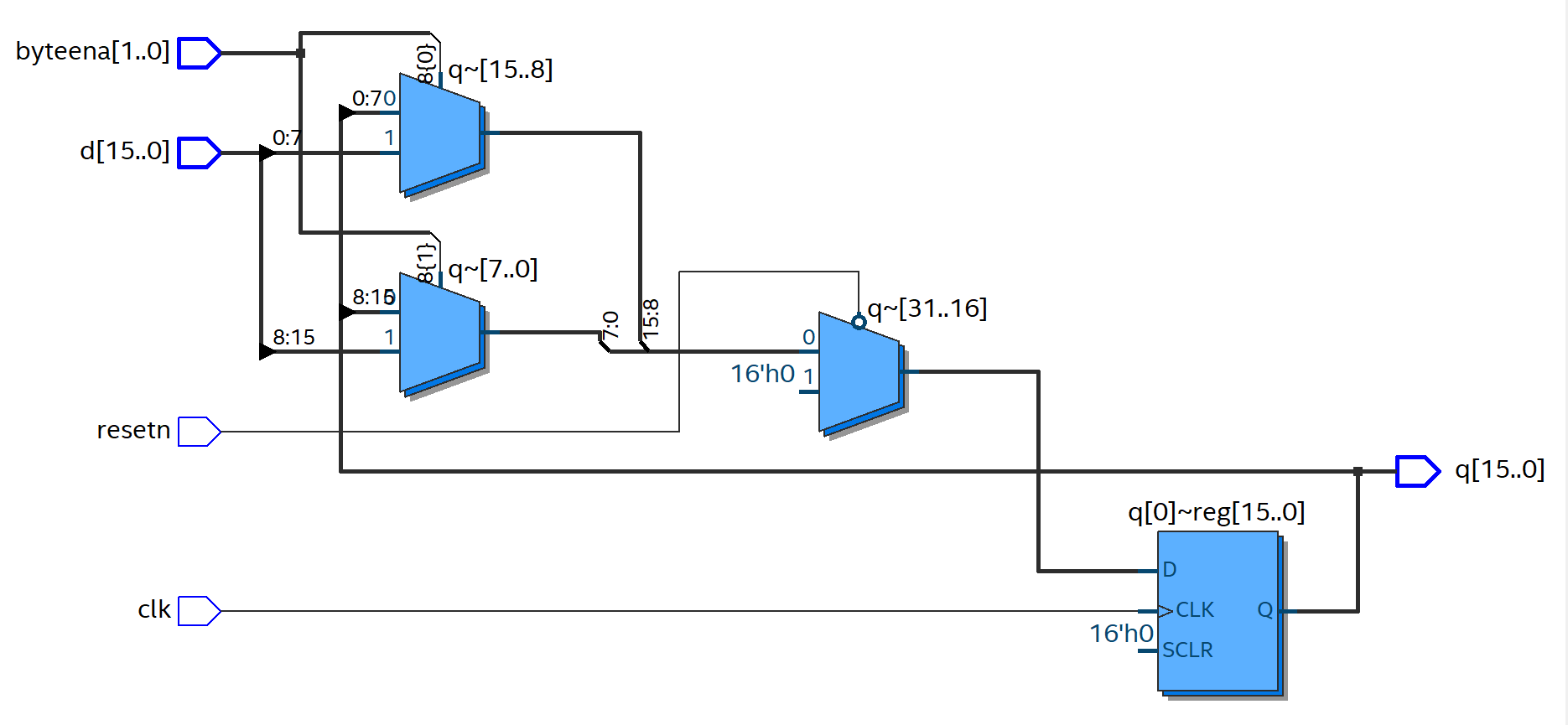

- 综合结果:

三、算数左右移:

- 功能描述:

64位算术移位寄存器,具有同步load数据功能,具体移位由ctrl控制,由下表所示:

.center { width: auto; display: table; margin-left: auto; margin-right: auto }

| ctrl | action |

|---|---|

| 00 | 算术左移1位 |

| 01 | 算术左移8位 |

| 10 | 算术右移1位 |

| 11 | 算术右移8位 |

- 设计方案:

①算术右移时,需要复制最高位,可以通过拼接运算符来完成;算术左移同逻辑左移

②优先级:load>ena>ctrl;

③ctrl的多方案可以用case来完成 - 关键代码:

always@(posedge clk) begin

if(load)

q <= data;

else if(ena) begin

case(ctrl)

2'b00: q <= {q[62:0], 1'b0};

2'b01: q <= {q[55:0], 8'b0};

2'b10: q <= {1'b0, q[63:1]};

2'b11: q <= {8'b0, q[63:8]}; //unsigned number

endcase

end

end

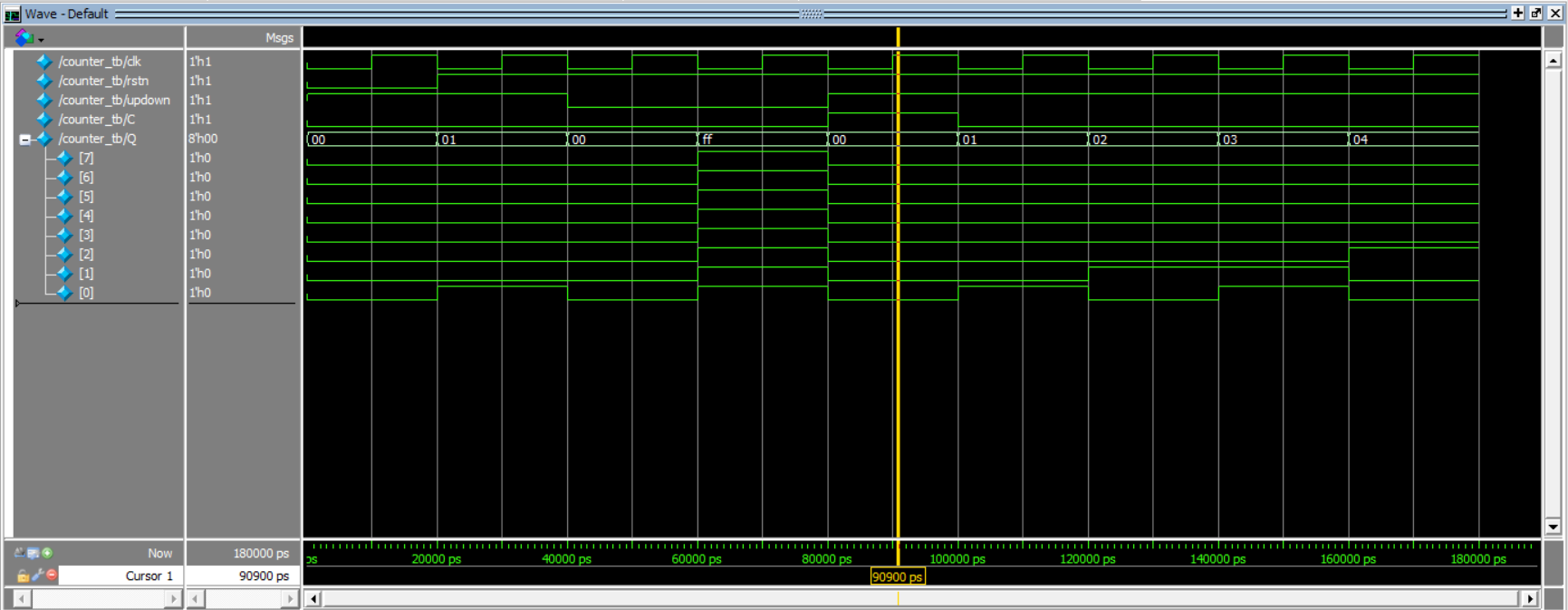

- 仿真验证:

分别设计进行加载数据、算术左移1、算术左移8、算术右移1、算术右移8、不移位。

initial begin

clk=0;

forever #10 clk=~clk;

end

initial begin

load=1; ena=1; ctrl=2'b00; data=16'h1111111111111111;

#20 load=0; ena=1; ctrl=2'b01; data=16'h1111111111111111;

#20 load=0; ena=1; ctrl=2'b10; data=16'h1111111111111111;

#20 load=0; ena=1; ctrl=2'b11; data=16'h1111111111111111;

#20 load=0; ena=0; ctrl=2'b10; data=16'h1111111111111111;

end

得到对应波形如下图所示,符合预设。

- 综合结果:

- 总结分析:

拼接运算符的正确应用:q <= {{8{q[63]}}, q[63:8]}。

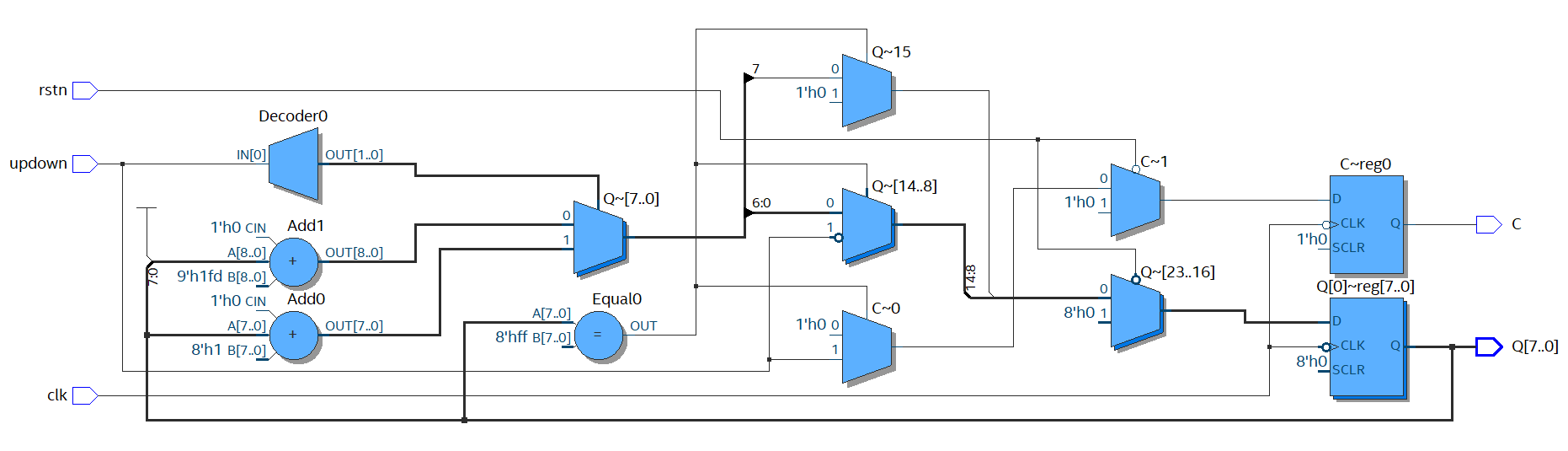

四、8位同步二进制加减法计数器:

功能描述:

8位同步二进制加减法计数器,输入为时钟端clk(下降沿有效)和异步清除端rstn(低电平有效),加减控制端updown,当updown为1时执行加法计数,为0时执行减法计数;输出为进位端C和8位计数输出端Q设计方案:

①异步置零:复位信号需放入敏感列表;

②优先级:rstn>updown;

③updown的多方案可以用case来完成.

④进位端C只有在从255->0时才为高电平,其余为低电平,可以将当前值是否为255作为一级判断。关键代码:

always @(negedge clk) begin

if(~rstn) begin Q <= 8'b0;C=0; end

else if(Q == 8'b11111111) begin

if(updown == 1) begin C=1; Q=8'b00000000; end

else begin C=0; Q=8'b11111110; end

end

else begin

case(updown)

1'b1: begin Q = Q + 1; C=0; end

1'b0: begin Q = Q - 1; C=0; end

endcase

end

end

- 仿真验证:

设计含加减法和255->0的testbench

initial begin

clk=0;

forever #10 clk=~clk;

end

initial begin

rstn=0; updown=1;

#20 rstn=1; updown=1;

#20 rstn=1; updown=0;

#40 rstn=1; updown=1;

#100 $stop;

end

相应的波形图如下,加减法合题意,且由255->0时,相应的进位输出为1.

- 综合结果:

五、分频器:

功能描述:

N分频时钟,50%占空比,上升沿采样,异步低电平复位,不可采用电平触发,同一敏感列表不可同时出现同一个信号的上升沿和下降沿。设计方案:

①异步复位:rstn信号出现在敏感列表中;

②因为对于奇偶性不同的N值,涉及到分别在上升沿和下降沿进行翻转,故需对N值得奇偶进行讨论:

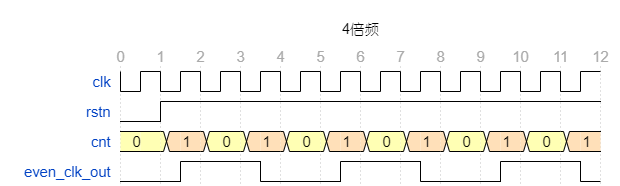

N为偶数:

为实现能够对时钟频率进行分频,则需要对时钟的翻转次数进行计数,这里采用对时钟上升沿进行计数,cnt每加一,则说明经过了一个时钟周期,如按图中需分四倍频,则需经过两个时钟周期,进行一次反转,四倍频即为\({cnt==1}\),则进行一次翻转,推广到偶数的N,则为每逢\({cnt==(N>>1)-1}\),进行一次翻转。

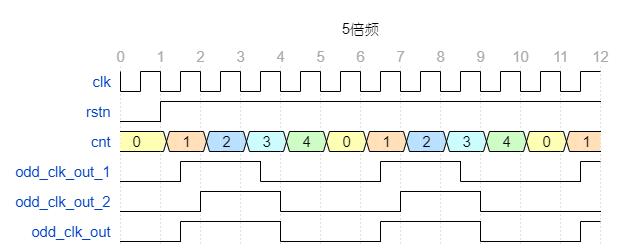

N为奇数:

而奇数的特殊点在于涉及到在时钟的上升沿和下降沿分别翻转,则可将其等效为两个偶倍频的并.

如图中\({odd\_clk\_out\_1}\),\({odd\_clk\_out\_2}\),其中前者在时钟上升沿进行翻转;后者在时钟下降沿进行翻转。

同时依旧在上升沿进行计数(图上cnt有一定误差,画不到中间的部分),对于图中五倍频来说,前者在\({cnt==0|cnt==2}\)进行翻转,后者在\({cnt==1|cnt==3}\)进行翻转,

推广到奇数的N,则有前者在\({cnt==0|cnt==N>>1}\)进行翻转,后者在\({cnt==1|cnt==N>>1+1}\)进行翻转。

- 关键代码:

//even

always@(posedge clk, negedge rstn) begin

if(!rstn)

even_cnt <= 1'b0;

else if(even_cnt == (N>>1'b1)-1'b1)

even_cnt <= 1'b0;

else

even_cnt <= even_cnt + 1'b1;

end

always@(posedge clk, negedge rstn) begin

if(!rstn)

even_clk_out <= 1'b0;

else if(even_cnt == (N>>1'b1)-1'b1)

even_clk_out <= ~even_clk_out;

else

even_clk_out <= even_clk_out;

end

//odd

always@(posedge clk, negedge rstn) begin

if(!rstn)

odd_cnt <= 1'b0;

else if(odd_cnt == N-1'b1)

odd_cnt <= 1'b0;

else

odd_cnt <= odd_cnt + 1'b1;

end

always@(posedge clk, negedge rstn) begin

if(!rstn)

odd_clk_out1 <= 1'b0;

else if(odd_cnt == N>>1'b1 | odd_cnt == 1'b0)

odd_clk_out1 <= ~odd_clk_out1;

else

odd_clk_out1 <= odd_clk_out1;

end

always@(negedge clk, negedge rstn) begin

if(!rstn)

odd_clk_out2 <= 1'b0;

else if(odd_cnt == (N>>1'b1)+1'b1 | odd_cnt == 1'b1)

odd_clk_out2 <= ~odd_clk_out2;

else

odd_clk_out2 <= odd_clk_out2;

end

assign odd_clk_out = odd_clk_out1 | odd_clk_out2;

assign clk_out = (N%2==0) ? even_clk_out : odd_clk_out;

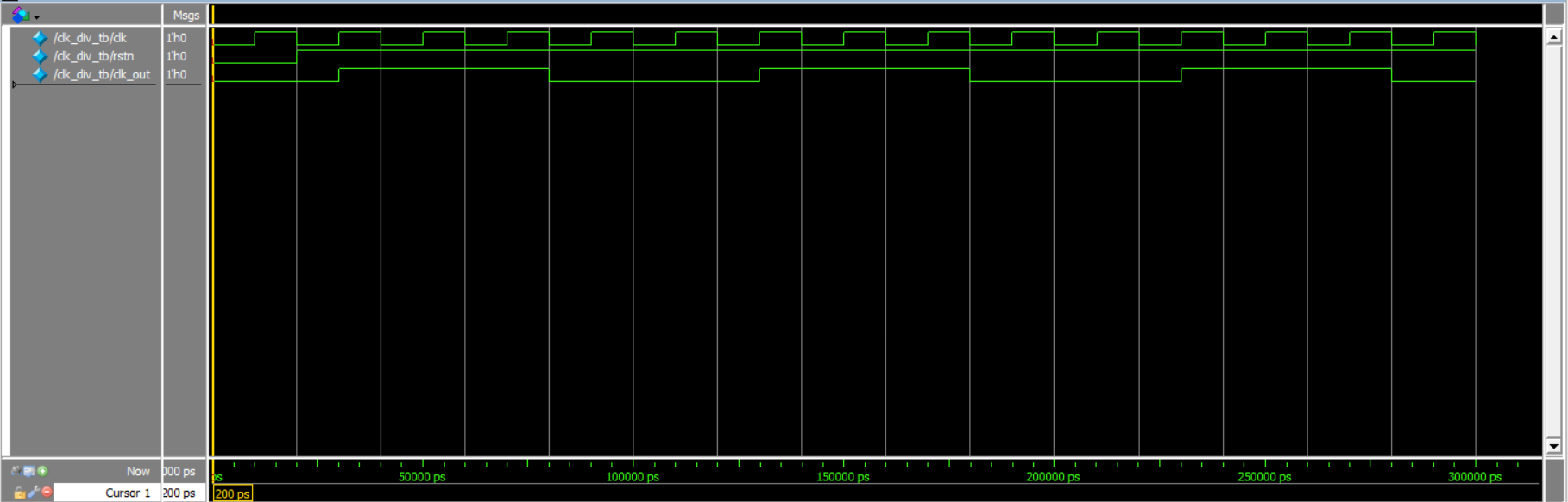

- 仿真验证:

由代码,我们只需要控制生成时钟信号clk和复位信号rstn即可。

initial begin

clk = 0;

forever #10 clk = ~clk;

end

initial begin

rstn=0;

#20 rstn=1;

end

相应地,五倍频的仿真波形结果如下,符合要求。

- 综合结果:

- 总结分析:

①:总结规律->设计实现;

②:优先级:算术运算符>移位运算符,想要先进行移位时,应加括号。

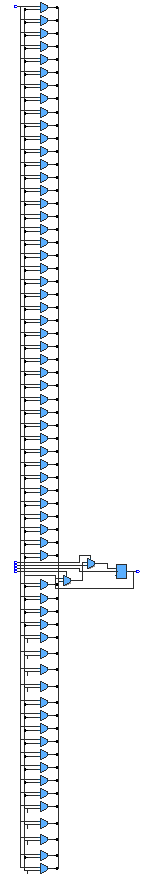

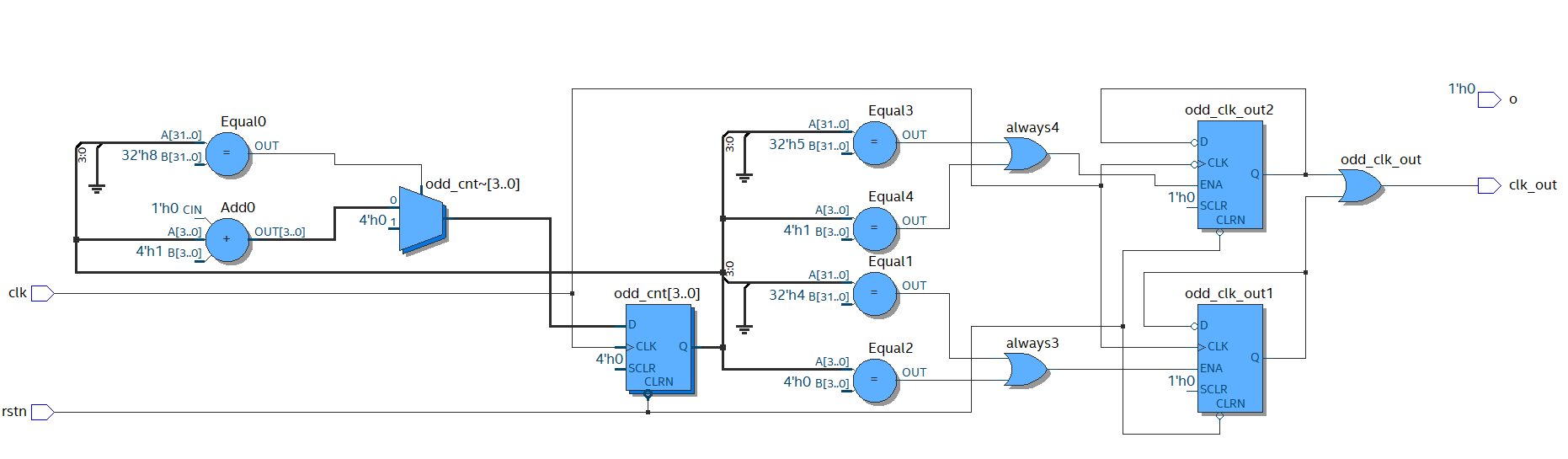

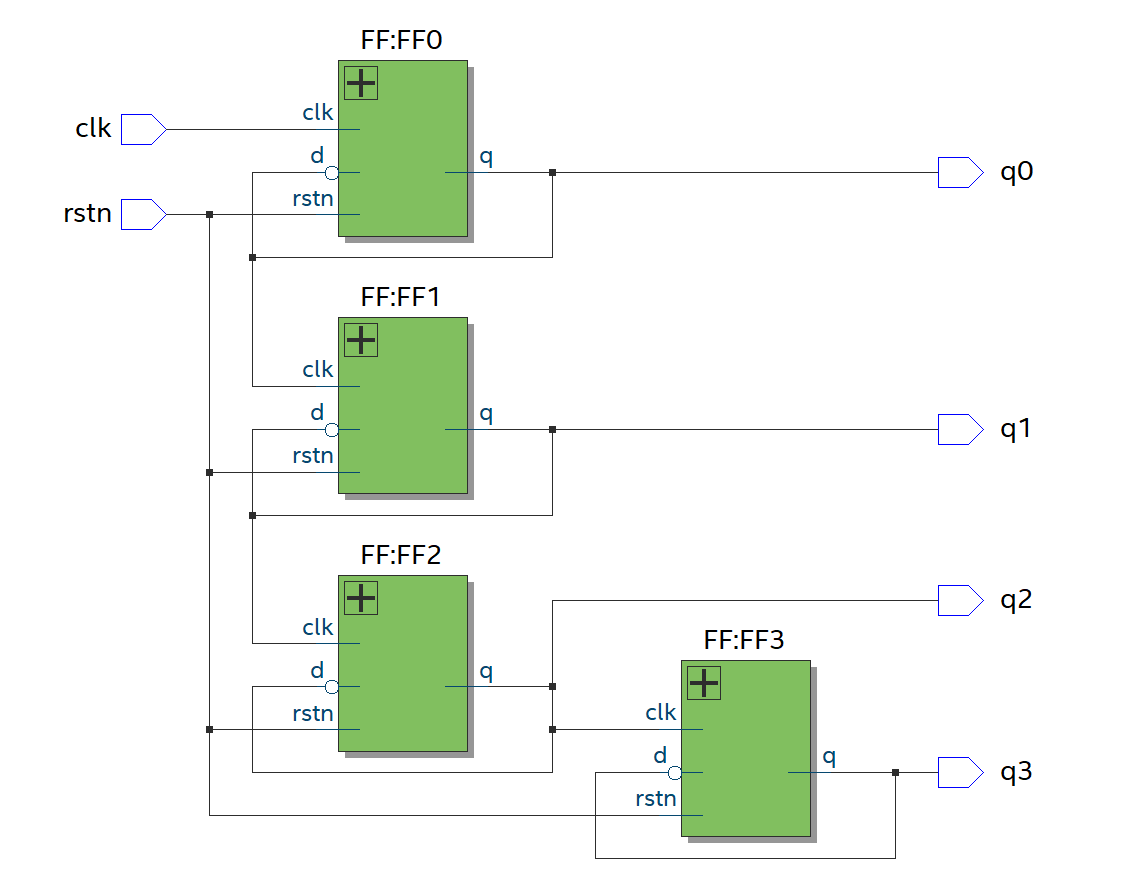

六、异步四位二进制加计数器:

- 功能描述:

每个D触发器的Q非端连接到D端,实现翻转功能。计数时钟clk加至触发器FF0的时钟脉冲输入端,每输入一个计数脉冲,FF0翻转一次。

FF1-FF3都以前一级触发器的Q端作为触发信号,当Q0由1变0时,FF1翻转,其余类推。

设计方案:

①设计基本的D触发器作为FF,例化4次得到功能实现;

②据图连接例化端口。关键代码:

module FF(

input clk,

input rstn,

input d,

output reg q);

always @(negedge clk) begin

if(!rstn) q <= 0;

else q <= d;

end

endmodule

module asyn_counter(

input clk,

input rstn,

output q0,

output q1,

output q2,

output q3);

FF FF0(

.clk(clk),

.rstn(rstn),

.d(~q0),

.q(q0));

FF FF1(

.clk(q0),

.rstn(rstn),

.d(~q1),

.q(q1));

FF FF2(

.clk(q1),

.rstn(rstn),

.d(~q2),

.q(q2));

FF FF3(

.clk(q2),

.rstn(rstn),

.d(~q3),

.q(q3));

endmodule

- 仿真验证:

只需控制生成时钟信号和复位信号

initial begin

clk = 0;

forever #10 clk=~clk;

end

initial begin

rstn=0;

#20 rstn=1;

#100 $stop;

end

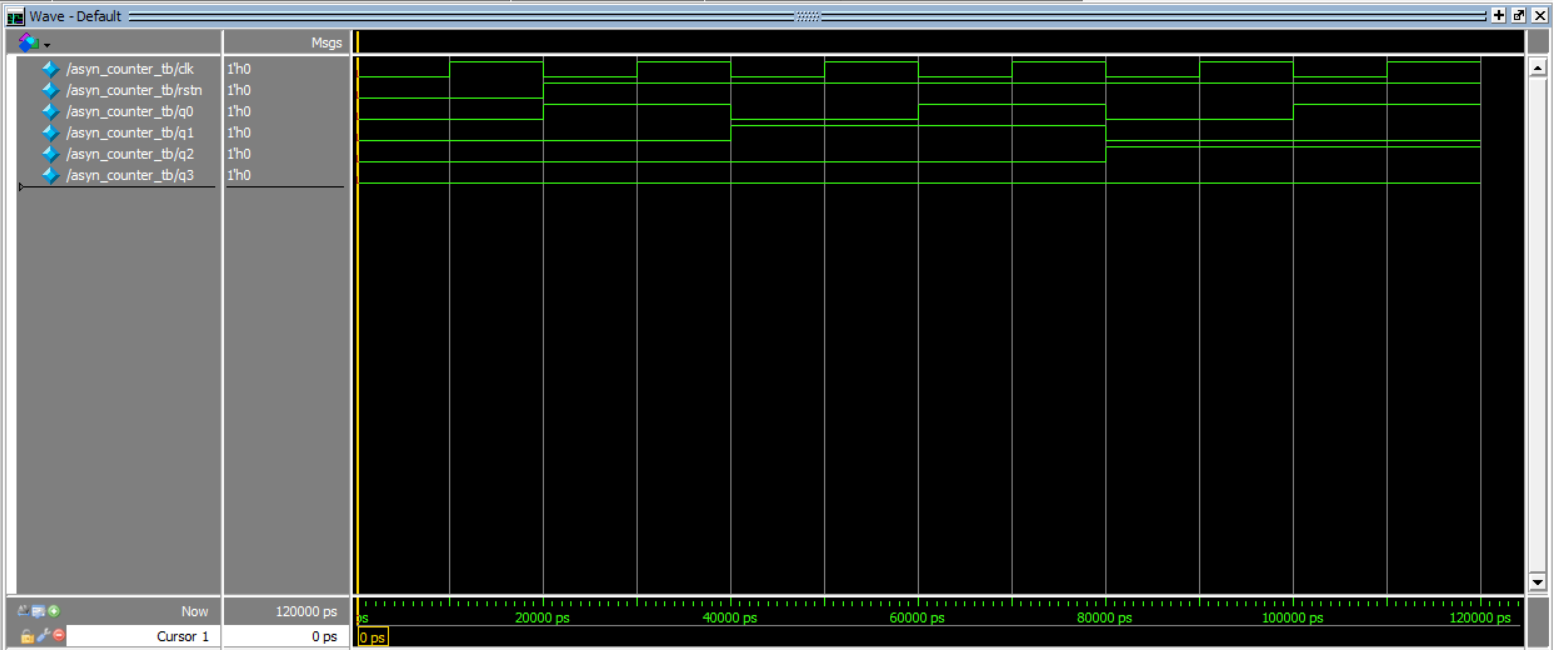

对应波形图如下,正确完成从零开始的下降沿计数。

- 综合结果:

数电第7周周结_by_yc的更多相关文章

- 模电&数电知识整理(不定期更新)

模电总复习之爱课堂题目概念整理 Chapter 1 1) 设室温情况下某二极管的反偏电压绝对值为1V,则当其反偏电压值减少100mV时,反向电流的变化是基本不发生变化. 2) 二极管发生击穿后,在击穿 ...

- 数电课设——琐碎

这几天没有更新过网站了,也没继续开发VellLock了,可是感觉还是没有闲着,一直在跟下面的一些元器件在打交道,当然下面的都是小儿科,英文文档都看得我快吐血了.数电基本属于棺材边上过的我,是各种头大, ...

- java第二周周学习总结

java运算符和循环 java运算符 一.for 语句 for 语句的基本结构如下所示:for(初始化表达式;判断表达式;递增(递减)表达式){ 执行语句; //一段代码} 初始化表达式:初 ...

- web前端笔记整理,从入门到上天,周周更新

由于大前端知识点太多,所以一一做了分类整理,详情可见本人博客 http://www.cnblogs.com/luxiaoyao/ 一.HTML 1.注释 格式:<!-- 注释内容 --> ...

- 数电基础之《OC门》

OC门,又称集电极开路门,Open Collector. 为什么引入OC门?实际使用中,有时需要两个或两个以上与非门的输出端连接在同一条导线上,将这些与非门上的数据(状态电平)用同一条导线输送出去 ...

- FPGA大公司面试笔试数电部分,看看你会多少

1:什么是同步逻辑和异步逻辑?(汉王) 同步逻辑是时钟之间有固定的因果关系.异步逻辑是各时钟之间没有固定的因果关系. 答案应该与上面问题一致 [补充]:同步时序逻辑电路的特点:各触发器的时钟端全部连接 ...

- STM32f103的数电采集电路的DMA设计和使用优化程序

DMA,全称为:Direct Memory Access,即直接存储器访问.DMA传输方式无需CPU直接控制传输,也没有中断处理方式那样保留现场和恢复现场的过程,通过硬件为RAM与I/O设备开辟一条直 ...

- 数电——全减器分析(用74HC138设计提示)

-1=1(即Di=1). Di=(Y1' * Y2' * Y4' * Y7')'可以得到74HC138来表示,(注意:Ai,Bi,Ci-1的各自位权对应A2,A1,A0) Ci同理可得.

- STM32f103的数电采集电路的TIMER定时器的使用与时序控制的程序

STM32 的通用定时器是一个通过可编程预分频器(PSC)驱动的 16 位自动装载计数器(CNT)构成.STM32 的通用定时器可以被用于:测量输入信号的脉冲长度(输入捕获)或者产生输出波形(输出比较 ...

- STM32f103的数电采集电路的双ADC的设计与使用

STM32F103C8T6拥有3个ADC,其独立使用已经在本文的3.1.3里面有详细的介绍,这里主要是介绍双ADC的同时使用,即STM32的同步规则模式使用.在此模式在规则通道组上执行时,外部触发来自 ...

随机推荐

- Elastic:使用ElastAlert发送通知

ElastAlert是一个简单的框架,用于从Elasticsearch中的数据中发出异常,尖峰或其他感兴趣模式的警报.我们可以在地址https://elastalert.readthedocs.io/ ...

- 使用Metricbeat监控zookeeper遇到的问题

1.metricbeat中启动自动加载模块 metricbeat.config.modules: path: ${path.config}/modules.d/*.yml reload.enabled ...

- 启动elasticsearch报错解决

说不定以后会不定期更新该文档 1.提示文件描述符数量太少,修改/etc/security/limits.conf文件,添加. * soft nofile 65537 * hard nofile 655 ...

- 使用Elasticsearch的processors来对csv格式数据进行解析

来源数据是一个csv文件,具体内容如下图所示: 导入数据到es中 有两种办法,第一种是在kibana界面直接上传文件导入 第二种方法是使用filebeat读取文件导入 这里采用第二种办法 配置文件名: ...

- 服务器设置X-Frame-Options Header响应头(Tomcat,服务器,项目)

解决方案(修改tomcat配置文件) 打开Tomcat配置文件(conf\web.xml)搜索 httpHeaderSecurity有两处地方 <!--第一处将注释放开--> <fi ...

- rpm,docker,k8s三种方式安装部署GitLab服务

rpm方式 源地址:https://mirrors.tuna.tsinghua.edu.cn/gitlab-ce/yum/el7/ wget https://mirrors.tuna.tsinghua ...

- 多云容器编排 Karmada-Operator 实践

作者:vivo 互联网服务器团队-Zhang Rong Karmada作为开源的云原生多云容器编排项目,吸引了众多企业共同参与项目开发,并运行于生产环境中.同时多云也逐步成为数据中心建设的基础架构,多 ...

- [题解] Atcoder Beginner Contest ABC 270 G Ex 题解

点我看题 G - Sequence in mod P 稍微观察一下就会发现,进行x次操作后的结果是\(A^xS+(1+\cdots +A^{x-1})B\).如果没有右边那一坨关于B的东西,那我们要求 ...

- 记Windows的一个存在了十多年的bug

bug Windows有一个bug,持续了十多年,从Windows Visita开始(2007年),一直存在,直到Windows11(2021年)才修复(其实也不叫修复,后面我再具体说),而Windo ...

- 一文讲清楚 JVM Safe Point

大家好,我是树哥. 关于 Safe Point 是 JVM 中很关键的一个概念,但我估计有不少同学不是很懂.于是今天跟大家来深入聊聊 Safe Point,希望通过这篇文章能解答这样几个问题: 什么是 ...