边沿检测电路设计verilog

Abstract

边沿检测电路(edge detection circuit)是个常用的基本电路。

Introduction

所谓边沿检测就是对前一个clock状态和目前clock状态的比较,如果是由0变为1,能够检测到上升沿,则称为上升沿检测电路(posedge edge detection circuit),若是由1变为0,能够检测到下降沿,则被称为下降沿检测电路(negedge edge dttection circuit),能够同时检测上升沿与下降沿的电路称为双沿检测电路(double edge detection)。

上升沿检测电路

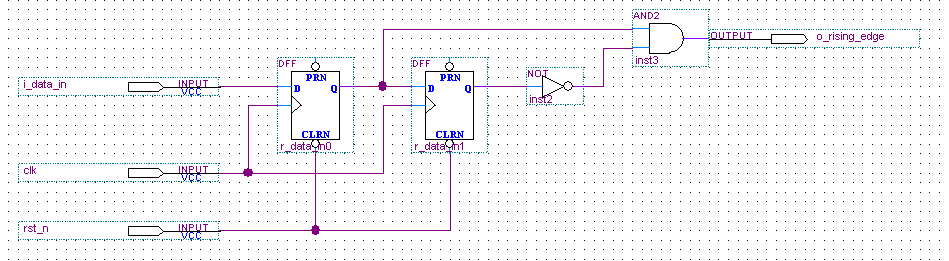

Method 1: 使用两个reg

r_data_in0与r_data_in1为DFF,分别hold住上一个与目前clock的i_data_in,当i_data_in由1变为0时,则

r_data_in0 1 1 1 0 0 0

r_data_in1 1 1 1 0 0 0 //对r_data_in0取反相与

o_rising_edge得到一个时钟周期的高电平。

Posedge detection.v / verilog

1 module posedge_detection (

2 input clk,

3 input rst_n,

4 input i_data_in,

5 output o_rising_edge

6 );

7

8 reg r_data_in0;

9 reg r_data_in1;

10

11 assign o_rising_edge = ~r_data_in0 & r_data_in1;

12

13 always@(posedge clk, negedge rst_n) begin

14 if (!rst_n) begin

15 r_data_in0 <= 0;

16 r_data_in1 <= 0;

17 end

18 else begin

19 r_data_in0 <= r_data_in1;

20 r_data_in1 <= i_data_in;

21 end

22 end

23

24 endmodule

这种写法经过综合后RTL为一个两位的DFF与一个AND。

Methord 2: 使用一个reg

posedge_detection2.v / verilog

module posedge_detection2(

input clk,

input rst_n,

input i_data_in,

output reg o_rising_edge

); reg r_data_in0; always@(posedge clk or negedge rst_n) begin

if(!rst_n)

r_data_in0 <= 0;

else begin

r_data_in0 <= i_data_in;

if({r_data_in0,i_data_in} == 2'b01)

o_rising_edge <= 1;

else

o_rising_edge <= 0; end end

endmodule

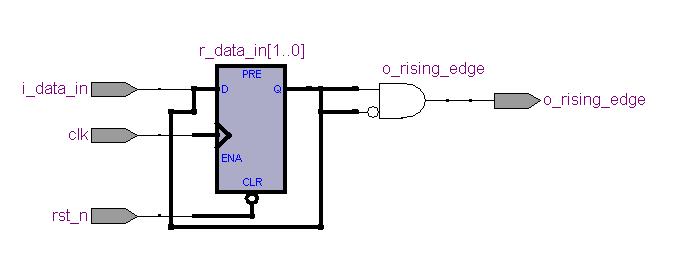

这种写法综合成RTL之后只有一个D-FF和一个Equal,右边的o_rising_edge 的D-FF主要是因为always过程块内的reg。

Vwf仿真图形如下

下降沿检测与上升沿相似,不在叙述

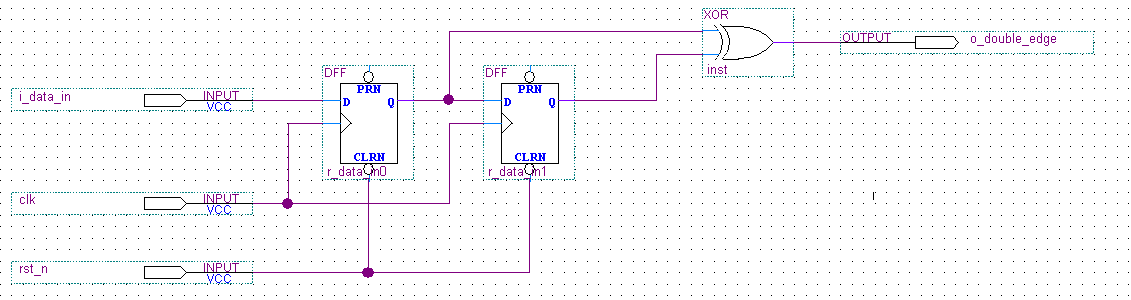

双沿检测电路(double edge detection)

r_data_in0与r_data_in1位reg,分别hold住上一个clock和目前的clock得i_data_in,就是i_data_in由1变0,或者由0变1,也就是r_data_in1为1,r_data_in0为0,或者是r_data_in1为0,r_data_in0为1,因此用异或(xor)连接两个寄存器。

Method1 : 使用两个reg

Double_edge_detection.v/ verilog

module doubleedge_detection (

input clk,

input rst_n,

input i_data_in,

output o_double_edge

); reg r_data_in0;

reg r_data_in1; assign o_double_edge = r_data_in0 ^ r_data_in1; always@(posedge clk, negedge rst_n) begin

if (!rst_n) begin

r_data_in0 <= 0;

r_data_in1 <= 0;

end

else begin

r_data_in0 <= r_data_in1;

r_data_in1 <= i_data_in;

end

end endmodule

Method2 :使用一个reg

Double_edge_detection2.v/verilog

module doubleedge_detection2 (

input clk,

input rst_n,

input i_data_in,

output reg o_double_edge

); reg r_data_in0; always@(posedge clk, negedge rst_n) begin

if (!rst_n)

r_data_in0 <= 0;

else begin

r_data_in0 <= i_data_in; if ({r_data_in0, i_data_in} == 2'b10)

o_double_edge <= 1;

else if ({r_data_in0, i_data_in} == 2'b01)

o_double_edge <= 1;

else

o_double_edge <= 0; // another method

// o_double_edge <= r_data_in0 ^ i_data_in;

end

end endmodule

Conclusion

什么时候使用这种电路呢?当input是非同步信号时,为了要让input与同步的FSM一起处理,必须先经过边沿检测,使之与clock同步,然后才能跟FSM一起运作。

边沿检测电路设计verilog的更多相关文章

- FPGA基础入门篇(四) 边沿检测电路

FPGA基础入门篇(四)--边沿检测电路 一.边沿检测 边沿检测,就是检测输入信号,或者FPGA内部逻辑信号的跳变,即上升沿或者下降沿的检测.在检测到所需要的边沿后产生一个高电平的脉冲.这在FPGA电 ...

- FPGA边沿检测Verilog代码

FPGA边沿检测Verilog代码(上升沿,下降沿,双边沿) 实现思路:用两个一位寄存器直接异或可以实现 代码实现: module edge_detect( input clk, input rs ...

- verilog 之数字电路 边沿检测电路

由代码可知:此边沿检测电路是由两个触发器级联而成,sign_c_r 输出是sign_c_r2的输入.并且有异步复位端没有使能端.最后输出:由触发器的输出取反和直接输出相与.如下的RTL图.

- FPGA学习笔记之格雷码、边沿检测、门控时钟

一.格雷码 格雷码的优点主要是进位时只有一位跳变,误码率低. 1.二进制转格雷码 我们观察下表: 二进制码 格雷码 00 00 01 01 10 11 11 10 二进制码表示为B[],格雷码表示为G ...

- FPGA编程技巧系列之按键边沿检测

抖动的产生: 通常的按键所用开关为机械弹性开关,当机械触点断开.闭合时,由于机械触点的弹性作用,一个按键开关在闭合时不会马上稳定地接通,在断开时也不会一下子断开.因而在闭合及断开的瞬间均伴随有一连串的 ...

- 14FPGA综设之图像边沿检测的sobel算法

连续学习FPGA基础课程接近一个月了,迎来第一个有难度的综合设计,图像的边沿检测算法sobel,用verilog代码实现算法功能. 一设计功能 (一设计要求) (二系统框图) 根据上面的系统,Veri ...

- 边沿检测方法-FPGA入门教程

本节实验主要讲解FPGA开发中边沿检测方法,我们在设计中会经常用到.这个地方大家一定要理解. 1.1.1.原理介绍 学习HDL语言设计与其他语言不一样,HDL语言设计需要考虑更多的信号的电气特性,时序 ...

- FPGA作为从机与STM32进行SPI协议通信---Verilog实现 [转]

一.SPI协议简要介绍 SPI,是英语Serial Peripheral Interface的缩写,顾名思义就是串行外围设备接口.SPI,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用 ...

- 基于basys2用verilog设计多功能数字钟(重写)

话不多说先上图 前言 自从学习FPGA以来,唯一做过的完整系统就是基于basys2得多功能数字表.记得当时做的时候也没少头疼,最后用时间磨出来了一个不是很完整的小系统,当时还是产生了满 ...

随机推荐

- GoF设计模式三作者15年后再谈模式

Erich Gamma, Richard Helm, 和 Ralph Johnson在GoF设计模式发表15年以后,再谈模式,另外一位作者,也是四色原型的发明者Peter已经过世. 提问者:如今有85 ...

- [Android Studio] Android Studio如何提示函数用法

Eclipse有一个很好的功能,就是当你代码调用某个android API时,鼠标移到对应的函数或者方法上,就会自动有一个悬 浮窗提示该函数的说明(所包含的参数含义,该方法功能).迁移到Android ...

- 数字锁相环Octave仿真

clc; clear all; % 仿真数据长度 SimLens = 1000; % 载波信号 Fs = 2400; Ts = 1 / Fs; Fsig = 60; % 随机初相 Delta_Phas ...

- C语言宏定义和宏定义函数

要写好C语言,漂亮的宏定义是非常重要的.宏定义可以帮助我们防止出错,提高代码的可移植性和可读性等. 在软件开发过程中,经常有一些常用或者通用的功能或者代码段,这些功能既可以写成函数,也可以封装成为宏定 ...

- Json转java对象和List集合

public static void main(String[] args) { // 转换对象 String strJson ="{\"basemenu_id\":\& ...

- Python 爬虫 之 阅读呼叫转移(三)

尽管上一篇博客中我们能够连续地阅读章节了,可是.难道每一次看小说都执行一下我们的 Python 程序?连记录看到哪里都不行,每次都是又一次来过?当然不能这样,改! 如今这么多小说阅读器,我们仅仅须要把 ...

- Windows10+Ubuntu双系统安装[

数据备份先别着急,你备份了吗?如果你看到这里,说明你选择了风险最大的一条路,在游戏开始之前,一定要做好数据备份,数据备份,数据备份. 创建磁盘分区 按住Win + X,选择“磁盘管理”: 磁盘管理概览 ...

- Sql从一张表中更改另一张表数据

语法: update table1 set table1.列=table2.列 from table2 where table2.列=table1.列update dbo.PATIENT se ...

- 利用VS2010开发一个跳转页面aspx

在开发项目的过程中,由于要集成Cognos的报表通过URL,但是Cognos报表的本身URL长度过程,那么此时就需要开发一个跳转的页面,下面我们就采用VS2010开发一个跳转的页面Default.as ...

- 使用javascript开发的视差滚动效果的云彩

在线演示 jquery.parallax.js是一款能够帮助你快速开发视差效果的jQuery插件,在这里我们使用它来开发一款漂亮的云朵视差效果. 主要代码: Javascript ........ 阅 ...