vivado设计四:自定义IP核测试

在vivado设计三中:http://blog.chinaaet.com/detail/37177已经建立了vivado工程和封装好了自定义IP核。

那么接下来,我们对这个自定义IP核进行测试了:我们已经回到了主界面。

1. create block design

这部分和vivado设计中:是类似的,就不贴图了,

2. 添加我们自定义的IP核

Add IP,输入led

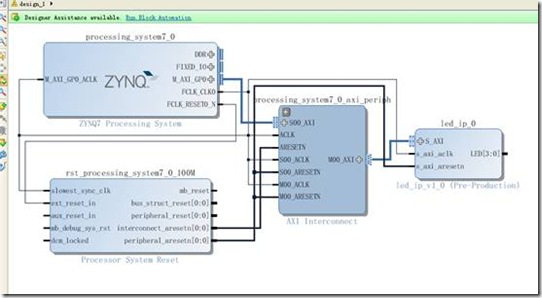

3. 连接

4. 连接后,拖动一下,使得好看一些:

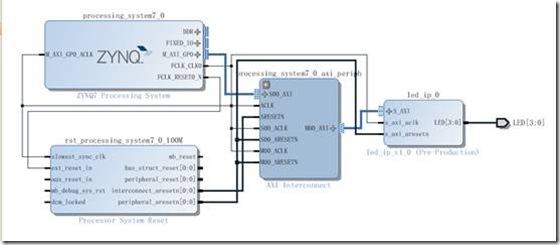

5. 引出LED管脚

6. 选择Tools -> Validate Design,使设计生效,没有error

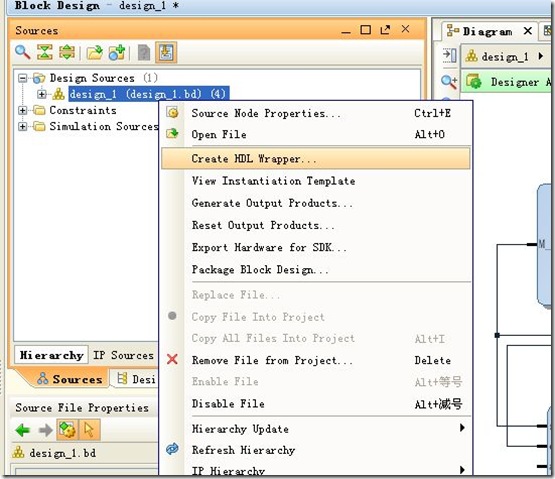

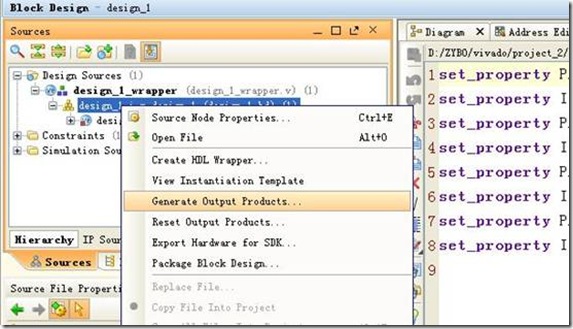

7. 右键design_1.bd, 选择Create HDL Wrapper

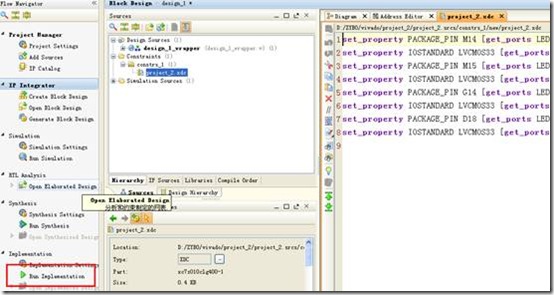

8. 下面添加约束文件,vivado的约束文件的是xdc文件而不是ucf文件

Next,我们create file

9. 编写xdc文件

set_property PACKAGE_PIN M14 [get_ports LED[0]]

set_property IOSTANDARD LVCMOS33 [get_ports LED[0]]

set_property PACKAGE_PIN M15 [get_ports LED[1]]

set_property IOSTANDARD LVCMOS33 [get_ports LED[1]]

set_property PACKAGE_PIN G14 [get_ports LED[2]]

set_property IOSTANDARD LVCMOS33 [get_ports LED[2]]

set_property PACKAGE_PIN D18 [get_ports LED[3]]

set_property IOSTANDARD LVCMOS33 [get_ports LED[3]]

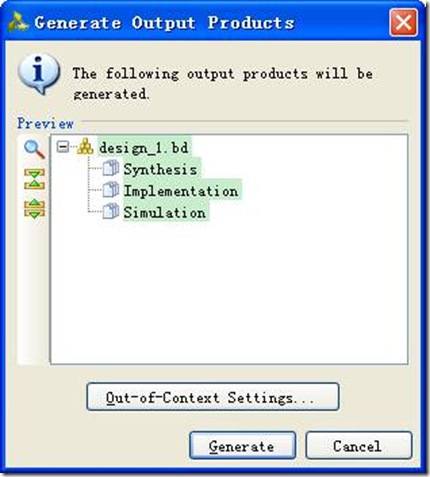

10. 接下来综合

综合通过:

这里cancel,因为下一步我们直接产生bit流文件、

点击generate

11.产生bit流文件,Open Implemented Design

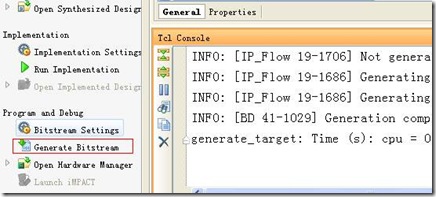

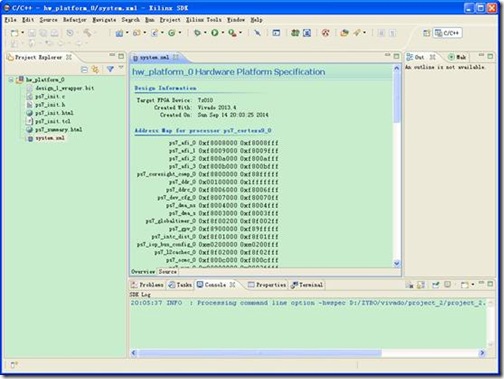

产生bit流文件后,就是愉快的导入SDK了:

File-》Export-》Export Hardware for SDK

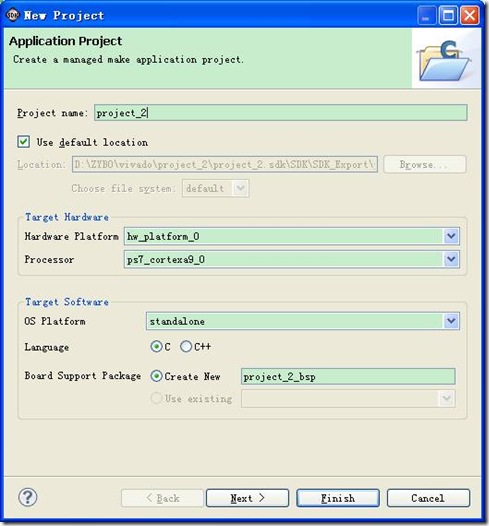

建立Application Project

Next,选择空工程

可以看到:

Tools –》Repositories

设置好路径后,点击ok,退出

右键project_2_bsp,选择Board Support Package Settings,drivers下选择我们的led_ip

这样我的bsp(board support Package)才有led_ip.h这些文件:

编写一个main.c文件

#include "xparameters.h"

#include "xutil.h"

#include "led_ip.h"

//====================================================

int main (void)

{

int i;

xil_printf("-- Start of the Program --\r\n");

while (1)

{

// output dip switches value on LED_ip device

LED_IP_mWriteReg(XPAR_LED_IP_0_S_AXI_BASEADDR, 0, 1);

for (i=0; i<9999999; i++);

LED_IP_mWriteReg(XPAR_LED_IP_0_S_AXI_BASEADDR, 0, 2);

for (i=0; i<9999999; i++);

LED_IP_mWriteReg(XPAR_LED_IP_0_S_AXI_BASEADDR, 0, 4);

for (i=0; i<9999999; i++);

LED_IP_mWriteReg(XPAR_LED_IP_0_S_AXI_BASEADDR, 0, 8);

for (i=0; i<9999999; i++); }

}

LED_IP_mWriteReg在led_ip.h中可以找到。编译生成elf文件。

由于vivado和zybo很久没用,突然连接不上了,测试结果就暂时不能贴上来了。。。有空补上吧。

vivado设计四:自定义IP核测试的更多相关文章

- Vivado 调用自定义IP核

关于Vivado如何创建自定义IP核有大量的参考文章,这里就不多加阐述了,本文目的主要是解决如何在新建工程中引用其它工程已经自定义封装好的IP核,从而实现自定义IP核的灵活复用. 举个例子,我们的目标 ...

- vivado设计三:一步一步生成自己的自定义IP核

开发环境:xp vivado2013.4 基于AXI-Lite的用户自定义IP核设计 这里以用户自定义led_ip为例: 1.建立工程 和设计一过程一样,见vivado设计一http://blog. ...

- AXI-Lite总线及其自定义IP核使用分析总结

ZYNQ的优势在于通过高效的接口总线组成了ARM+FPGA的架构.我认为两者是互为底层的,当进行算法验证时,ARM端现有的硬件控制器和库函数可以很方便地连接外设,而不像FPGA设计那样完全写出接口时序 ...

- Vivado 2017封装自定义IP Core

使用Vivado2017.3自定义IP Core.通常情况下,我们做设计采用模块化设计,对于已经设计好的一部分模块功能,就可以直接拿来调用,IP Core就是这样来的,一般来说我们看不到IP Core ...

- NIOS II 自定义IP核的静态地址对齐和动态地址对齐

如果使用静态地址对齐(每个寄存器在Avalon总线上占4个字节的地址)设置IP使用静态地址对齐的方式为,在hw.tcl脚本里加上一局话:set_interface_property as addres ...

- NIOS II 自定义IP核编写基本框架

关于自定义IP .接口 a.全局信号 时钟(Clk),复位(reset_n) b.avalon mm slave 地址(as_address) 片选(as_chipselect /as_chipsel ...

- vivado中使用ROM IP核

1.在project中选择IP Catalog 在IP Catalog中选择---->Block Memory Generator------>RAMs&ROMs&BRAM ...

- vivado中使用MMCM ip核

1.在project中选择IP Catalog 在IP Catalog中选择FPGA Features and Design----->Clocking------>Clocking Wi ...

- Vivado使用技巧(二):封装自己设计的IP核

由 judyzhong 于 星期五, 09/08/2017 - 14:58 发表 概述 Vivado在设计时可以感觉到一种趋势,它鼓励用IP核的方式进行设计.“IP Integrator”提供了原 ...

随机推荐

- Cargo, Rust’s Package Manager

http://doc.crates.io/ Installing The easiest way to get Cargo is to get the current stable release o ...

- Understanding how SQL Server executes a query

https://www.codeproject.com/Articles/630346/Understanding-how-SQL-Server-executes-a-query https://ww ...

- nodejs第一个练习:用Node.js建HTTP服务器

这是官方的一个例子, 在F盘建立一个tinyphp.js文件,内容: var http = require('http'); http.createServer(function (req, res) ...

- cas协议,以及tomcat搭建cas服务器

1. CAS 简介 1.1. What is CAS ? CAS ( Central Authentication Service ) 是 Yale 大学发起的一个企业级的.开源的项目,旨 ...

- Spring WebSocket入门(二) 转载

本文转载自:http://www.jianshu.com/p/8500ad65eb50 WebSocket前端准备 前端我们需要用到两个js文件:sockjs.js和stomp.js SockJS:S ...

- Postgres间隔大量写IO的解决办法

概述 为了保证数据可靠性,同时还要保证好的读写性能,以及读写的一致性,经过多年的积累,REDO日志,shared buffer等基本成为关系型数据库的标配.postgres也不例外. 为了保证数据的可 ...

- SEO之巴莱多定律

SEO这个词在2007.2008年好像特别的火,尤其在2007年下半年至今,众多SEO爱好者发起了最大的一轮搜索引擎优化研究风暴,甚至最终逼迫百度等大型搜索引擎公司改变算法. SEO,确实能带来一些经 ...

- 推送代码分支时出现:fatal: 'origin' does not appear to be a git repository

关于ubuntu进行提交本地分支到远程库出现问题: 解决方案: 执行如下命令: git remote add origin git@github.com:yourusername/test.git y ...

- JS-产生随机数的几个用法!

<script> function GetRandomNum(Min,Max) { var Range = Max - Min; var Rand = Math.random(); ret ...

- install.Android

It was not possible to complete an automatic installation. This might be due to a problem with your ...