高速PCB设计注意事项

和SERDES应用相关的高速系统PCB设计注意事项如下:

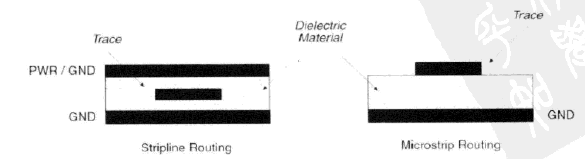

(1)微带(Microstrip)和带状线(Stripline)布线。

微带线是用电介质分隔的参考平面(GND或Vcc)的外层信号层上的布线,这样能使延迟最小;带状线则在两个参考平面(GND或Vcc)之间的内层信号层布线,这样能获得更大的容抗,更易于阻抗控制,使信号更干净,如图所示。

微带线和带状线最佳布线

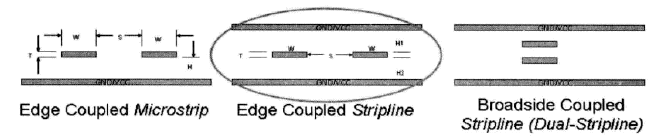

(2)高速差分信号对布线。

高速差分信号对布线常用方法有边沿耦合(Edge Coupled)的微带(顶层)、边沿耦合的带状线(内嵌信号层,适合布高速SERDES差分信号对)和Broadside耦合微带等,如图所示。

高速差分信号对布线

(3)旁路电容 (BypassCapacitor)。

旁路电容是一个串联阻抗非常低的小电容,主要用于滤除高速变换信号中的高频干扰。在FPGA系统中主要应用的旁路电容有3种:高速系统(100MHz~1GHz)常用旁路电容范围有0.01nF到10nF,一般布在距离Vcc 1cm以内;中速系统(十几兆赫兹100MHz),常用旁路电容范围为47nF到100nF钽电容,一般布在Vcc 3cm以内;低速系统(十几兆赫兹以下),常用旁路电容范围为470nF到3300nF电容,在PCB上布局比较自由。

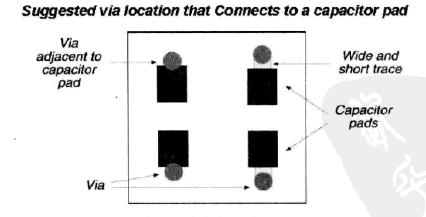

(4)电容最佳布线。

电容布线可遵循下列设计准则,如图所示。

电容最佳布线

使用大尺寸过孔(Via)连接电容引脚焊盘,以减少耦合容抗。

使用短而宽的线连接过孔和电容引脚的焊盘,或者直接将电容引脚的焊盘与过孔相连接。

使用LESR电容(Low Effective Series Resistance,低串联阻抗电容)。

每个GND引脚或过孔应该连接到地平面。

(5)高速系统时钟布线要点。

避免使用锯齿绕线,时钟布线要尽可能笔直。

尽量在单一信号层布线。

尽可能不使用过孔,因为过孔将带来强烈的反射和阻抗不匹配。

尽量在顶层用微带布线,从而避免使用过孔且使信号时延最小。

将地平面尽量布在时钟信号层旁,用以减少噪音和串扰。如果使用内部信号层布时钟线,可以使用两个地平面将时钟信号层夹在中间,以减少噪声和干扰。缩短信号时延。

时钟信号应该正确阻抗匹配。

(6)高速系统耦合与布线注意事项。

注意差分信号的阻抗匹配。

注意差分信号线的宽度,使之可以容忍20%的信号上升或下降时间。

使用合适的连接器,连接器的额定频率应该能满足设计的最高频率。

差分信号对尽量使用edge-couple方式耦合,避免使用broadside-couple方式耦合,使用3S分式法则,避免过耦合或串扰。

(7)高速系统噪声滤波注意事项。

减少电源噪声带来的低频干扰(1KHz以下),在每个电源接入端加屏蔽或者滤波电路。

在每处电源进入PCB的地方加100F的电解电容滤波。

为了减少高频噪音,在每处Vcc和GND处尽可能多地布置去耦合电容。

将Vcc和GND平面平行布置,并用电介质(如FR-4PCB)分隔,在其他层布置旁路电容。

(8)高速系统地弹(Ground Bounce)

尽量在每处Vcc/GND信号对上添加去耦合电容。

在计数器等高速翻转信号的输出端加外部Buffer,以减少驱动能力的要求。

将为使用的用户I/O设置成输出为低电平的输出信号,这相当于虚拟的GND,将这些低电平输出连接到地平面。

对于速度要求不苛刻的输出信号设置为Slow Slew (低上升斜率)的模式。

控制负载容抗。

减少时钟不停翻转的信号,或者将这种信号尽量均匀地分布在芯片的四周。

将翻转频繁的信号尽量靠近芯片的GND引脚布置。

设计同步时序电路时应该尽量避免输出瞬时全部翻转。

将电源和地引岔开布置,这样可以起到在整体上中和电感的作用。

版权所有权归卿萃科技 杭州FPGA事业部,转载请注明出处

作者:杭州卿萃科技ALIFPGA

原文地址:杭州卿萃科技FPGA极客空间 微信公众号

扫描二维码关注杭州卿萃科技FPGA极客空间

高速PCB设计注意事项的更多相关文章

- 一文读懂高速PCB设计跟高频放大电路应用当中的阻抗匹配原理

这一期课程当中,我们会重点介绍高频信号传输当中的阻抗匹配原理以及共基极放大电路在高频应用当中需要注意的问题,你将会初步了解频率与波长的基础知识.信号反射的基本原理.特性阻抗的基本概念以及怎么样为放大电 ...

- 《电容应用分析精粹:从充放电到高速PCB设计》最新勘误表

最新勘误表百度云盘下载 链接: https://pan.baidu.com/s/18yqwnJrCu9oWvFcPiwRWvA 提取码: x3e3 (本勘误表仅包含错误相关部分,不包含对语句的 ...

- 高速PCB设计名词解析

1.吸芯效应 "芯吸效应"是超细纤维特有的性能,是指超细纤维中孔细,接近真空时,近水端纤维管口与水分子接触形成纤维中真空孔隙,此时大气压值超过纤维内部的真空,水就自然压积进入纤维孔 ...

- 高速PCB之EMC设计47则

高速PCB之EMC设计47则 差模电流和共模电流 辐射产生 电流导致辐射,而非电压,静态电荷产生静电场,恒定电流产生磁场,时变电流既产生电场又产生磁场.任何电路中存在共模电流和差模电流,差模信号携带数 ...

- 如何计算PCB设计中的阻抗

关于阻抗的话题已经说了这么多,想必大家对于阻抗控制在pcb layout中的重要性已经有了一定的了解.俗话说的好,工欲善其事,必先利其器.要想板子利索的跑起来,传输线的阻抗计算肯定不能等闲而视之. 在 ...

- 六步教你如何用PADS进行PCB设计?

在使用PADS进行PCB设计的过程中,需要对印制板的设计流程以及相关的注意事项进行重点关注,这样才能更好的为工作组中的设计人员提供系统的设计规范,同时也方便设计人员之间进行相互的交流和检查. 02 设 ...

- 如何用PADS进行PCB设计?这6步就够了

在使用PADS进行PCB设计的过程中,需要对印制板的设计流程以及相关的注意事项进行重点关注,这样才能更好的为工作组中的设计人员提供系统的设计规范,同时也方便设计人员之间进行相互的交流和检查. 02 设 ...

- PCB设计检查表

PCB设计检查表 一.确保PCB网表与原理图描述的网表一致 二.布局大致完成后需检查 外形尺寸 确认外形图是最新的 确认外形图已考虑了禁止布线区.传送边.挡条边.拼板等问题 确认PCB 模板是最新的 ...

- 高端PCB设计相关知识整理

PCB的设计布局布线实际上是一门很复杂而且大部分靠经验来做的学问,很多东西也有点玄乎,但有很多经验性的结论和公式还是可以参考的 保证原创,一天不一定写的完 CH.1 更加严重的电磁干扰 首先基本上微电 ...

随机推荐

- 使用Ant和YUICompressor链接合并压缩你的JS和CSS代码

JS代码和CSS代码在上线前要压缩大家应该都是知道的了.记得之前做项目的时候,最后要交差的时候是找了个网站,将JS代码的文件一个一个地复制,粘贴,复制,粘贴. 当时就在想:TMD有没有好一点的方法,劳 ...

- NumPy切片和索引

NumPy - 切片和索引 ndarray对象的内容可以通过索引或切片来访问和修改,就像 Python 的内置容器对象一样. 如前所述,ndarray对象中的元素遵循基于零的索引. 有三种可用的索引方 ...

- Cacti的基本安装配置

////////////////////cacti///////////////////////////常用的监控软件有:cacti.nagios.zabbix等 cacti 重图形.有数据历史.需要 ...

- 将hibernate.cfg.xml文件都放到spring中时报错

报错如下所示: 私以为是配置文件出现问题了. <?xml version="1.0" encoding="UTF-8"?> <beans xm ...

- python学习笔记(xlwt/xlrd下载安装)

python支持处理Excel 可以使用xlwt xlrd 模块 分别在https://pypi.python.org/pypi/xlwt 和 https://pypi.python.org/pyp ...

- TCP粘包问题及解决方案

① TCP是个流协议,它存在粘包问题 TCP是一个基于字节流的传输服务,"流"意味着TCP所传输的数据是没有边界的.这不同于UDP提供基于消息的传输服务,其传输的数据是有边界的.T ...

- WebService是什么?以及工作原理

WebService 就是一个应用程序,向外界暴露出公开的API使别人其能在WEB对其进行远程调用,具有跨平台和跨语言的等特点,采用Internet的Http协议进行客户端与服务器之间的交互 由XML ...

- 使用MouseWithoutBordersSetup共享鼠标键盘教程

1.下载MouseWithoutBordersSetup软件 2.需要共享鼠标键盘的电脑都要安装[注:这些电脑在同一个局域网] 3.运行软件后,图标上右键—>Settings 注意大红框的地方, ...

- 007——VUE中非常使用的计算属性computed实例

<!DOCTYPE html> <html lang="en"> <head> <meta charset="UTF-8&quo ...

- 【poj1195】Mobile phones(二维树状数组)

题目链接:http://poj.org/problem?id=1195 [题意] 给出一个全0的矩阵,然后一些操作 0 S:初始化矩阵,维数是S*S,值全为0,这个操作只有最开始出现一次 1 X Y ...