MIPS寄存器堆

实验目的

- 熟悉并掌握 MIPS 计算机中寄存器堆的原理和设计方法

- 理解源操作数/目的操作数的概念

实验环境

- Vivado 集成开发环境

MIPS寄存器

- 寄存器R0的值恒为0。

模块接口设计

1个写端口和2个读端口

| 名称 | 宽度 | 方向 | 描述 |

|---|---|---|---|

| clk | 1 | IN | 时钟信号 |

| raddr1 | 5 | IN | 寄存器堆读地址1 |

| rdata1 | 32 | OUT | 寄存器堆返回数据1 |

| raddr2 | 5 | IN | 寄存器堆读地址2 |

| rdata2 | 32 | OUT | 寄存器堆返回数据2 |

| we | 1 | IN | 寄存器堆写使能 |

| waddr | 5 | IN | 寄存器堆写地址 |

| wdata | 32 | IN | 寄存器堆写数据 |

寄存器堆(regfile)实现了32个32位通用寄存器。

- 可以同时进行两个寄存器的读操作和一个寄存器的写操作。

- 写:写使能信号(we)为1时写有效,为0时无效。(write enable)

- 读:读操作可以同时读两个寄存器。

- 同时对同一个寄存器进行读写时,读的数据为旧的数据。

- 读写均为同步。

- 0号寄存器恒为0。

设计代码

`define REG_DATA_WIDTH 31:0

`define REG_NUM 31:0

`define REG_ADDR_WIDTH 4:0

`define REG_ADDR_BIT 5 // 地址线宽

`define REG_DATA_BIT 32 // 数据线宽

module regfile(

input clk,

input [`REG_ADDR_WIDTH] raddr1,

input [`REG_ADDR_WIDTH] raddr2,

input we, // 写使能

input [`REG_ADDR_WIDTH] waddr, // 写地址

input [`REG_DATA_WIDTH] wdata, // 写数据

output reg [`REG_DATA_WIDTH] rdata1,

output reg [`REG_DATA_WIDTH] rdata2

);

// 数组表示寄存器堆

reg [`REG_DATA_WIDTH] mips_regfile [`REG_NUM];

// 读1

always @(posedge clk) begin

if (raddr1 == {`REG_ADDR_BIT{1'b0}}) begin

rdata1 <= {`REG_DATA_BIT{1'b0}};

end

else begin

rdata1 <= mips_regfile[raddr1];

end

end

// 读2

always @(posedge clk) begin

if (raddr2 == {`REG_ADDR_BIT{1'b0}}) begin

rdata2 <= {`REG_DATA_BIT{1'b0}};

end

else begin

rdata2 <= mips_regfile[raddr2];

end

end

// 写

always @(posedge clk) begin

if (we == 1'b1 ) begin

if (waddr == {`REG_ADDR_BIT{1'b0}}) begin

mips_regfile[0] <= {`REG_DATA_BIT{1'b0}};

end

else begin

mips_regfile[waddr] <= wdata;

end

end

else begin

mips_regfile[0] <= {`REG_DATA_BIT{1'b0}};

end

end

endmodule

测试

测试代码

`timescale 1ns / 1ps

`define REG_DATA_WIDTH 31:0

`define REG_NUM 31:0

`define REG_ADDR_WIDTH 4:0

`define REG_ADDR_BIT 5

`define REG_DATA_BIT 32

module sim();

reg clk;

reg [`REG_ADDR_WIDTH] raddr1;

reg [`REG_ADDR_WIDTH] raddr2;

reg we; // 写使能

reg [`REG_ADDR_WIDTH] waddr; // 写地址

reg [`REG_DATA_WIDTH] wdata; // 写数据

wire [`REG_DATA_WIDTH] rdata1;

wire [`REG_DATA_WIDTH] rdata2;

integer i;

regfile u0 (

.clk(clk),

.raddr1(raddr1),

.raddr2(raddr2),

.we(we),

.waddr(waddr),

.wdata(wdata),

.rdata1(rdata1),

.rdata2(rdata2)

);

initial begin

clk = 1;

forever begin

#10 clk = ~clk;

end

end

initial begin

raddr1 = `REG_ADDR_BIT'd0;

raddr2 = `REG_ADDR_BIT'd0;

we = 1'b0;

waddr = `REG_ADDR_BIT'd0;

wdata = `REG_DATA_BIT'd0;

// 写数据

#100

we = 1'b1;

wdata = `REG_DATA_BIT'hFF;

for (i = 0; i < `REG_DATA_BIT; i = i + 1) begin

waddr = i;

wdata = wdata + `REG_DATA_BIT'h100;

#20;

end

// 读数据

we = 1'b0;

for (i = 0; i < `REG_DATA_BIT; i = i + 1) begin

raddr1 = i;

raddr2 = `REG_DATA_BIT - raddr1 - 1;

#20;

end

// 读写相同

// 读到的数据是旧数据

we = 1'b1;

wdata = `REG_DATA_BIT'h100;

for (i = 0; i < `REG_DATA_BIT; i = i + 1) begin

raddr1 = i;

raddr2 = i;

waddr = i;

wdata = wdata - `REG_DATA_BIT'h1;

#20;

end

we = 1'b0;

#100 $finish;

end

endmodule

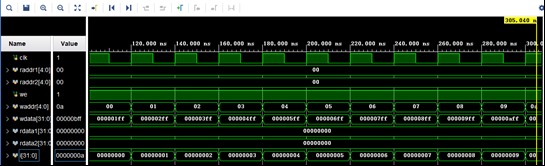

测试波形

写数据:

从 0号寄存器开始到 31号寄存器,分别写入 01ff到 20ff。

读数据:

读地址 1和读地址 2分别读寄存器值,0号寄存器读得值为 0。其余寄存器读值正确。

结果分析

先进行写数据测试,从 0号寄存器开始到 31号寄存器,分别写入 01ff到 20ff。然后进行读数据测试,发现 0号寄存器值为 0,其余寄存器的值符合预期。当同时写和读,即写地址和读地址相同,且写使能时,发现读到的数据为旧数据,而写入的数据不会冲突。

MIPS寄存器堆的更多相关文章

- 自己动手写CPU——寄存器堆、数据存储器(基于FPGA与Verilog)

上一篇写的是基本的设计方案,由于考研复习很忙,不知道下一次什么时候才能打开博客,今天就再写一篇.写一写CPU中涉及到RAM的部件,如寄存器堆.数据存储器等. 大家应该在大一刚接触到计算机的时候就知道R ...

- 【CPU微架构设计】分布式多端口(4写2读)寄存器堆设计

寄存器堆(Register File)是微处理的关键部件之一.寄存器堆往往具有多个读写端口,其中写端口往往与多个处理单元相对应.传统的方法是使用集中式寄存器堆,即一个集中式寄存器堆匹配N个处理单元.随 ...

- 手写一个简易的多周期 MIPS CPU

一点前言 多周期 CPU 相比单周期 CPU 以及流水线 CPU 实现来说其实写起来要麻烦那么一些,但是相对于流水线 CPU 和单周期 CPU 而言,多周期 CPU 除了能提升主频之外似乎并没有什么卵 ...

- MIPS指令 MIPS架构

华中科技大学 - 计算机组成原理 华中科技大学 - 计算机硬件系统设计 Microprocessor without Interlocked Pipleline Stages 无内部互锁流水级的微处理 ...

- MIPS 汇编指令学习

MIPS 寄存器 MIPS comes with 32 general purpose registers named $0. . . $31Registers also have symbolic ...

- uvm_reg_file——寄存器模型(十四)

有了uvm_reg_field, uvm_reg, uvm_block, 也许我们需要跟大的uvm_file,这就是传说中的寄存器堆. // // CLASS: uvm_reg_file // Reg ...

- iot漏洞mips汇编基础

1 基础概念 MIPS(Microprocessor without Interlocked Piped Stages architecture),是一种采取精简指令集(RISC)的处理架构,由MIP ...

- verilog实现16位五级流水线的CPU带Hazard冲突处理

verilog实现16位五级流水线的CPU带Hazard冲突处理 该文是基于博主之前一篇博客http://www.cnblogs.com/wsine/p/4292869.html所增加的Hazard处 ...

- OpenRisc-47-or1200的WB模块分析

引言 “善妖善老,善始善终”,说的是无论什么事情要从有头有尾,别三分钟热度. 对于or1200的流水线来说,MA阶段是最后一个阶段,也是整条流水线的收尾阶段,负责战场的清扫工作.比如,把运算指令的运算 ...

- OpenRisc-44-or1200的pipeline整体分析

引言 我们在前面分析了ORPSoC,or1200_top,和or1200_cpu的整体架构,在最近,我们也分析了or1200的pipeline(流水线)中的两级,EX级和IF级. 但是,我们还没有从宏 ...

随机推荐

- Windows 11 和 Rocky 9 Linux 平台 MySQL 8.0.33 简易安装教程

目录 Windows 平台安装 MySQL Linux 平台 Rocky 9 安装 MySQL binary package rpm package yum 源 source package Wind ...

- 《MS17-010(永恒之蓝)—漏洞复现及防范》

作者: susususuao 免责声明:本文仅供学习研究,严禁从事非法活动,任何后果由使用者本人负责. 一. 什么是永恒之蓝? - 永恒之蓝 永恒之蓝(Eternal Blue)是一种利用Window ...

- HyperPlatform

之前也写过一个vt的框架,但是比较简单,写的比较乱迁移什么的比较麻烦,于是阅读下HyperPlatform的源码学习下. 本文只对主体框架分析. vt的流程大概如下 1:检测是否支持VT. 2:vmx ...

- 写一个Python简单的Socket网络通讯

完成需求 用Python完成一个简单的Socket通讯实例 1. 服务端 用于提供服务 源码: import socket s = socket.socket() # 创建服务器端套接字 # sk.s ...

- @SuppressWarnings注解的使用

Java编译器在编译代码时,会产生一些安全警告信息.如果被@SuppressWarnings注解标记的元素,就可以告诉编译器抑制指定的警告. 先看看@SuppressWarnings注解在Java S ...

- 二分查找法upper版(找大于某个值的最小下标)递归+非递归版

需求:比如说查询一个班级大于60分的最低分等等. 思路与二分法基本相同,只不过是对比的逻辑发生了一些小变化,这里所说的上界就是指大于某个值的最小下标. 当mid < target :说明 tar ...

- 前端vue基于echart实现散点图

前端vue基于echart实现散点图, 下载完整代码请访问uni-app插件市场地址: https://ext.dcloud.net.cn/plugin?id=12866 效果图如下: 参考代码如 ...

- 安装VMware Workstation 16 Pro

下载 官网:https://www.vmware.com/cn/products/workstation-pro/workstation-pro-evaluation.html 注:我是在新毒霸软件管 ...

- 我坚定的认为,这个源码肯定是有 BUG 的!

你好呀,我是歪歪. 上周我不是发了<我试图给你分享一种自适应的负载均衡.>这篇文章嘛,里面一种叫做"自适应负载均衡"的负载均衡策略,核心思路就是从多个服务提供者中随机选 ...

- 前端关于table的设置

表格超长度后加... table{ table-layout:fixed; } td{ overflow:hidden; text-overflow:ellipsis; white-space:now ...