DCDC电路设计之FB引脚布线

该随笔从与非网上搬运,原文:

案例讲解,DCDC电源反馈路径的布线规则

下面为正文内容:

在本文中,将对用来将输出信号反馈给电源ic的FB引脚的布线进行说明。

反馈路径的布线

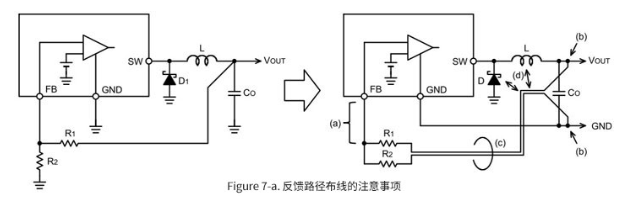

反馈信号的布线在信号布线过程中也需要特别注意。反馈信号如Figure 7-a左侧的电路图所示,输出电压经由布线,由电阻分压,被反馈至电源IC的FB引脚-即误差放大器的输入端,电源IC根据该电压信息执行输出电压的稳定化工作。该反馈路径重要的是,如果实际的输出电压之外的噪声和波动被送往误差放大器,则不仅无法进行准确的输出稳定化,在某些条件下还可能会产生振荡等现象,工作可能会变得不稳定。所以在反馈路径的设计过程中,需要考虑使之能够反馈纯净的信号。

以下是布线的注意事项。如果因反馈信号布线而引发噪声,则可能导致输出电压产生误差,甚至可能导致运行不稳定

- 输入反馈信号的检测输出电压的位置要配置在输出电容器的两端或输出电容器的前面:图中的(b)

- 从输出到电阻分压器的布线要平行且接近,这样不容易产生噪声:图中的(c)

- 布线要远离电感和二极管的开关节点:图中的(d)

- 不在电感或二极管的正下方、与电力系统的布线平行布线(多层PCB板也同样)

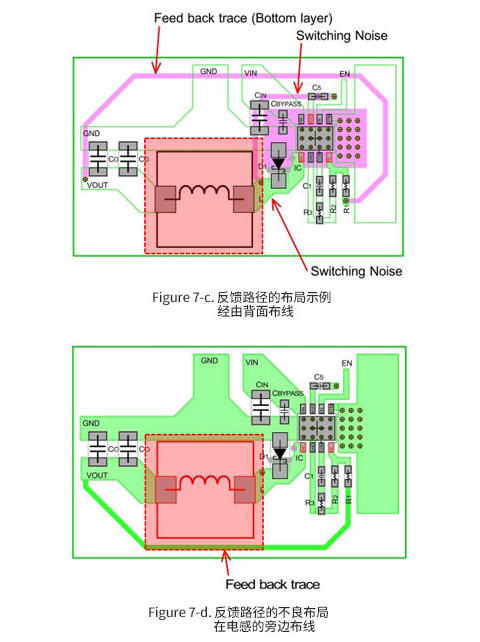

实际进行布线时请注意这些注意事项。Figure 7-c是在反馈路径中使布线经由过孔转移到背面,远离开关节点的布局示例。由PCB板可见,完美地满足上述条件的布线并非易事。尤其是上述条件中未提及的布线的基本要求————“尽量短”。所以,如下面的PCB板所示,一味地延长反馈布线,远离整体电路的做法并不能称之为良策。在这种情况下,还有一种方案是在背面铺设反馈信号的布线。

Figure 7-d是不理想的布线示例。由于反馈路径是与电感平行布局的,所以因电感周边产生的磁场而诱发了反馈路径中的噪声。

实际上,因其他部件的关系,有时无论如何也无法实现理想的配置与布线。在这种情况下,需要好好斟酌理想配置的目的是什么,找出最佳的妥协点。

关键要点: - 输出端的反馈信号线要远离开关节点。如果引发噪声将可能导致误差或误动作。

- 还有一种方法是经由过孔在PCB板背面布线。

DCDC电路设计之FB引脚布线的更多相关文章

- 同步降压DC-DC转换IC——XC9264

设计一个12V转3.3V,输出电流30mA的电源电路,由于项目对转化效率要求较高,所以不能采用低压差线性稳压LDO的方案.经过对比,TOREX的XC9264效率在此转化条件下效率可做到85%以上,比M ...

- [专业名词·硬件] 2、DC\DC、LDO电源稳压基本常识(包含基本原理、高效率模块设计、常见问题、基于nRF51822电源管理模块分析等)·长文

综述先看这里 第一节的1.1简单介绍了DC/DC是什么: 第二节是关于DC/DC的常见的疑问答疑,非常实用: 第三节是针对nRF51822这款芯片电源管理部分的DC/DC.LDO.1.8的详细分析,对 ...

- 【转】从此以后谁也别说我不懂LDO了!

LDO是个很简单的器件,但是我跟客户沟通的过程中,发现客户工程师的技术水平参差不齐,有的工程师只是follow 别人以前的设计,任何原理和设计方法都不懂,希望大家看完这篇文章都能成为LDO 专家. 第 ...

- LT3756/LT3756-1/LT3756-2 - 100VIN、100VOUT LED 控制器

LT3756/LT3756-1/LT3756-2 - 100VIN.100VOUT LED 控制器 特点 3000:1 True Color PWMTM调光 宽输入电压范围:6V至 100V 输出电压 ...

- Spartan6系列之Spartan6系列之芯片时钟资源深入详解

1. 时钟资源概述 时钟设施提供了一系列的低电容.低抖动的互联线,这些互联线非常适合于传输高频信号.最大量减小时钟抖动.这些连线资源可以和DCM.PLL等实现连接. 每一种Spartan-6芯片提 ...

- 硬件设计--DC/DC电源芯片详解

本文参考:http://www.elecfans.com/article/83/116/2018/20180207631874.html https://blog.csdn.net/wangdapao ...

- 24V转5V降压芯片,24V转3.3V的稳压芯片,中文规格书

一般说明PW2312 是一个高频,同步,整流,降压,开关模式转换器内部功率 MOSFET.它提供了一个非常紧凑的解决方案,以实现 1.5A 的峰值输出电流在广泛的输入电源范围内,具有优良的负载和线路调 ...

- PCB布线经验

查看: 3645|回复: 11 [经验] PCB设计经验(1)——布局基本要领 [复制链接] ohahaha 927 TA的帖子 0 TA的资源 纯净的硅(中级) 发消息 加好友 电 ...

- 【小梅哥FPGA进阶学习之旅】基于Altera FPGA 的DDR2+千兆以太网电路设计

DDR2电路设计 在高速大数据的应用中,高速大容量缓存是必不可少的硬件.当前在FPGA系统中使用较为广泛的高速大容量存储器有经典速度较低的单数据速率的SDRAM存储器,以及速度较高的双速率DDR.DD ...

- 《FPGA全程进阶---实战演练》第二十一章 电源常用类型:LDO和 DCDC

高速电路中的电源设计 高速电路中的电源设计大概分为两种,一种是集总式架构,一种是分布式架构.集总式架构就是由一个电源输入,然后生成多种所需要的电压.如图1所示.这种架构会增加多个DC/DC模块,这样成 ...

随机推荐

- flex数据绑定

1 .方法绑定 [Bindable(event="myFlagChanged")] private function isEnabled():String { if (myF ...

- Vue Element-ui Table实现动态新增和删除

达到效果:1.点击添加动态添加一行表格数据 2.点击移除删除一行 templete部分代码 <el-tab-pane label="股东情况"> <el-row& ...

- 【测试平台开发】——02Vue前端框架实战—router路由设计(登录页面)

一.安装vue-cli Mac系统: sudo npm install -g vue-cli 检查是否安装好: vue -V 二.创建新项目 1.打开Vue项目管理器 输入命令: vue ui 但是没 ...

- 【YashanDB知识库】yac修改参数后关闭数据库hang住

[标题]yac修改参数后关闭数据库hang住 [问题分类]性能优化 [关键词]YashanDB, yac, shutdown hang [问题描述]修改yac参数后执行shutdown immedia ...

- 用Python实现阿拉伯数字转换成中国汉字

要将阿拉伯数字转换成中国汉字表示的数字,我们需要一个映射表来转换每个数字,并且处理不同位数的数字(如十.百.千.万等). 1. Python实现阿拉伯数字转换成中国汉字 下面是一个完整的Python代 ...

- MMDetection

安装了mmdetection,想跑一下有几篇文章的工作.总觉得发展很快,一转眼几年时间,好多东西都变了.可再仔细看,感觉又没变啥,还是faster rcnn, ssd, yolo等,这几年变化的主要是 ...

- CSS & JS Effect – Button Hover Bling Bling Effect

效果 原理 一眼看上去, background 有渐变颜色 linear-gradient. 当 hover in 的时候有一束白光, 从右边移动到左边. hover out 则是反过来. 它其实是通 ...

- mongo集群同步数据异常,手动同步节点副本数据

转载请注明出处: 数据同步方案 当副本集节点的复制进程落后太多,以至于主节点覆盖了该节点尚未复制的 oplog 条目时,副本集节点就会变为"陈旧".节点跟不上,就会变得" ...

- Spring —— 注解开发(依赖注入)

自动装配 引用类型 简单类型 加载properties文件

- 音视频入门-8-ffmpeg小实验-v4l2 ubuntu取图、格式转换、编码成H264,ffplay观看

1. getpic_transform_encode2h264.c #include <stdio.h> #include <string.h> #include <st ...