Altera FPGA 开启引脚片上上拉电阻功能

本博文以矩阵键盘实验为例,介绍了如何开启FPGA管脚的片上上拉电阻。

Cyclone IV E FPGA的通用输入输出管脚都支持内部弱上拉电阻,但是时钟输入脚不支持。所以,当需要上拉电阻的信号(如本例中的矩阵键盘Row信号和IIC协议中的SDA、SCL信号)连接到了FPGA的通用输入输出管脚上,在一些要求不高的场合,就可以使用片上上拉电阻来为这些信号设置上拉了。

分配引脚并设置row上拉电阻详细方式

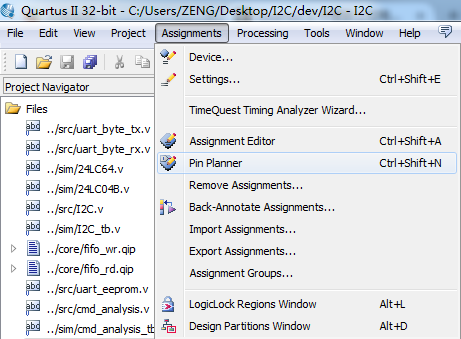

1. 如下图所示,在菜单 Assignments 中选择 Pin Planner,也可以直接点击面板上引脚分配的图标;

(温馨提醒:如图片看不清楚,可以选中图片点击右键,在新窗口中打开该图片以查看高清大图)

图 进入引脚分配界面选项

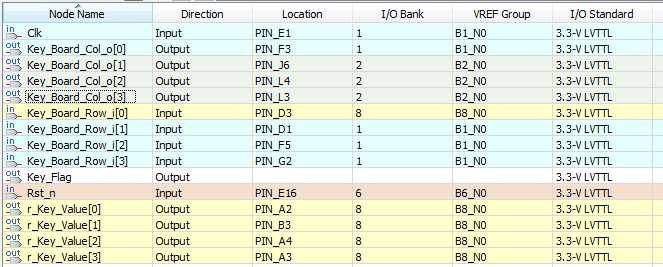

2.进入引脚分配的界面之后,按照上面给出的矩阵键盘与AC620板卡的连接关系以及引脚分配情况,完成引脚分配工作,Starter板卡用户请按照Starter板引脚分配关系分配,并将Key_Value的4位信号分别连接到4位LED上,以方便通过LED的亮灭值确定按键的值。

(温馨提醒:如图片看不清楚,可以选中图片点击右键,在新窗口中打开该图片以查看高清大图)

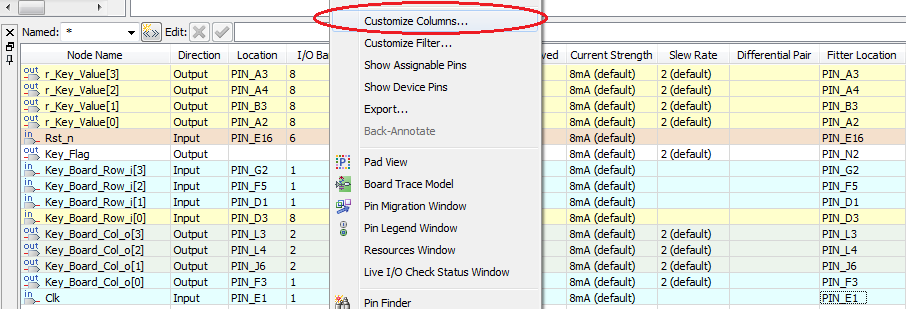

3.在弹出的Pin Planner界面的All Pins区域里任意位置点击鼠标右键,找到 Customize Columns并点击进入,如下图所示;

(温馨提醒:如图片看不清楚,可以选中图片点击右键,在新窗口中打开该图片以查看高清大图)

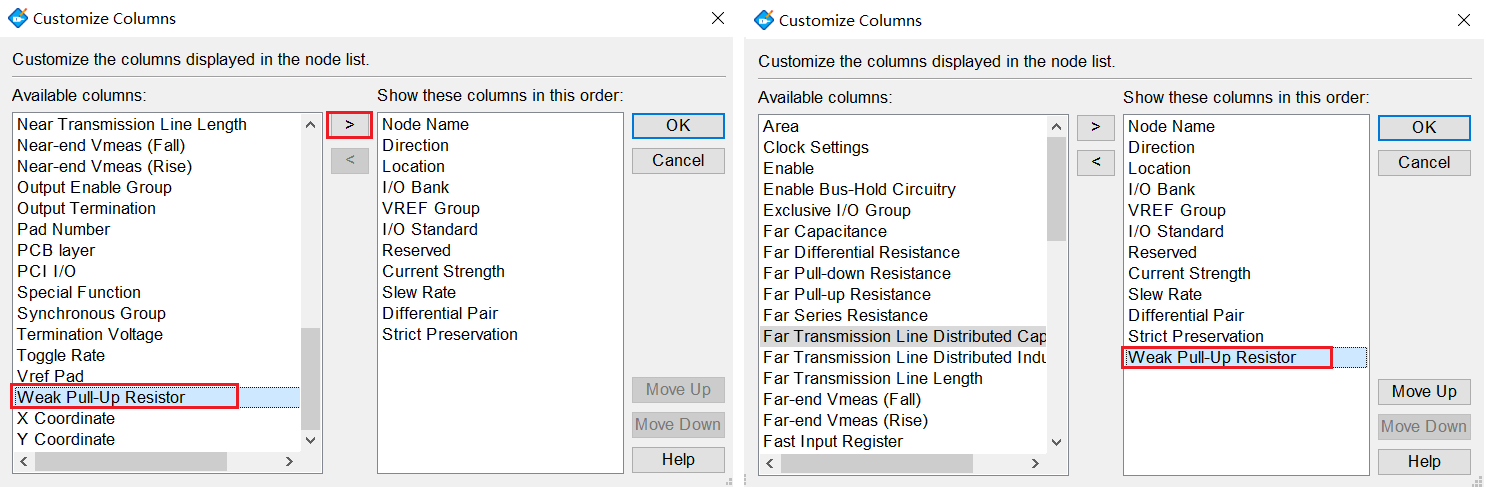

4. 在弹出的Customize Columns对话框的左列表框选择Weak Pull-Up Resistor,如图下图所示,再点击和大于号(>)一样的图标,这样把Weak Pull-Up Resistor添加到右列表框,最后点击OK。

(温馨提醒:如图片看不清楚,可以选中图片点击右键,在新窗口中打开该图片以查看高清大图)

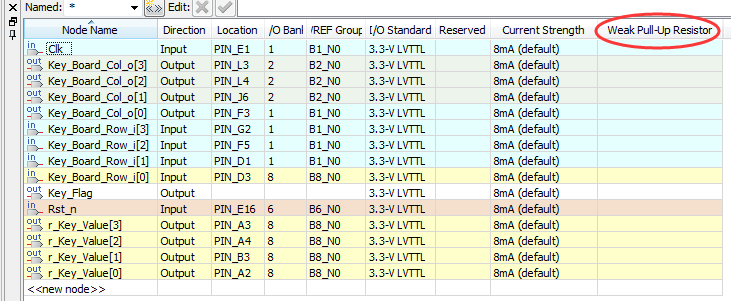

5. 经过步骤4后,在引脚分配界面就会多出一个Weak Pull-Up Resistor列,如下图所示:

(温馨提醒:如图片看不清楚,可以选中图片点击右键,在新窗口中打开该图片以查看高清大图)

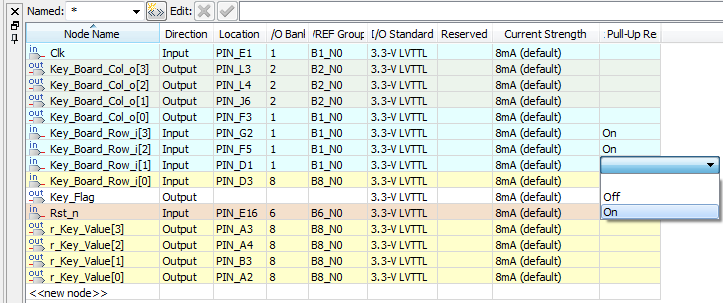

6.再把需要上拉的Row0~Row3对应WeakPull-Up Resistor的位置双击鼠标左键,就会弹出一个Off/On的选项,选上On就可以了。

(温馨提醒:如图片看不清楚,可以选中图片点击右键,在新窗口中打开该图片以查看高清大图)

Altera FPGA 开启引脚片上上拉电阻功能的更多相关文章

- Altera FPGA管脚弱上拉电阻详细设置方法

Altera FPGA管脚弱上拉电阻的软件设置方法 在使用 Altera 的 FPGA 时候, 由于系统需求, 需要在管脚的内部加上上拉电阻. Quartus II 软件中在 Assignment E ...

- 关于51单片机IO引脚的驱动能力与上拉电阻

单片机的引脚,可以用程序来控制,输出高.低电平,这些可算是单片机的输出电压.但是,程序控制不了单片机的输出电流. 单片机的输出电流,很大程度上是取决于引脚上的外接器件. 单片机输出低电平时,将允许外部 ...

- 关于51单片机IO引脚的驱动能力与上拉电阻设计方案

转载自:http://bbs.dianyuan.com/article/20312-2 单片机的引脚,可以用程序来控制,输出高.低电平,这些可算是单片机的输出电压.但是,程序控制不了单片机的输出电流. ...

- Arduino 极速入门系列 - 光控灯(2) - 关于开关,上拉、下拉电阻那些事

接上篇,这次继续讲解光控灯的另外两个组成部分 - 开关和光敏电阻,光控灯里面将会有自锁开关按钮和光敏电阻.这此主要给新玩电子的朋友解释一下开关按钮的做法. 开关按钮的引脚电平读取问题 - 新手专用 我 ...

- 【转】上拉下拉电阻、I/O输出(开漏、推挽等)

作者:BakerZhang 链接:https://www.jianshu.com/p/3ac3a29b0f58来源:简书 感谢! ——————————————————————————————————— ...

- 关于XILINX芯片IO管脚的上拉电阻的疑问

XILINX的每个IO脚都有一个可选的可配上拉电阻功能,现在我在配置文件的UCF里使用了这个上拉电阻:语法如下:NET"I_key_data" LOC = " ...

- Altera FPGA中的pin进一步说明

最近END china上的大神阿昏豆发表了博文 <FPGA研发之道(25)-管脚>,刚好今天拿到了新书<深入理解Altera FPGA应用设计>第一章开篇就讲pin.这里就两者 ...

- 【小梅哥FPGA进阶学习之旅】基于Altera FPGA 的DDR2+千兆以太网电路设计

DDR2电路设计 在高速大数据的应用中,高速大容量缓存是必不可少的硬件.当前在FPGA系统中使用较为广泛的高速大容量存储器有经典速度较低的单数据速率的SDRAM存储器,以及速度较高的双速率DDR.DD ...

- 浅谈用ModelSim+Synplify+Quartus来实现Altera FPGA的仿真

浅谈用ModelSim+Synplify+Quartus来实现Altera FPGA的仿真 工作内容: Mentor公司的ModelSim是业界最优秀的HDL语言仿真软件,它能提供友好的仿真环境,是业 ...

随机推荐

- IP分片(IP Fragment)

为什么要分片 不同的链路类型能够支持的最大传输单元值(MTU: Maxitum Transmission Unit)主要是由相关RFC文档规定的,常见的以太网链路的MTU值为1500,如果需要转发的I ...

- 12步轻松搞定Python装饰器

译者:寒寻 译文:http://www.cnblogs.com/imshome/p/8327438.html 原文:https://dzone.com/articles/understanding-p ...

- All sentinels down, cannot determine where is mymaster master is running...

修改配置的哨兵文件 vim /sentinel.conf 将保护模式关闭

- YUM CentOS 7 64位下mysql5.7安装配置

配置YUM源 在MySQL官网中下载YUM源rpm安装包:http://dev.mysql.com/downloads/repo/yum/ #下载mysql源安装包 # wget http://dev ...

- WPF 出现“调用线程无法访问此对象,因为另一个线程拥有该对象”

引起这种错误多半是由于在非UI线程刷新界面,解决此问题可以使用Dispatcher this.Dispatcher.Invoke(new Action(() => { UpdateUI(stri ...

- Rhythmk 一步一步学 JAVA (20) JAVA enum常用方法

JAVA 枚举定义常用方法: 1.static Enum valueOf(Class enum,String name) 返回指定name的枚举类型 2.Static Enum values[] 返回 ...

- delphi 实体类 JSON 数组

delphi 实体类 与JSON转换,序列化 TJson REST.JSON.pas TJson.JsonToObjectTJson.ObjectToJsonString JsonEncode O ...

- LUA table.sort的问题,数组与表的区别

t = { [] = , [] = , [] = , [] = , } t1 = { , , , , } t2 = { 'a', 'b','d','c', } function cmp(v1, v2) ...

- FM模型

[ 闲聊DNN CTR预估模型] http://www.mamicode.com/info-detail-1465813.html http://blog.csdn.net/bitcarmanlee/ ...

- 无法启动Tomcat, 端口被占用的问题

这个错误是说这几个端口已经有某个应用程序占用了,所以Tomcat就没法启动了. 出现这个问题的原因可能有以下几种: 情况一:点击运行的时候没有选中页面或Servlet窗口的标签 标签被选中时: 标 ...