Verilog HDL 使用规范(一)

本博文参考:《大规模逻辑设计指导书》,对于写出规范的代码,培养良好的代码风格颇有裨益。

wire and register

- 一个reg变量只能在一个always语句中赋值;

这个说明至关重要啊,如果不满足这个,也许仿真的时候没问题,但是综合时候绝对出现,不可以综合。我就犯过多次这个错误。

曾经写过一篇博客,专门说过:Modelsim下进行功能仿真没问题,可是在ISE综合报错,如何解决?

- 向量的有效位定义一般是从大到小。

尽管,标准并没有强制这样,但是这样更规范,读代码更加容易。

表达式(Expressions)

- 用括号表示执行的优先级;

这个比较好理解,尽管Verilog HDL语言有自己的优先级,但是使用括号来表示优先级对读者来说更加清晰,更有意义。

例如:if( (a>b) && (c>d) )......

就比下面这种表达要好:

if( a>b && c>d ),尽管二者的作用一致。

- 用一个函数(function)来代替表达式的多次重复,经常使用的一组描述可以写到一个任务中。

If语句

- 向量比较时,比较的向量要相等;

当比较向量时,Verilog将对 位数小的向量做0扩展以使它们的长度相匹配,它的自动扩展是隐式的。建议采用显示扩展,这个规律同样适用于向量同常量的比较。

例如:

reg [7:0] a;

reg [3:0] b;

...

if( a == {4'b0, b} ) begin

...

end

if( a == 8'b0 ) begin

...

end

- 每一个if都有一个else与之对应;

在做硬件设计时,常要求条件为真时执行一种动作,而条件为假时,执行另一个动作,即使认为条件为假不可能发生,也要有一个else语句,该语句可以为一个空语句。

如果没有else语句可能会使综合出来的逻辑和RTL级的逻辑不同。(这句话什么意思呢?就是如果没有else语句,综合工具可能会综合出来一些你不希望出现的东西,例如会综合出锁存器。本可以不用锁存器的,可偏偏因为没有加else语句,而综合出了锁存器,这不仅对电路的整体性能产生影响,同时也会导致资源浪费。)

例如:

always @(Cond)

begin

if(Cond)

DataOut <= DataIn; //缺少else语句

end

以上语句DataOut会综合成锁存器。

- 应注意if... else if...else 的优先级

上面的语句是有优先级的,if的优先级最高,else if其次,else最后。

- 如果变量在if...else或case 语句中做非完全赋值,则应给变量一个缺省值,即:

V1 = 2'b00; //default

V2 = 2'b00;

v3 = 2'b00;

if(a == b) begin

V1 = 2'b01;

V2 = 2'b10; //V3 is not assigned

end

else if(a == c) begin

V2 = 2'b10;

V3 = 2'b11; //V1 is not assigned

end

else ;

上面的意思就是如果变量在语句中未全部赋值,那么在开始应该给变量一个缺省值,要不然它的值就不可预测了。

case语句

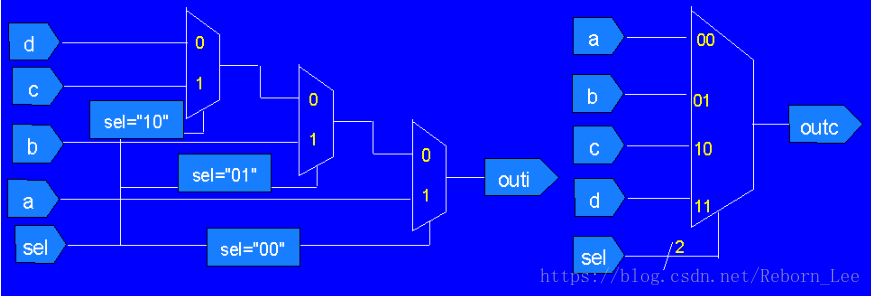

- case通常会综合成一级多路复用器(图的右边部分),而 if...else...则综合成优先编码的串接的多个多路复用器,如图的左边部分。通常使用case语句要比if语句快,优先编码器的结构仅在信号的到达有先后时使用。条件赋值语句也能综合成多路复用器,而case语句仿真要比条件赋值语句快。

- 所有的case 应该有一个default,允许空语句,即:

case

...

default: ;

endcase

这篇博文暂时就到这里,当然需要注意的地方还有很多,我们以后继续更新。更新包括对本博客的修改以及添加,根据实际检验而解释。

例如:下面这句话我就没有说太多的话,因为我还不太清楚。在以往的电路设计中很少使用函数和任务,所以得先学习学习然后实践下。

用一个函数(function)来代替表达式的多次重复,经常使用的一组描述可以写到一个任务中。

Verilog HDL 使用规范(一)的更多相关文章

- Verilog HDL模块的结构

一个设计是由一个个模块(module)构成的.一个模块的设计如下: 1.模块内容是嵌在module 和endmodule两个语句之间.每个模块实现特定的功能,模块可进行层次的嵌套,因此可以将大型的数字 ...

- 关于Verilog HDL的一些技巧、易错、易忘点(不定期更新)

本文记录一些关于Verilog HDL的一些技巧.易错.易忘点等(主要是语法上),一方面是方便自己忘记语法时进行查阅翻看,另一方面是分享给大家,如果有错的话,希望大家能够评论指出. 关键词: ·技巧篇 ...

- 基于Verilog HDL整数乘法器设计与仿真验证

基于Verilog HDL整数乘法器设计与仿真验证 1.预备知识 整数分为短整数,中整数,长整数,本文只涉及到短整数.短整数:占用一个字节空间,8位,其中最高位为符号位(最高位为1表示为负数,最高位为 ...

- 关于初次使用Verilog HDL语言需要懂的基本语法

关于初次使用Verilog HDL语言需要懂的基本语法 1.常量 数字表达式全面的描述方式为:<位宽><进制><数字> 8’b10101100,表示位宽为8的二进制 ...

- FPGA Verilog HDL 系列实例--------步进电机驱动控制

[连载] FPGA Verilog HDL 系列实例 Verilog HDL 之 步进电机驱动控制 步进电机的用途还是非常广泛的,目前打印机,绘图仪,机器人等等设备都以步进电机为动力核心.那么,下面我 ...

- Verilog HDL基础语法讲解之模块代码基本结构

Verilog HDL基础语法讲解之模块代码基本结构 本章主要讲解Verilog基础语法的内容,文章以一个最简单的例子"二选一多路器"来引入一个最简单的Verilog设计文件的 ...

- 写自己的第二级处理器(3)——Verilog HDL行为语句

我们会继续上传新书<自己动手写处理器>(未公布),今天是第七章,我每星期试试4 2.6 Verilog HDL行为语句 2.6.1 过程语句 Verilog定义的模块一般包含有过程语句,过 ...

- 基于Verilog HDL 各种实验

菜鸟做的的小实验链接汇总: 1.基于Verilog HDL 的数字时钟设计 2.乘法器 3.触发器(基本的SR触发器.同步触发器.D触发器) 4.基于Verilog HDL的ADC ...

- 基于Verilog HDL 的数字电压表设计

本次实验是在“基于Verilog HDL的ADC0809CCN数据采样”实验上进一步改进,利用ADC0809采集到的8位数据,进行BCD编码,以供查表方式相加进行显示,本次实验用三位数码管. ADC0 ...

随机推荐

- MVC中使用EF的技巧集(二)——分部验证

1.从数据库生成模型后,再次更新模型时,之前设置的验证规则会丢失. 解决方法:在Models文件夹中新建一个空白类,把它命名为shujuyanzh.cs(类名可以自定),然后把Models中自动生成的 ...

- SQL查询含有%号的字段

select * from EMS_ANNOUNCEMENT where 1=1 and title like '%\%%' escape '\'

- awk 截取某段时间的日志

好久没有截取nginx/haproxy 中 的日志了,竟有点不熟悉了. 记录一下,以免以后忘记. NGINX 日志格式: 192.168.1.26 - - [14/Sep/2017:16:48:42 ...

- 【Win10+eclipse+MinGW+QT安装教程】已有eclipse环境下配置QT插件出错详解

(纪念一下装了一整天濒临绝望的自己[/doge]) (以下所有下载项一律使用32位) step1:下载安装eclipse.适配的jdk.MinGW和QT 1.下载32位eclipse for c++以 ...

- 4、Node.js REPL(交互式解释器)

Node.js REPL(Read Eval Print Loop:交互式解释器) 表示一个电脑的环境,类似 Window 系统的终端或 Unix/Linux shell,我们可以在终端中输入命令,并 ...

- python面向对象之类成员修饰符

类的所有成员分为: 公有成员,在任何地方都能访问 私有成员,只有在类的内部才能访问 私有成员和公有成员的定义不同:私有成员命名时,前两个字符是下划线.(特殊成员除外,例如:__init__.__c ...

- 好用的css库

实现元素各种抖动效果:https://elrumordelaluz.github.io/csshake/

- AngularJs学习笔记--Using $location

原版地址:http://code.angularjs.org/1.0.2/docs/guide/dev_guide.services.$location 一.What does it do? $loc ...

- JAVAWEB之文件的上传下载

文件上传下载 文件上传: 本篇文章使用的文件上传的例子使用的都是原生技术,servelt+jdbc+fileupload插件,这也是笔者的习惯,当接触到某些从未接触过的东西时,总是喜欢用最原始的东西将 ...

- 通过163smtp服务器向各大邮箱发送邮件(SOCKET编程)

package server; import java.io.*; import java.net.*; import java.sql.Time; import java.util.Scanner; ...