基于Verilog HDL整数乘法器设计与仿真验证

基于Verilog HDL整数乘法器设计与仿真验证

1.预备知识

整数分为短整数,中整数,长整数,本文只涉及到短整数。短整数:占用一个字节空间,8位,其中最高位为符号位(最高位为1表示为负数,最高位为0表示为正数),取值范围为-127~127。

负数的表示方法为正值的求反又加1。例如:

8’b0000_0100; //表示值:4,正值求反为:8’b1111_1011;再加1表示为:8’b1111_1100,这样便得到了-4的表示方法为:8’b1111_1100。

同理,负值变成正值的方法为:负值求反又加1。

2.设计思路

怎样判断一个短整数是正值还是负值?

利用一个数的最高位,if(!A[7]) //A是正值;if(B[7]) //B是负值。

在乘法运算中,运算结果的符号可以通过异或运算得到。

|

A值 |

B值 |

结果 |

|

正(0) |

正(0) |

正(0) |

|

正(0) |

负(1) |

负(1) |

|

负(1) |

正(0) |

负(1) |

|

负(1) |

负(1) |

正(0) |

3.乘法器程序设计思路

首先考虑输入信号量,有乘数与被乘数,有一个开始指令(Start_Sig),相当于我们在计算器中输入完计算式子之后,再按下一个“=”号,得到最终的结果。

再考虑输出信号量,有计算结果,同时在计算结果出来后,输出一个运算完成信号(Done_Sig)。

乘法运算的Verilog HDL程序实现:以8X5来举例,其中8是被乘数,5是乘数,表示的含义是5个8相加。乘法运算可以拆分成三个步骤来实现:

在运算前,取得乘数和被乘数的符号位,然后取被乘数和乘数的正值。

isNeg <= Multiplicand[7]^Multiplier[7];

Mcand <= Multiplicand[7]?(~Multiplicand+1’b1):Multiplicand;

Mer <= Multiplier[7]?(~Multiplier+1’b1):Multiplier;

4.基于ModelSim的乘法器仿真验证

本文将详细描述ModelSim的配置过程,方便以后查阅。

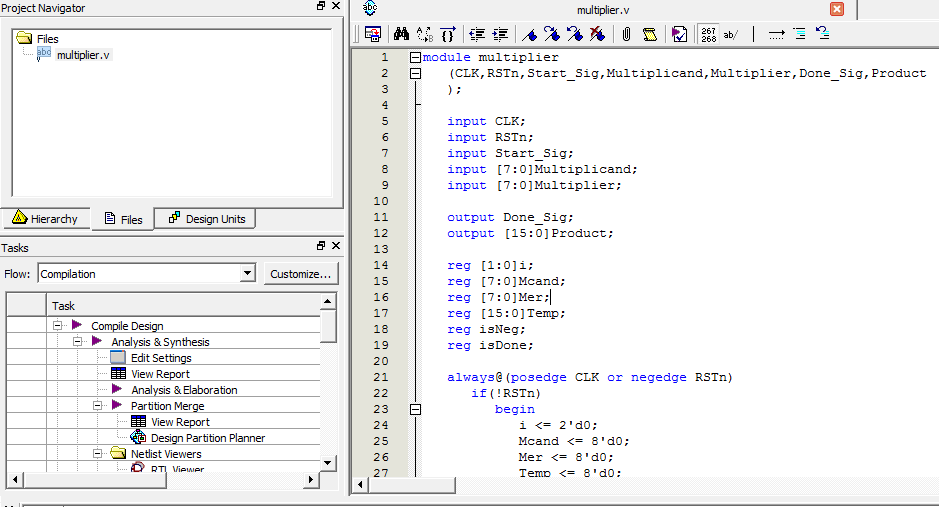

(1)首先建立乘法器的模型,编辑好Verilog HDL程序(学习重点)

(2)关联Quartus与Modelsim-Altera

(2)关联Quartus与Modelsim-Altera

Tools ---- Options ---- EDA Tool Options,选择仿真工具,并添加仿真工具的安装路径。本文选用的Modelsim-Altera。

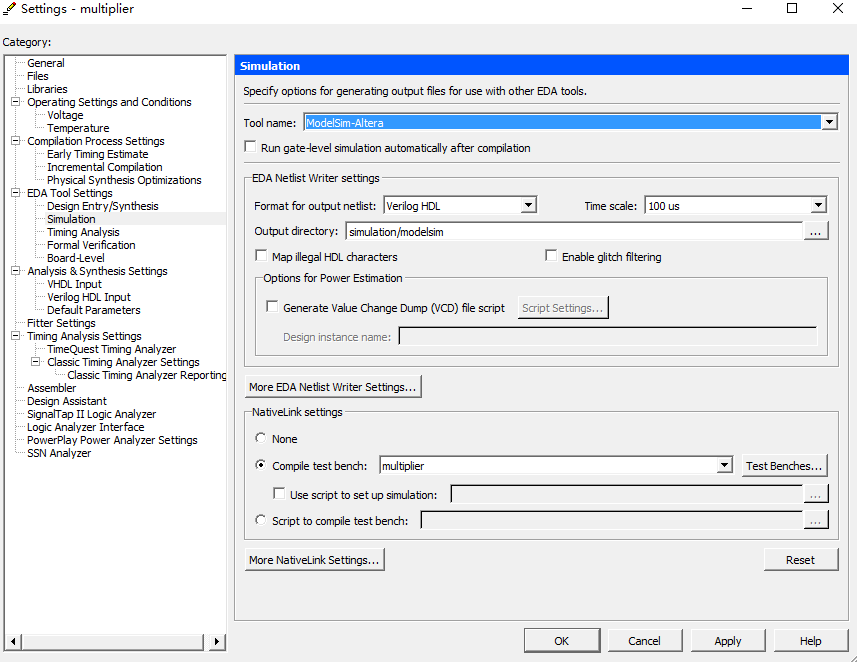

(3)设置仿真工具与需要仿真的文本格式,Time Scale。

Assignments ---- Settings ---- Simulation

Tool name:

Format for output netlist:

Time scale:

Output directory:为默认设置

(4)自动生成Test bench模板

(4)自动生成Test bench模板

Processing ---- Start ---- Start Test Bench Template writer,操作完成后,自动生成Test bench。

打开Test Bench文件,在整个工程文件中会生成一个simulation文件夹,打开,找到里面的“XXX.vt”文件。

(5)编辑Test bench文件

(5)编辑Test bench文件

按照模板文件中的注释,填充相应的测试程序即可。(里面有大学问)

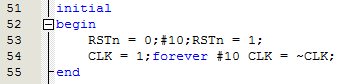

在测试文件中,有一个初始化模块,一般用来初始化时钟信号(CLK)和复位整个电路(RSTn)。

在测试文件中,有一个初始化模块,一般用来初始化时钟信号(CLK)和复位整个电路(RSTn)。

结合“#num”这一参数的变化,与仿真波形的对比,可以得出“#num”是用来设定时间的语句。

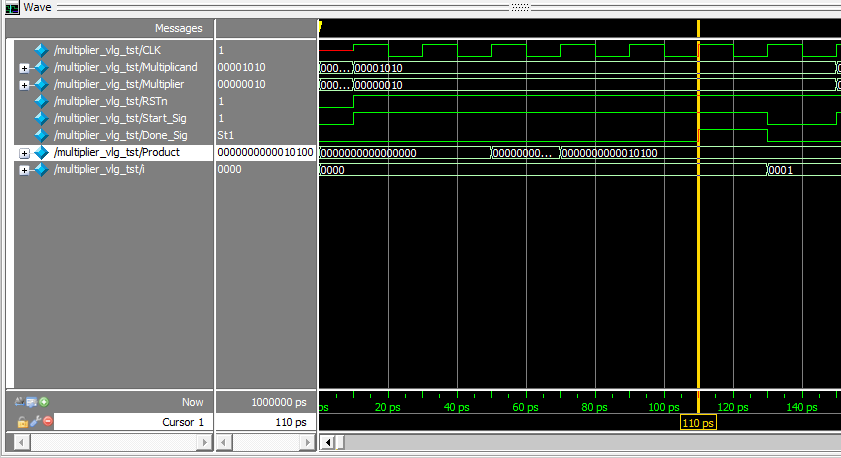

首先谈谈乘法器的工作原理:首先输入乘数与被乘数,当Start_Sig信号置高电平,乘法器开始工作,按照预先写好的模型一步一步运算完后,Done_Sig输出高电平,代表运算完成,得出运算结果输出到Product上。

1.Start_Sig由0跳变到1,乘法器开始运算(相当于计算器上的等号按钮),此时乘数与被乘数输入端口已经有数值,Done_Sig处于st0状态,代表还未完成计算。

2.计算完了乘法的第一步,输出Product上已经有第一步的运算结果了,但是Done_Sig信号还是保持st0状态,代表计算还未结

2.计算完了乘法的第一步,输出Product上已经有第一步的运算结果了,但是Done_Sig信号还是保持st0状态,代表计算还未结

3.第二步运算完成,结果输出到了Product信号线上,但是Done_Sig信号还是保持st0,乘法器还在继续工作。

3.第二步运算完成,结果输出到了Product信号线上,但是Done_Sig信号还是保持st0,乘法器还在继续工作。

4.Done_Sig信号线由st0跳变为st1,并持续一个脉冲周期,此刻表示乘法器完成计算,Product信号线上的数据即为乘法运算的最终结果。

4.Done_Sig信号线由st0跳变为st1,并持续一个脉冲周期,此刻表示乘法器完成计算,Product信号线上的数据即为乘法运算的最终结果。

5.Done_Sig状态又恢复到st0,此刻Start_Sig信号由1变为0,代表乘法器关闭,停止工作,always块语句里面的乘法算法将不再执行。

(6)将编辑好的Test bench文件添加到工程中

Assignments ---- Settings ---- Simulation

选择 Compile test bench选项,单击“...”

New ----

需要填充如下内容:

Test bench name:就是testbench文件的名字,即“.vt”文件的文件名。

Top level module in test bench:就是testbench文件的顶层模块名。

End simulation at:就是仿真最大的时间。

在Test bench files面板中添加Test bench文件,单击“...”找到“.vt”文件的路径,单击add即可,最后单击OK。

单击OK。

单击OK。

单击Apply,单击OK。

单击Apply,单击OK。

(7)开始仿真

Tools ---- Run EDA Simulation Tool ---- EDA RTL Simulation

自动启动ModelSim程序,即可以看到仿真波形。

基于Verilog HDL整数乘法器设计与仿真验证的更多相关文章

- 基于Verilog HDL 的数字电压表设计

本次实验是在“基于Verilog HDL的ADC0809CCN数据采样”实验上进一步改进,利用ADC0809采集到的8位数据,进行BCD编码,以供查表方式相加进行显示,本次实验用三位数码管. ADC0 ...

- 基于Verilog HDL 各种实验

菜鸟做的的小实验链接汇总: 1.基于Verilog HDL 的数字时钟设计 2.乘法器 3.触发器(基本的SR触发器.同步触发器.D触发器) 4.基于Verilog HDL的ADC ...

- 基于Verilog HDL 的数字时钟设计

基于Verilog HDL的数字时钟设计 一.实验内容: 利用FPGA实现数字时钟设计,附带秒表功能及时间设置功能.时间设置由开关S1和S2控制,分别是增和减.开关S3是模式选择:0是正常时钟 ...

- 基于Verilog语言的可维护性设计技术

[注]本文内容主体部分直接翻译参考文献[1]较多内容,因此本文不用于任何商业目的,也不会发表在任何学术刊物上,仅供实验室内部交流和IC设计爱好者交流之用. “曲意而使人喜,不若直节而使人忌:无善而致人 ...

- 基于Verilog HDL的超前进位全加器设计

通常我们所使用的加法器一般是串行进位,将从输入的ci逐位进位地传递到最高位的进位输出co,由于电路是有延迟的,这样的长途旅行是需要时间的,所以为了加快加法器的运算,引入了超前进位全加器. 全加器的两个 ...

- paper:基于verilog HDL 的高速可综合FSM设计

1.寄存器输出型状态机 VS 组合逻辑输出型状态机 2.状态编码方法 这块讲的不好,也比较少. 3.系统设计中模块划分的指导性原则

- 基于Verilog HDL的二进制转BCD码实现

在项目设计中,经常需要显示一些数值,比如温湿度,时间等等.在数字电路中数据都是用二进制的形式存储,要想显示就需要进行转换,对于一个两位的数值,对10取除可以得到其十位的数值,对10取余可以得到个位的数 ...

- 基于Verilog HDL的ADC0809CCN数据采样

本实验是用ADC0809CCN进行数据采样,并用7段数码管进行显示. ADC0809由一个8路模拟开关.一个地址锁存与译码器.一个A/D转换器和一个三态输出锁存器组成.多路开关可选通8个模拟通道,允许 ...

- 基于Verilog的奇数偶数小数分频器设计

今天呢,由泡泡鱼工作室发布的微信公共号“硬件为王”(微信号:king_hardware)正式上线啦,关注有惊喜哦.在这个普天同庆的美好日子里,小编脑洞大开,决定写一首诗赞美一下我们背后伟大的团队,虽然 ...

随机推荐

- GnuRadio Hacking①:使用GnuRadio+SDR破解固定码无线遥控

0×01 信号捕获 在这篇文章中,我们将使用GnuRadio+SDR硬件对某品牌型号的无线跳蛋进行无线重放攻击的演示. 市面上常见的无线遥控工作的频段,通常工作在315Mhz.433Mhz,也有少数的 ...

- REVERSE-Daily(4)-Elfcrackme2

非常坑爹的一道题目,看似非常简单,实则有套路 链接: http://pan.baidu.com/s/1i4XLCd3 密码:9zho 为了练手 我会写出三种解法,包括 结合ascii码值范围的爆破,动 ...

- VC

原子锁 临界区 互斥量 信号量 事件

- sass基础编写流程

这是之前整理在word上的基础流程 sass是Ruby语言开发的一个用于动态编程css文件的框架 所以sass的运行依赖Ruby环境 所以要先安装Ruby 参见详细教程(安装参照慕课网有详细的教程) ...

- 软件工程总结(Final)

又到了学期末了,此时此刻软件工程课业接近尾声了.时间过得太快,仿佛昨天这学期的课才开始, 开学时,老师让我们提出了不少对这门课的问题和疑惑,通过一学期的努力学习,我可以试着解开我自己的疑问了. 下面是 ...

- WPF中未将对象引用设置到对象的实例

前几天,我开始了WPF的基础学习,一上来我就遇到了一个令我头痛的问题,按照书上的例子我写了一段属于自己的代码,一个简单的色调器.满心期待的编译运行,就出现了未将对象引用设置到对象的实例.我在网上查阅了 ...

- web设计中那些因素可能影响网站后期优化

web设计中那些因素可能影响网站后期优化. 1.网站代码的简洁实用性.网站源文件html代码.js代码.css代码等应尽可能的压缩处理.能用jquery-min.js的最好不要用jquery.js:c ...

- 使用if else if else 统计计算

package review20140419;/* * 统计一个班级的成绩,并统计优良中差和不及格同学个数以及求平均分 */public class Test2 { //程序的入口 pub ...

- 最全的CSS浏览器兼容问题

CSS对浏览器的兼容性有时让人很头疼,或许当你了解当中的技巧跟原理,就会觉得也不是难事,从网上收集了IE7,6与Fireofx的兼容性处理方法并整理了一下.对于web2.0的过度,请尽量用xhtml格 ...

- Android应用开发是否应避免使用枚举?

在Android Froyo版本之前, 官方文档Performance Tips中有"Avoid Enums Where You Only Need Ints", 后来该部分被去掉 ...