数字逻辑实践3->EDA技术与Verilog设计

本文属于EDA技术概述类文章

1 EDA技术及其发展

概念

EDA(Electronic Design Automation),指的是以计算机为工作平台,以EDA软件工具为开发环境,以PLD期间或者ASIC专用集成电路为目标期间设计实现电路系统的一种技术。

电子CAD(Computer Aided Design)

狭义的CAD 偏重于“制图”和“建模”(几何模型),广义CAD即覆盖了所有利用计算机进行辅助设计的过程,在这个意义上,CAE和EDA 也可以理解为是CAD的一种;

电子CAE(Computer Aided Engineering)

CAE的核心在于建模--解方程。

CAE 的关注点和出发点在于解决实际工程问题,无论是电磁仿真分析还是流体受力分析等实际问题在工程中都最终被抽象为了一个个数学方程,而得出仿真结果的过程就是求解数学问题的过程。

在CAE领域应用比较多的有有限元分析、有限差分法、加权余量法等求解方程的经典方法,所以CAE的核心在于解方程,这一过程也凝聚了工程师的智慧输出,所以说CAE和工程结合最为紧密,同时门槛极高;

EDA(Electronic Design Automation)

在CAD绘图技术基础上融合了应用电子技术、计算机技术、信息处理技术等实现电子产品的自动设计。

部分参考:三者的区别与CAD软件与常用EDA软件的区别

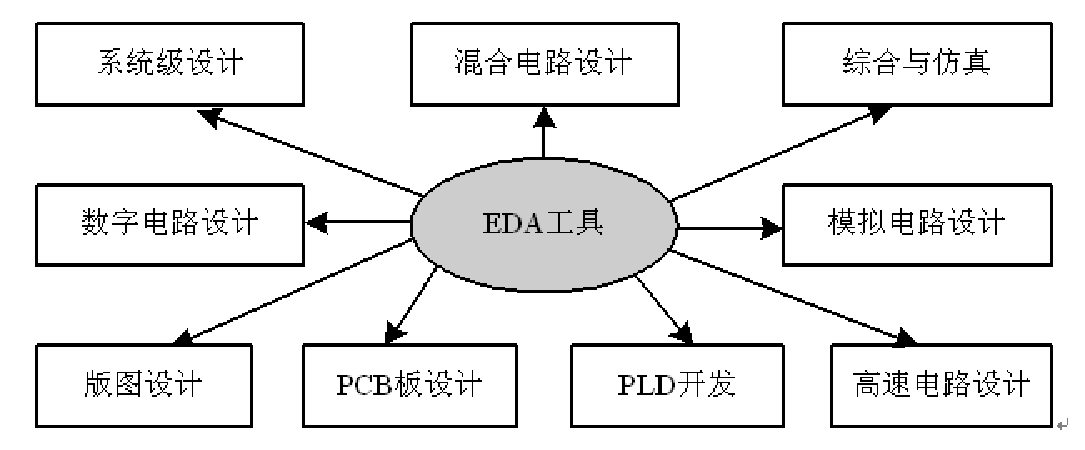

EDA技术的应用范畴

EDA技术的新发展

在FPGA上实现DSP应用

嵌入式处理器软核的成熟

自主知识产权

电子技术领域全方位融入EDA技术

电子领域各学科的界限更加模糊、互为包容

更大规模的FPGA和CPLD器件不断推出

IP核的广泛应用

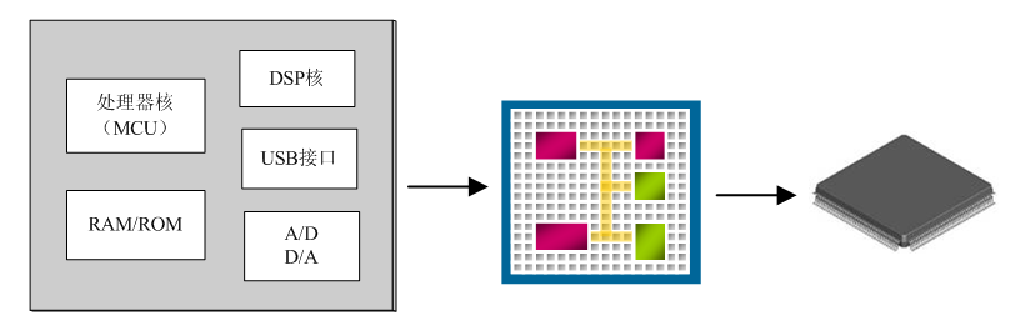

SoC高效低成本设计技术的成熟

现代EDA技术的特征

硬件描述语言设计输入

自顶向下设计方法(即 Top-down设计)

开放性和标准化

高层综合与优化

2 Top-down设计与IP核设计

Top-down设计

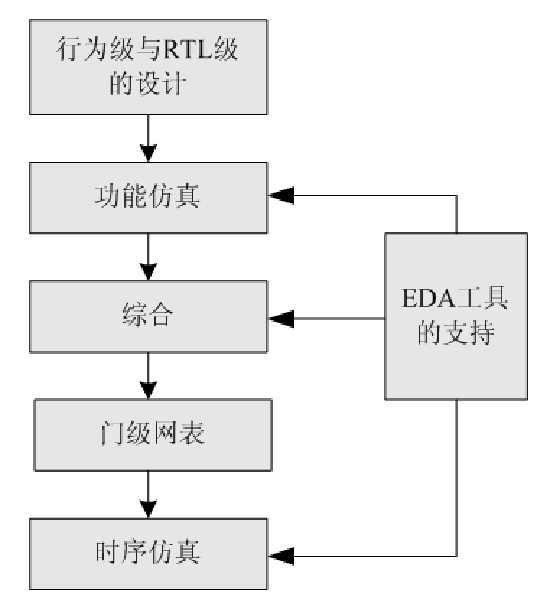

Top-down的设计须经过“设计—验证—修改设计—再验证”的过程,不断反复。

直到结果能够实现所要求的功能,并在速度、功耗、价格和可靠性方面实现较为合理的平衡。

上图就是自顶向下设计;

与之相对的是自底向上的设计(Bottom-up设计)

由设计者调用设计库中的元件(如各种门电路、加法器、计数器等) ,设计组合出满足自己需要的系统缺点:效率低、易出错

好家伙,这不是Altuim Designer的设计风格吗?

IP核设计

一些词

IP(Intellectual Property):

原来的含义是指知识产权、著作权,在IC设计领域指实现某种功能的设计。

IP核(IP模块):

指功能完整,性能指标可靠,已验证的、可重用的电路功能模块。

IP复用(IP reuse)

简称调包

IP核与SOC设计

软IP--用VHDL等硬件描述语言描述的功能块,但是并不涉及用什么具体电路元件实现这些功能。

固IP--完成了综合的功能块。

硬IP--供设计的最终阶段产品:掩膜。

SoC是什么?

SYSTEM ON a CHIP

3 EDA设计的流程

设计输入(Design Entry)

分为两种:

原理图输入(Schematic diagrams )

硬件描述语言(HDL文本 输入)

VHDL

Verilog HDL

硬件描述语言与软件编程语言(C、PASCAL等)有本质的区别

综合(Synthesis)

将较高层次的设计描述自动转化为较低层次描述的过程。

行为综合:从算法表示、行为描述->寄存器传输级(RTL)

逻辑综合:RTL级描述->逻辑门级(包括触发器)

版图综合或结构综合:从逻辑门表示->版图表示,或->PLD器件的配置网表表示

综合器是能够自动实现上述转换的软件工具,是能将原理图或HDL语言描述的电路功能转化为具体电路结构网表的工具

综合 这个概念在硬件里相当于软件的编译。

软件编译器和硬件综合器有所差别:

软件编译(Compiler)->CPU指令/数据代码(01码)

硬件综合(synthesizer)->为ASIC设计提供电路网表文件

适配

适配器也称为结构综合器。

它的功能是将由综合器产生的网表文件配置于指定的目标器件中,并产生最终的可下载文件。

对CPLD器件而言,产生熔丝图文件,即JEDEC文件;

对FPGA器件则产生Bitstream位流数据文件。

仿真

仿真是对所设计电路的功能的验证。

功能仿真(Function Simulation)

时序仿真(Timing Simulation)

编程(下载/配置)

把适配后生成的编程文件装入到PLD器件(可编程逻辑器件)中的过程,或称为下载。

通常将对基于EEPROM工艺的非易失结构PLD器件的下载称为编程(Program);

将基于SRAM工艺结构的PLD器件的下载称为配置(Configure)。

4 常用的EDA软件工具

集成的CPLD/FPGA开发工具

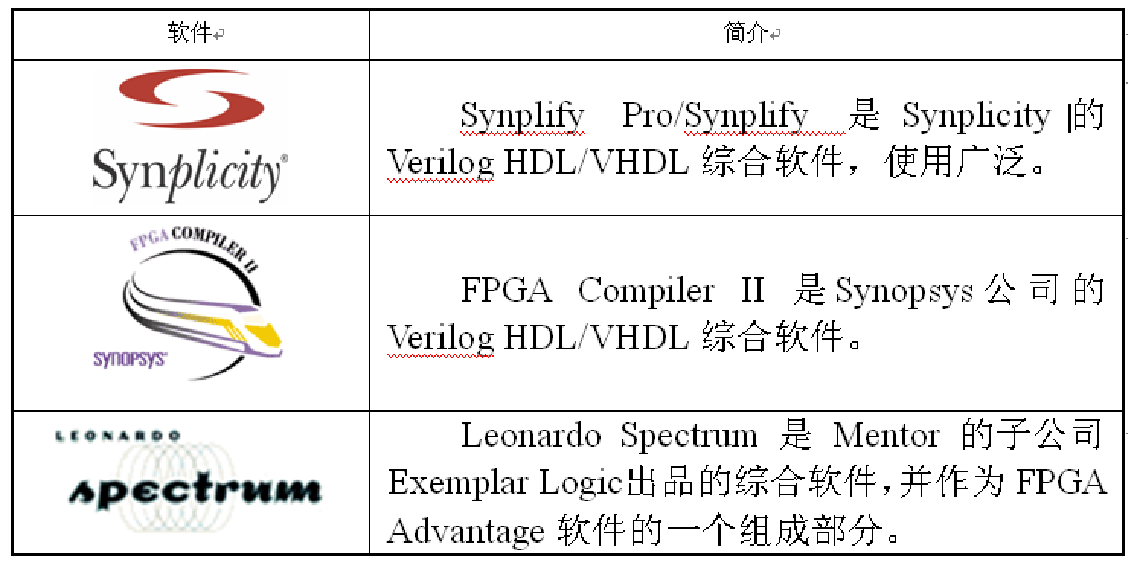

逻辑综合工具

仿真工具

其他设计工具

5 EDA技术的发展趋势

超大规模集成电路的集成度和工艺水平不断提高。

市场对系统的集成度不断提出更高的要求。

高性能的EDA工具,其自动化和智能化程度不断提高,为嵌入式系统设计提供了功能强大的开发环境。

计算机硬件平台性能大幅度提高,为复杂的SoC设计提供了物理基础。

数字逻辑实践3->EDA技术与Verilog设计的更多相关文章

- 数字逻辑实践6-> 从数字逻辑到计算机组成 | 逻辑元件总结与注意事项

00 一些前言 数字逻辑是计算机组成与体系结构的前导课,但是在两者的衔接之间并没有那么流畅,比如对面向硬件电路的设计思路缺乏.这篇总结是在数字逻辑和计组体系结构的衔接阶段进行的. 虽然这篇文是两门课的 ...

- 数字逻辑实践2->Verilog编写规范

来源:数字逻辑与Verilog设计实验课讲解,个人做的笔记与整理. 00 规范的重要性 良好的编程风格有利于减少消耗的硬件资源,提高设计的工作频率 . 提高系统的可移植性和可维护性. 程序的格式化能体 ...

- 数字逻辑实践4->面向硬件电路的设计思维--FPGA设计总述

本文是对实验课上讲解的"面向硬件电路的设计思维"的总结,结合数字逻辑课本,进行提炼和整理. 主要来源是课件与本人整理,部分参考了网络大佬的博客. 本文主要介绍不同于之前软件设计思维 ...

- 数字逻辑实践5->Verilog语法 | wire 与 reg 的选择与特性

问题起因:最初学习数字逻辑设计理论的时候还没有注意到,在实验课上写代码的时候发现了一个问题: 对于源码模块的变量定义,何时定义为reg.何时定义为wire?它们各自又有什么特性和物理意义? 1. wi ...

- EDA技术与ASIC设计和FPGA开发有什么关系?FPGA在ASIC设计中有什么用途?

利用EDA技术进行电子系统设计的最后目标是完成专用集成电路ASIC的设计和实现:FPGA和CPLD是实现这一途径的主流器件.FPGA和CPLD通常也被称为可编程专用IC,或可编程ASIC.FPGA和C ...

- 数字逻辑与EDA设计

目录 第一章 数字逻辑基础 1.1数制与码制★★★ 数制 码制 1.2基本及常用的逻辑运算★★ 1.2逻辑函数表示方法★★ 1.3逻辑函数的化简★★★ 1.4常用74HC系列门电路芯片★ 第二章 组合 ...

- FPGA学习笔记(三)—— 数字逻辑设计基础(抽象的艺术)

FPGA设计的是数字逻辑,在开始用HDL设计之前,需要先了解一下基本的数字逻辑设计-- 一门抽象的艺术. 现实世界是一个模拟的世界,有很多模拟量,比如温度,声音······都是模拟信号,通过对模拟信号 ...

- 高速数字逻辑电平(8)之LVDS差分信号深度详解

原文地址点击这里: LVDS(Low-Voltage Differential Signaling ,低电压差分信号)是美国国家半导体(National Semiconductor, NS,现TI)于 ...

- MSF MS11-050/10-087/Adobe攻击实践及内存保护技术

MSF MS11-050/10-087/Adobe攻击实践及内存保护技术 内存攻击指的是攻击者利用软件安全漏洞,构造恶意输入导致软件在处理输入数据时出现非预期错误,将输入数据写入内存中的某些特定敏感位 ...

随机推荐

- 从零入门 Serverless | Serverless Kubernetes 应用部署及扩缩容

作者 | 邓青琳(轻零) 阿里云技术专家 导读:本文分为三个部分,首先给大家演示 Serverless Kubernetes 集群的创建和业务应用的部署,其次介绍 Serverless Kuberne ...

- Google Style Guides

Google Style Guides Google Style Guides Google 开源项目风格指南 (zh-google-styleguide.readthedocs.io)

- Golang通脉之基础入门

为什么要学 Go 性能优越感:Go 极其地快,其性能与 Java 或 C++相似.在使用中,Go 一般比 Python 要快 30 倍: 序列化/去序列化.排序和聚合中表现优异: 开发者效率较高:多种 ...

- javascript-原生-闭包

1.变量的作用域 前提:这里只全部都通过var创建的变量或对象 1.全局变量:函数外创建变量 var x=10; function test(){ alert("全局变量在test函数中&q ...

- HttpRunner3.X - 实现参数化驱动

一.前言 HttpRunner3.X支持三种方式的参数化,参数名称的定义分为两种情况: 独立参数单独进行定义: 多个参数具有关联性的参数需要将其定义在一起,采用短横线(-)进行连接. 数据源指定支持三 ...

- 【UE4 插件】UnrealEnginePython 源码版编译、项目打包注意事项

源码下载 git clone git clone https://github.com/20tab/UnrealEnginePython 直接下载zip https://github.com/20ta ...

- 对mongo文档的增删改操作

在mongo db 中增加.删除.修改文档有好多方法,这里简单记录一下我所知道的一些方法. 前置条件: 1.创建study数据库 use study; 2.创建persons集合,当第一次向pers ...

- Java版流媒体编解码和图像处理(JavaCPP+FFmpeg)

欢迎访问我的GitHub https://github.com/zq2599/blog_demos 内容:所有原创文章分类汇总及配套源码,涉及Java.Docker.Kubernetes.DevOPS ...

- 无网络下,配置yum本地源

1. 新建一个没有iso镜像文件的虚拟机: 2. 本地上传一个镜像文件(CentOS7的镜像),到虚拟机已创建的目录: 例如:上传一个镜像文件CentOS-7-x86_64-Everything-17 ...

- 2021.8.24考试总结[NOIP47]

T1 prime 发现只需筛小于等于$mid(\sqrt r,k)$的质数,之后用这些质数筛掉区间内不合法的数即可. $code:$ 1 #include<bits/stdc++.h> 2 ...