FPGA 日积月累

Nios II 13.1中,使用Qsys生成的cpu中断号默认为-1,因此中断无法注册。解决方法:手动修改中断模块的tcl文件如下:

add_interface interrupt_sender interrupt end

set_interface_property interrupt_sender associatedAddressablePoint "avalon_slave "

set_interface_property interrupt_sender associatedClock clock

set_interface_property interrupt_sender associatedReset reset

set_interface_property interrupt_sender bridgedReceiverOffset ""

set_interface_property interrupt_sender bridgesToReceiver ""

set_interface_property interrupt_sender ENABLED true

set_interface_property interrupt_sender EXPORT_OF ""

set_interface_property interrupt_sender PORT_NAME_MAP ""

set_interface_property interrupt_sender CMSIS_SVD_VARIABLES ""

之后重新生成CPU即可

1. Quartus 中 Modelsim-Altera 设置的问题

在Quartus II 13.1中, 需要选定好可执行程序的位置,要注意描述的是路径!而非程序

设置结果默认D:\altera\13.1\modelsim_ase\win32aloem,需要在最后加斜线,D:\altera\13.1\modelsim_ase\win32aloem\ 如果最后的“\”没有的话系统无法运行。

2 Modelsim-Altera 仿真过程中无法读取RAM出事话文件*.hex或者*.mif

需要把初始化文件和仿真文件放在同一个路径下。

3. Quartus 远程登录

在lisence里面的网卡后面加上几个字母TS_OK即可

如下

FEATURE quartus alterad 2035.12 permanent uncounted 295142B536B3 \

HOSTID=002618e3e3b6 TS_OK SIGN="0C8D 31B5 AD64 E1C4 C6F9 1540 5072 \

C53D 386C 7A5E 09F0 6FE0 EBAB A42C C139 015B 44B1 D3E6 8F4B \

CD45 FAFF B30C 77BE FA54 955D 022F 0663 87C2 26B0 7305"

4. 网表文件的生成

4.1、基本概念

QuartusII的qxp文件为QuartusII Exported Partition,用于创建综合或者PAR之后的网表文件。

QuartusII的vqm文件为verilog quartusII mapping,只能保存综合后,PAR前的综合结果。

4.2、qxp文件生成

1. 在quartusII的Project Navigator中选中欲创建qxp的module文件,右击,选择“Design Partition > Set as Design Partition”。

2. 综合整个工程,想出PAR后的qxp就需要编译整个工程。

3. 点击菜单“Process”,选择“Start > Start Partition Merge”,以创建完整的module网表。

4. 点击菜单“Project”,选择“Export Design Partition”。

5. 在弹出窗口中选择想要的层次和网表选项,即可导出qxp文件。

注:使用时,仍需右击选择“Set as Design Partition”,否则,有时候会出错,只是有时候而已哦。

通过RTL查看器看到的qxp模块是空的,但PAR后即可看到里面的东东了。

4.3、vqm文件生成

1. 创建以相应module为顶层的工程。

2. 点击菜单“Process”,选择“Start > Start VQM Writer”,即可得到vqm文件。

注:有的器件不支持vqm哦,此时只能用qxp了。

5. WARNING: Couldn't compute FAST_CWD pointer. Please report this problem to the public mailing list cygwin@cygwin.com"

解决方法:Updating Cygwin for Quartus II 13.1 on Windows 8.1

There is a compatibility issue that causes old versions of Cygwin to fail to run on Windows 8.1. This affects all of Altera’s tools that use Cygwin, such as Altera Monitor Program and Nios II EDS. To solve this issue, the Cygwin that is installed with Quartus II must be updated as follows:

- Download the patch at ftp://ftp.altera.com/up/pub/Cygwin_Patch/cygwin_patch.zip

- Extract the contents of cygwin_patch.zip to your Quartus II install directory, overwriting existing files. Both 32-bit and 64-bit versions of Cygwin are included in the zip file; extract both of these versions to your Quartus II install folder. The default path to the Quartus II install folder is “C:\altera\13.1\quartus”.

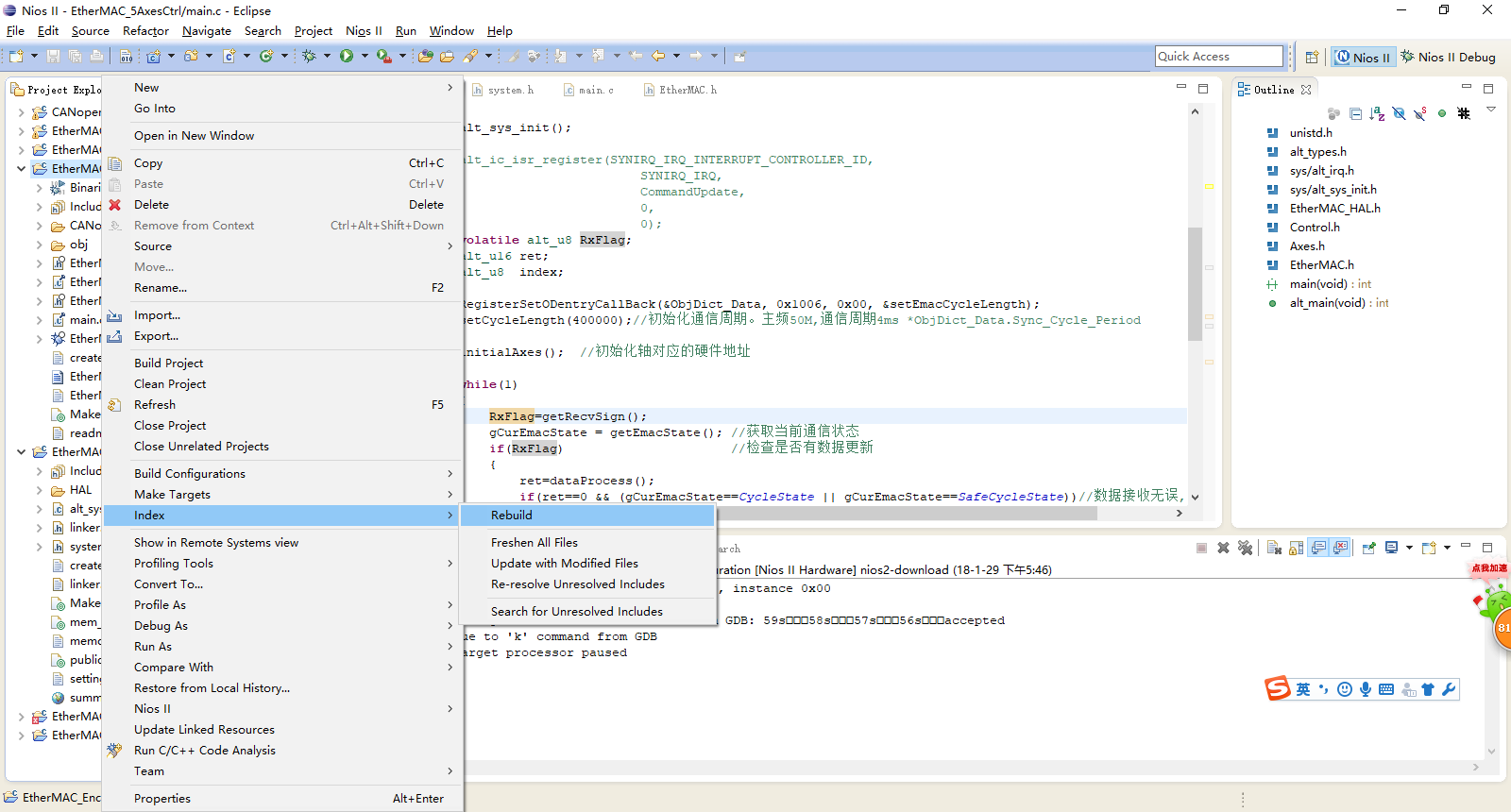

6. NIOS II EDS中出现TYPE 'XXXX_BASE' COULD NOT BE RESOLVED;不识别“system.h”“io.h”等系统头文件(只是错误警告,实际不影响编译和执行)

选中project——右键——Index——rebuild(此方案不行只能重新建立工程)

FPGA 日积月累的更多相关文章

- FPGA的“可编程”使你迷惑吗?

http://www.alteraforum.com.cn/showtopic-7791.aspx FPGA的“可编程”使你迷惑吗? 任何一个硬件工程师对FPGA都不会陌生,就好比C语言对于软件工 ...

- FPGA与simulink联合实时环路系列——实验三 按键key

实验三 按键key 实验内容 在FPGA的实验中,经常涉及到按键的使用,按键是必不可少的人机交互的器件之一,在这些实验中,有时将按键的键值读取显示到数码管.LCD或者是通过串口传送到PC的串口助手上进 ...

- FPGA与simulink联合实时环路系列——实验二LED

实验二LED 实验内容 在实验一的基础上,将simulink产生的测试信号输出到FPGA开发板上的LED灯进行显示,这里要在生成的硬件模型上进行修改,将传送到FPGA的信号输出到8个LED灯上,并且对 ...

- FPGA优化之高扇出

Fanout即扇出,模块直接调用的下级模块的个数,如果这个数值过大的话,在FPGA直接表现为net delay较大,不利于时序收敛.因此,在写代码时应尽量避免高扇出的情况.但是,在某些特殊情况下,受到 ...

- 关于 FPGA 内部信号扇入扇出

扇入.扇出系数 扇入系数是指门电路允许的输入端数目.一般门电路的扇入系数为1—5,最多不超过8.扇出系数是指一个门的输出端所驱动同类型门的个数,或称负载能力.一般门电路的扇出系数为8,驱动器的扇出系数 ...

- FPGA Timing笔记

很多FPGA工程师都会遇到timing的问题,如何让FPGA跑到更快的处理频率是永久话题.决定FPGA的timing关键是什么?如何才能跑到更快的频率呢? A. 第一步需要了解FPGA的timing路 ...

- FPGA的引脚VCCINT 、VCCIO VCCA

首先是看到FPGA在配置的时候有三种不同的电VCCINT .VCCIO VCCA,于是就查了下有什么不同: FPGA一般会有许多引脚,那它们都有什么用呢? VCCINT为施加于 FPGA 内核逻辑的电 ...

- FPGA与simulink联合实时环路系列——实验一 测试

实验一 测试 实验内容 在simulink创建测试模块,通过测试模块产生信号,再传送到FPGA,FPGA读出后再将信号无处理传送回simulink进行显示.由此来测试整个硬件在环的功能是否正常,并且熟 ...

- FPGA与simulink联合实时环路系列—开篇

FPGA与simulink联合实时环路系列—开篇 作为网络上第一个开源此技术,笔者迫不及待地想将此技术分享出来,希望大家多多支持.笔者从2011年接触FPGA以来,从各个方面使用FPGA,无论是控制. ...

随机推荐

- 使用union all 命令之后如何对hive表格进行去重

业务场景大概是这样的,这里由两个hive表格,tableA 和 tableB, 格式内容都是这样的: uid cate1 cate2 在hive QL中,我们知道union有着自动去重的功能,但是那是 ...

- POJ:2674-Linear world(名字交换碰撞)

Linear world Time Limit: 3000MS Memory Limit: 65536K Total Submissions: 4514 Accepted: 1025 Descript ...

- [CodeChef]RIN(最小割)

Description 有m门课可以在n个学期内学习,第i门课在第j个学期的收益是\(X_{i,j}\),一个学期可以学多门课,有的课之间有依赖关系,即必须先学a再学b,求最大收益.n,m<= ...

- 8 实现10mins用户登录与注册

1.重新认识登录 2.实现登录功能 (1)Django 自带的authenticate, login模块 from django.contrib.auth import authenticate, l ...

- Spring Boot :Request请求处理流程

技术交流群:233513714

- 教你一步学会安装Hue

一.简介 hue是一个开源的apache hadoop ui系统,由cloudear desktop演化而来,最后cloudera公司将其贡献给了apache基金会的hadoop社区,它基于pytho ...

- 剑指Offer - 九度1360 - 乐透之猜数游戏

剑指Offer - 九度1360 - 乐透之猜数游戏2014-02-05 19:54 题目描述: 六一儿童节到了,YZ买了很多丰厚的礼品,准备奖励给JOBDU里辛劳的员工.为了增添一点趣味性,他还准备 ...

- 《Cracking the Coding Interview》——第1章:数组和字符串——题目8

2014-03-18 02:12 题目:判断一个字符串是否由另一个字符串循环移位而成. 解法:首先长度必须相等.然后将第一个串连拼两次,判断第二个串是否在这个连接串中. 代码: // 1.8 Assu ...

- JNDI和JDBC的区别和联系及其使用方法

一.JNDI 和JDBC的区别和联系 两者都是API,是连接数据库的标准.并不是什么产品或方法. 二.JDBC 全称:Java Database Connectivity 以一种统一的方式来对各种各样 ...

- (转\整)UE4游戏优化 多人大地型游戏的优化(三)GPU的优化

施主分享随缘,评论随心,@author:白袍小道 小道暗语: 1.因为小道这里博客目录没自己整,暂时就用随笔目录结构,所以二级目录那啥就忽略了.标题格式大致都是(原or转) 二级目录 (标题) 2.因 ...