计数器IP核

Quartus II提供的LPM_couter IP核的使用

FPGA设计方式:

原理图,Verilog HDL设计方式,IP核输入方式

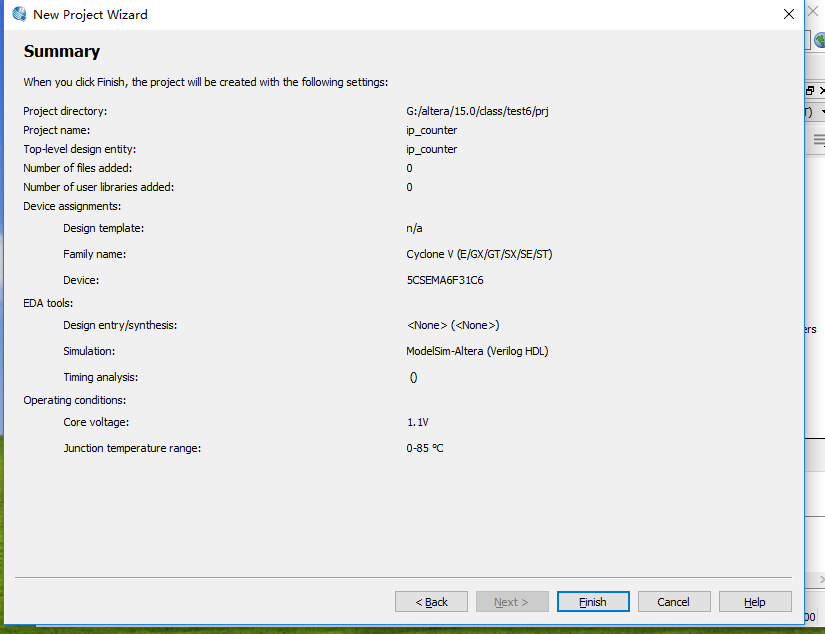

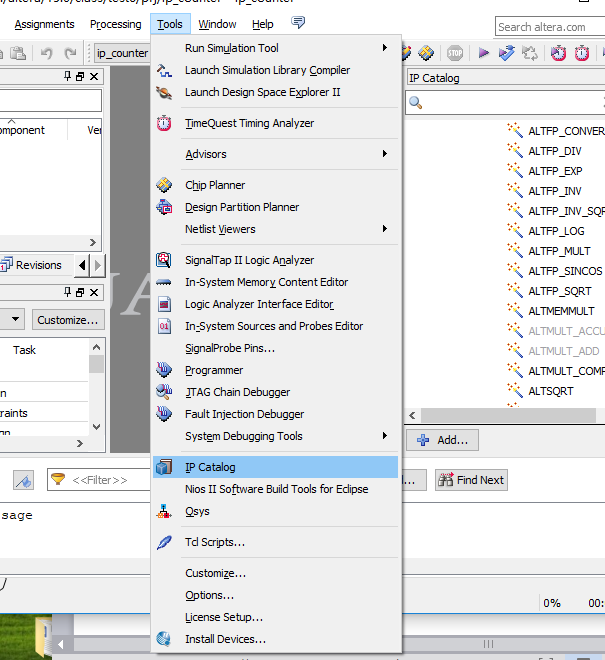

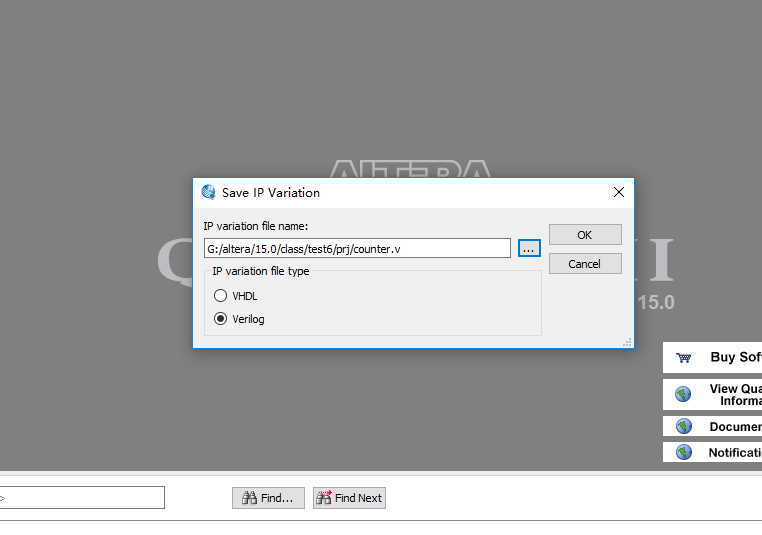

创建IP核

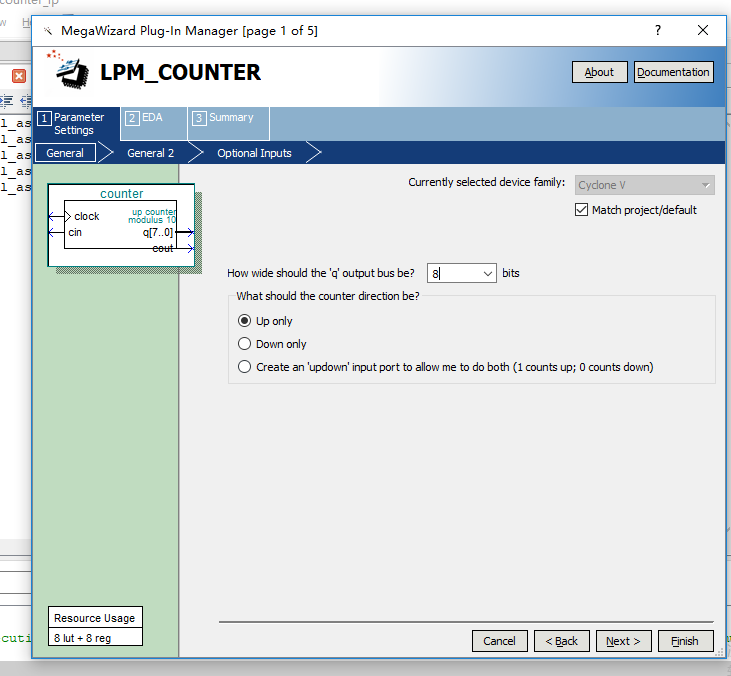

点击TOOLS—IP catalog-libray-Arithmetic-LPM_COUNTER

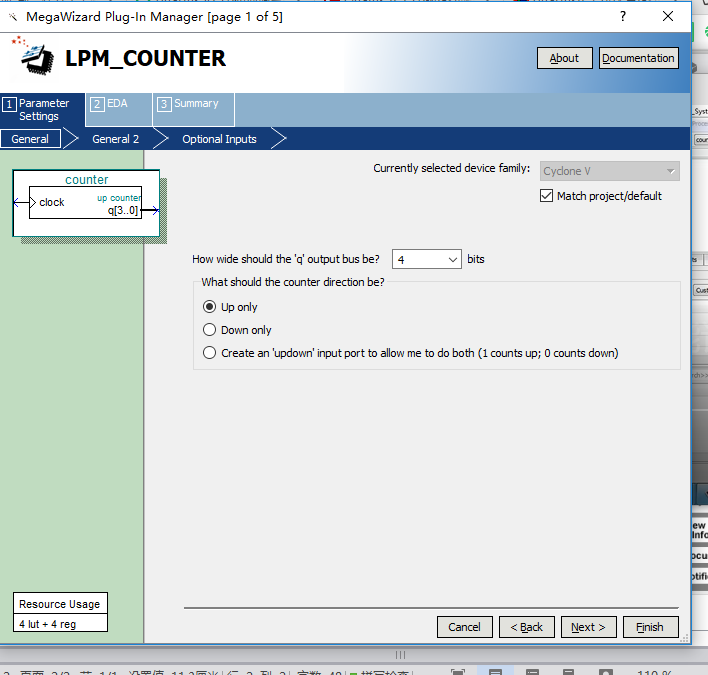

选择希望输出的寄存器是多少位的,计数类型。

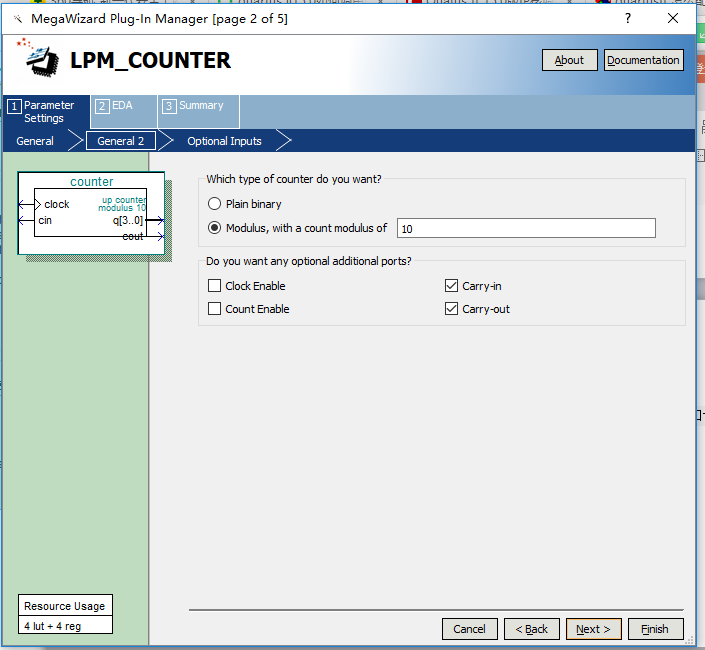

选择计数器类型(直接计数还是以模的形式计数),是否需要时钟使能和计数使能信号、进位链的输入和进位链的输出。

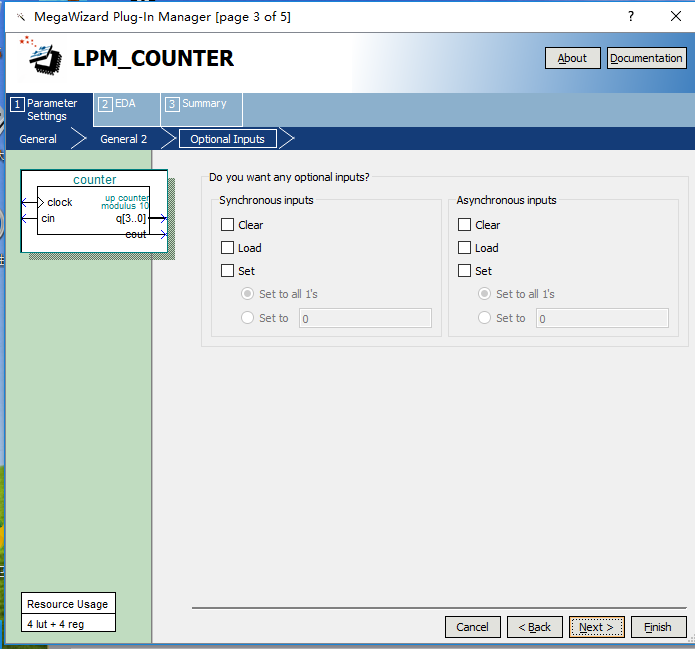

清零加载等信号

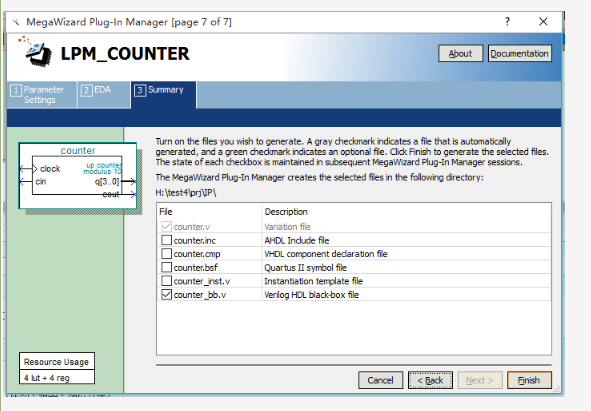

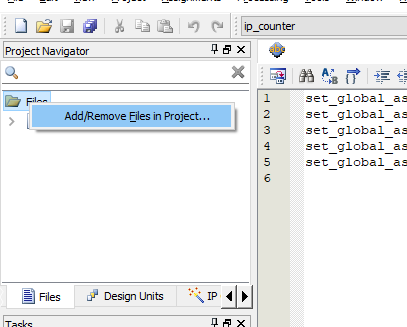

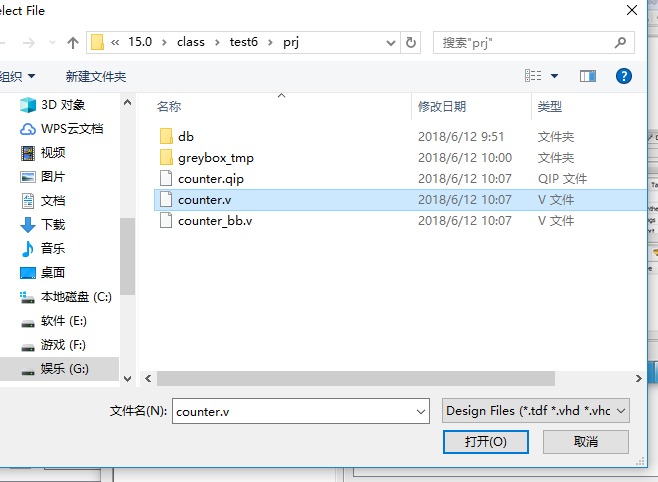

创建成功后的IP核的文件信息

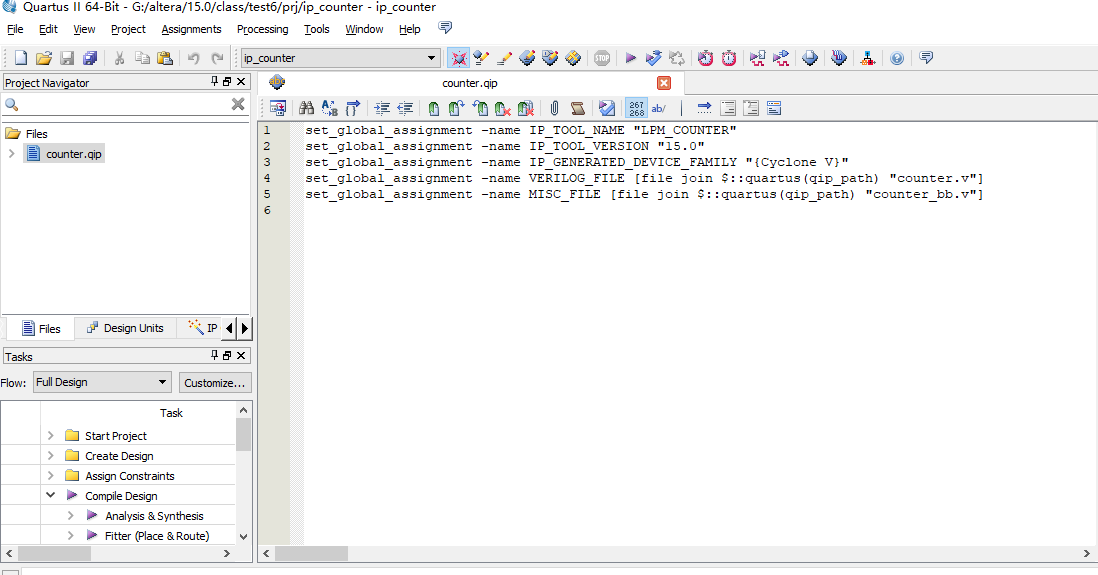

将counter.v文件加载到顶层文件中

Ip核已经做好了功能,直接利用就可以;

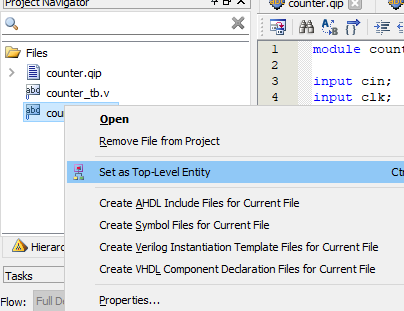

把counter_ip设置为顶层文件后进行编译。

编写testbench文件进行测试IP核功能

`timescale 1ns/1ns

`define clock_period

module counter_tb;

reg cin,clk; // 进位输入 计数基准时钟;

wire cout;//进位输出

wire [:] q;

counter counter0(

.cin(cin),

.clock(clk),

.cout(cout),

.q(q)

);

initial clk = ;

always #(`clock_period/)clk = ~clk;

initial begin

repeat()begin

cin = ;

#(`clock_period*)cin = ;

#(`clock_period)cin = ;

end

#(`clock_period*);

$stop;

end

endmodule

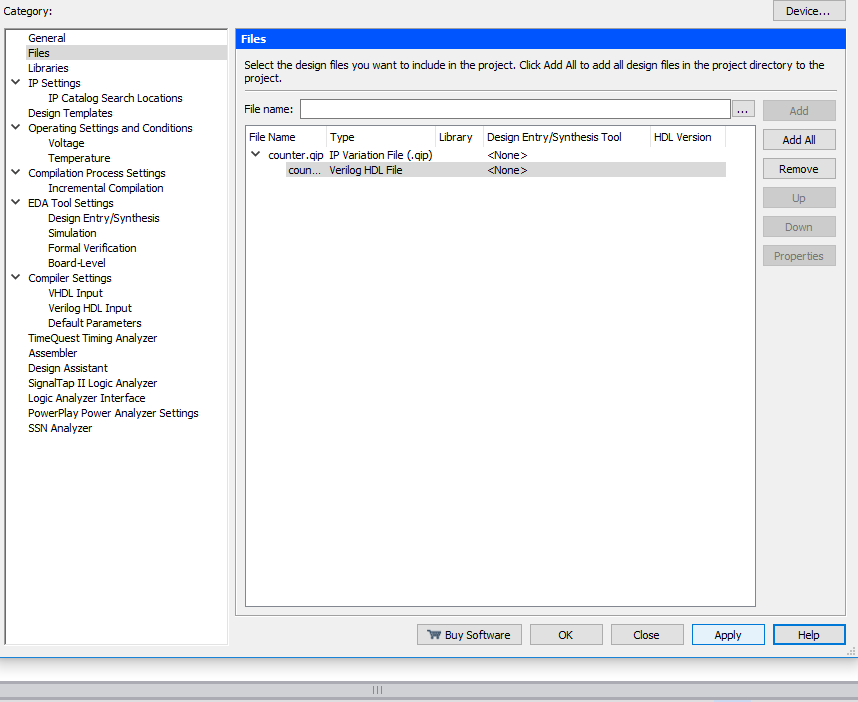

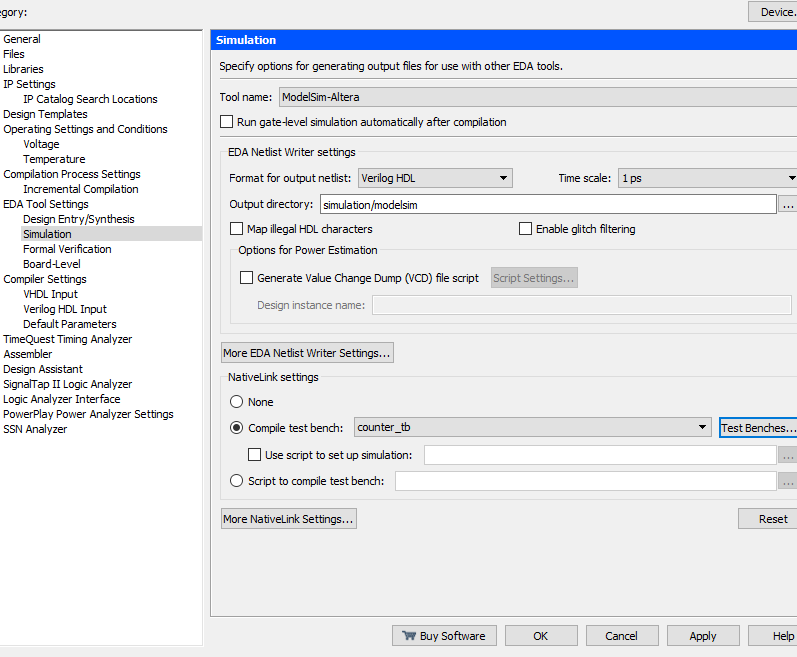

设置仿真

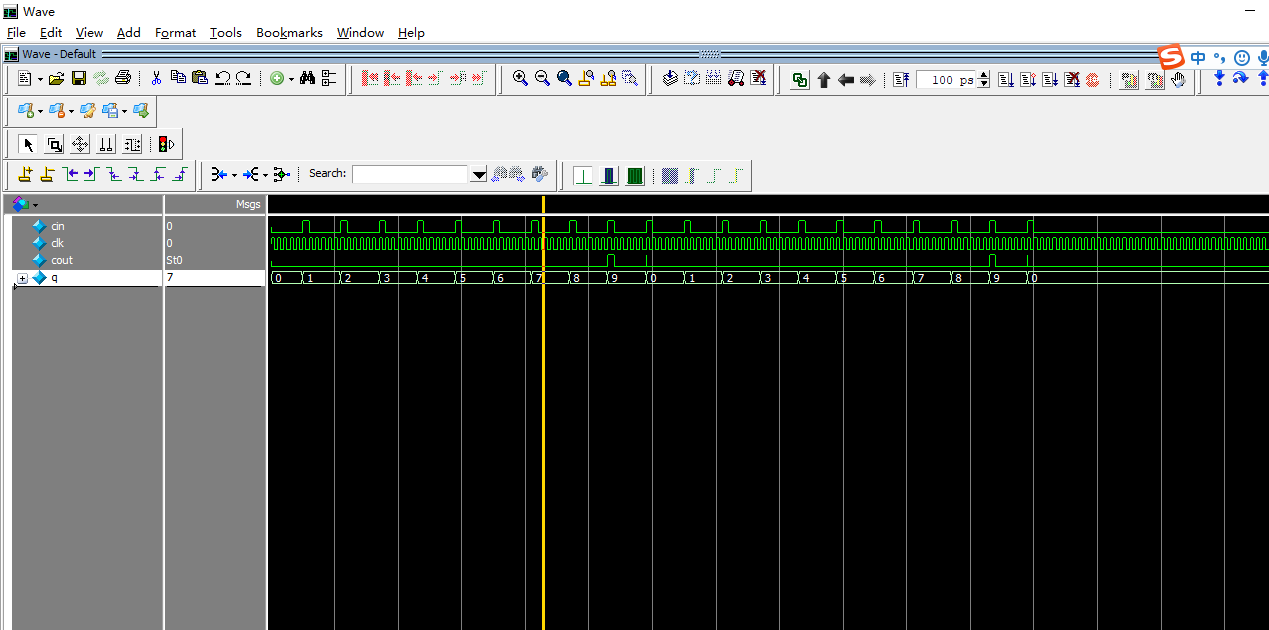

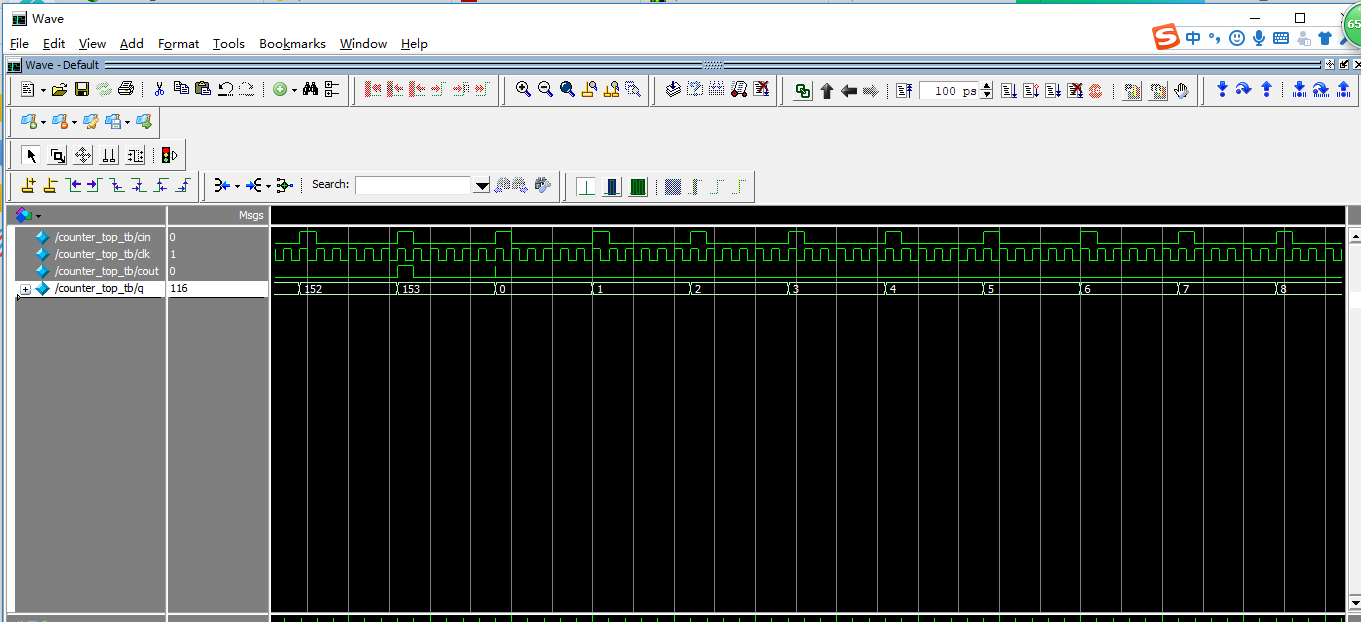

运行 仿真,可以看到每隔5个clk有一个cin信号,计数器完成一次计数,到计数到设定的模值10时会产生一次c_out信号,然后计数器重新开始从0开始计数,与设计的期望。

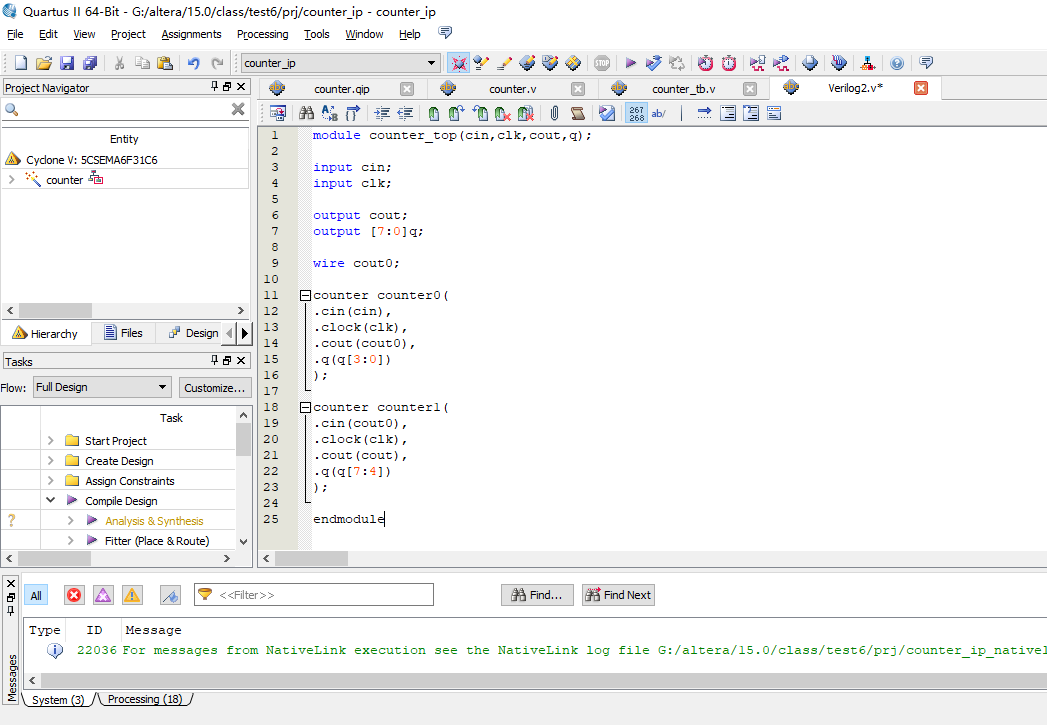

若要将计数器改为8位计数器:

(1)可以将 ip核改为8位

(2)也可以进行级联

新建Verilog文件进行编程如下。

这里的原理是将前一级的c_out作为下一级计数的c_in,此时即将两个计数器级连起来了,这样就将一个四位的计数器转换成了一个八位的计数器。

将这个文件设置为顶层文件。

module counter_top(cin,clk,cout,q); input cin;

input clk; output cout;

output [:]q; wire cout0; counter counter0(

.cin(cin),

.clock(clk),

.cout(cout0),

.q(q[:])

); counter counter1(

.cin(cout0),

.clock(clk),

.cout(cout),

.q(q[:])

); endmodule

编写testbench如下

`timescale 1ns/1ns

`define clock_period

module counter_top_tb;

reg cin,clk; // 进位输入 计数基准时钟;

wire cout;//进位输出

wire [:] q;

counter_top counter0(

.cin(cin),

.clk(clk),

.cout(cout),

.q(q)

);

initial clk = ;

always #(`clock_period/)clk = ~clk;

initial begin

repeat()begin

cin = ;

#(`clock_period*)cin = ;

#(`clock_period)cin = ;

end

#(`clock_period*);

$stop;

end endmodule

计数器IP核的更多相关文章

- 利用IP核设计高性能的计数器

利用Quartus II的LPM_counter IP核进行设计(利用IP核设计可以迅速高效的完成产品的设计) 新建工程 调用IP核 创建一个新的IP核 选择LMP_COUNTER,语言类型,输出路径 ...

- 调用altera IP核的仿真流程—上

调用altera IP核的仿真流程—上 在学习本节内容之后,请详细阅读<基于modelsim-SE的简单仿真流程>,因为本节是基于<基于modelsim-SE的简单仿真流程>的 ...

- IP核之初——FIFO添加以太网MAC头部

本文设计思路源自明德扬至简设计法.在之前的几篇博文中,由于设计比较简单,所有的功能都是用verilogHDL代码编写实现的.我们要学会站在巨人的肩膀上,这时候就该IP核登场了! 说白了,IP核就是别人 ...

- 自定义AXI总线形式SPI接口IP核,点亮OLED

一.前言 最近花费很多精力在算法仿真和实现上,外设接口的调试略有生疏.本文以FPGA控制OLED中的SPI接口为例,重新夯实下基础.重点内容为SPI时序的RTL设计以及AXI-Lite总线分析.当然做 ...

- IP核引发的关于定,浮点数的认识

上面是一段关于CORDIC_IP测试文件,用于计算给定角度的sin值和cos值,关于数值表示规则在此不再重复,仅仅说明以下3点: 1 数采用原码,反码,补码,本身并没有正确与否之分(这一点很重要,我 ...

- FIFO IP核

转载: 说白了,IP核就是别人做好了的硬件模块,提供完整的用户接口和说明文档,更复杂的还有示例工程,你只要能用好这个IP核,设计已经完成一半了.说起来容易,从冗长的英文文档和网上各个非标准教程中汲取所 ...

- 第7讲 SPI和RAM IP核

学习目的: (1) 熟悉SPI接口和它的读写时序: (2) 复习Verilog仿真语句中的$readmemb命令和$display命令: (3) 掌握SPI接口写时序操作的硬件语言描述流程(本例仅以写 ...

- SPI和RAM IP核

学习目的: (1) 熟悉SPI接口和它的读写时序: (2) 复习Verilog仿真语句中的$readmemb命令和$display命令: (3) 掌握SPI接口写时序操作的硬件语言描述流程(本例仅以写 ...

- 调用altera IP核的仿真流程—下

调用altera IP核的仿真流程—下 编译 在 WorkSpace 窗口的 counter_tst.v上点击右键,如果选择Compile selected 则编译选中的文件,Compile All是 ...

随机推荐

- Chrome 插件 postman 可以在线post

地址:https://chrome.google.com/webstore/detail/fhbjgbiflinjbdggehcddcbncdddomop

- 如何将博客搬至CSDN

简单聊下对于博客园的印象是技术改变世界,作为一个IT技术人员很乐意把这里当作自己的网上家园,每天在这里分享着精彩的原创内容,看重的不是华丽的外表.诱人的虚名,而是纯净.专注.对技术人员的理解. CSD ...

- java静态初始化块的执行顺序

先来观察下面的代码 package trr; class Root { static{ System.out.println("Root的静态初始化块"); } { System. ...

- Educational Codeforces Round 82 (Rated for Div. 2)

题外话 开始没看懂D题意跳了,发现F题难写又跳回来了.. 语文好差,码力好差 A 判第一个\(1\)跟最后一个\(1\)中\(0\)的个数即可 B 乘乘除除就完事了 C 用并查集判一下联通,每个联通块 ...

- linux--权限管理和用户管理

权限 查看详细信息 ls -l - rw- r-- r-- 1 tom root 0 Jun 20 00:02 apple.txt 1 2 3 4 5 6 7 8 9 10 #1 文件的类型 #[-: ...

- 【Unity|C#】基础篇(15)——异常处理(try/catch/throw)

[学习资料] <C#图解教程>(第22章):https://www.cnblogs.com/moonache/p/7687551.html 电子书下载:https://pan.baidu. ...

- 小程序y轴拖动

需求场景 小程序在y轴方向 拖动 一小段距离 解决方案 1.监听 元素 2.绑定 点击 和 移动 事件 3.数据处理 代码 <view animation="{{item.animat ...

- 南昌邀请赛B题(拉格朗日插值)

题目链接:https://nanti.jisuanke.com/t/40254 #include<iostream> #include<cstdio> #include< ...

- 莫凡_linux

1.安装软件 2.基本命令ls和cd cd 指令 第一个要知道的指令就是怎么样去到你想去的地方. cd (Change Directory) 就是干这个的. 找到 Linux 的 terminal 窗 ...

- springboot 扫描不到包 @SpringBootApplication 自动配置原理

解决方案 在main类中增加注解 @ComponentScan("com.test.test.*") 扫描具体的包 @ComponentScan(basePackages = {& ...