基于FPGA的74ls148设计

1 74ls148简介

74ls148是8线-3线优先编码器,将 8 条数据线(0-7)进行 3 线(4-2-1)二进制(八进制)优先编码,即对最高位数据线进行译码。利用选通端(EI)和输出选通端(EO)可进行八进制扩展。

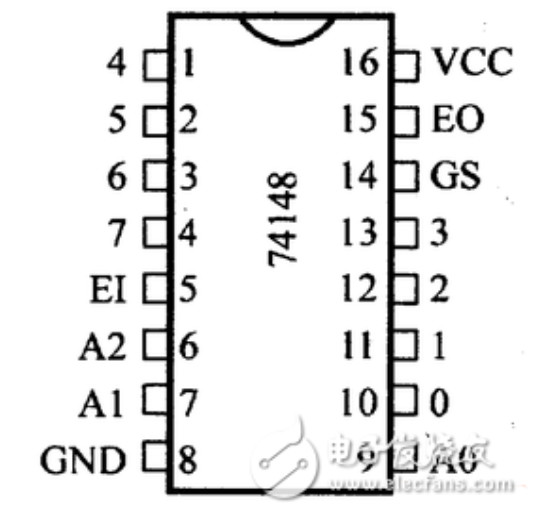

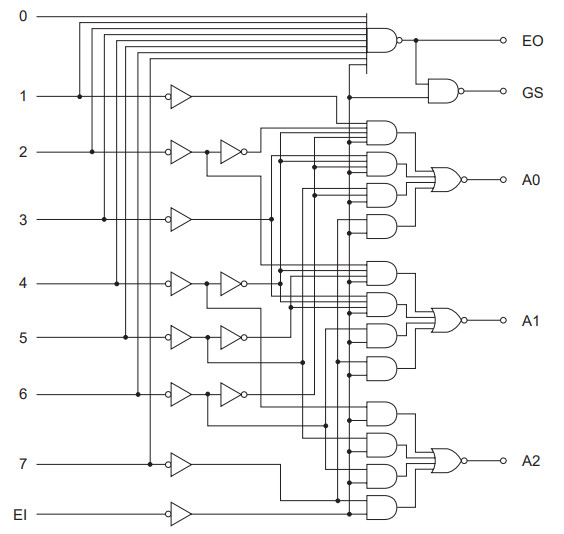

2 74ls148管脚图和逻辑图

管脚介绍

0-7 编码输入端(低电平有效)

EI 选通输入端(低电平有效)

A0、A1、A2 三位二进制编码输出信号即编码输出端(低电平有效)

GS 片优先编码输出端即宽展端(低电平有效)

EO 选通输出端,即使能输出端

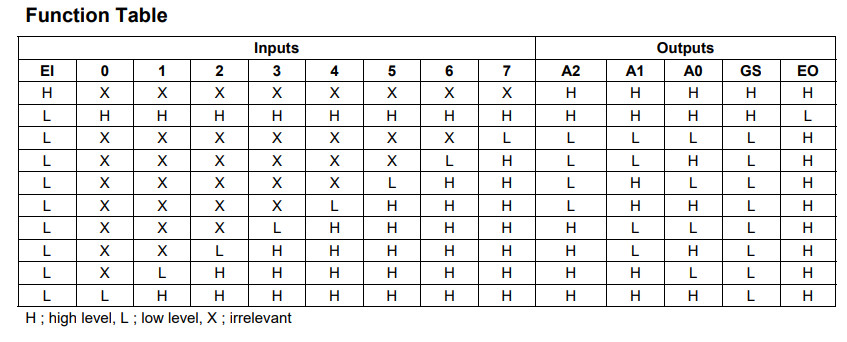

3 74ls148真值表

4 74ls148工作原理

该编码器有8个信号输入端,3个二进制码输出端。此外,电路还设置了输入使能端EI,输出使能端EO和优先编码工作状态标志GS。当EI=0时,编码器工作;而当EI=1时,则不论8个输入端为何种状态,3个输出端均为高电平,且优先标志端和输出使能端均为高电平,编码器处于非工作状态。这种情况被称为输入低电平有效,输出也为低电来有效的情况。当EI为0,且至少有一个输入端有编码请求信号(逻辑0)时,优先编码工作状态标志GS为0。表明编码器处于工作状态,否则为1。

5 74ls148的Verilog设计

1 module ttl_74148(

2 input wire D0,D1,D2,D3,D4,D5,D6,D7, //输入信号,低电平有效

3 input wire EI, //输入使能

4 output reg A0,A1,A2, //输出信号,

5 output reg GS, //优先编码工作状态标志,0表示工作状态

6 output reg EO //输出使能

7 );

8

9 always@(*)begin

10 if(EI)

11 begin {A2,A1,A0} = 3'b111; GS = 1'b1; EO = 1'b1; end

12 else if({D7,D6,D5,D4,D3,D2,D1,D0} == 8'b1111_1111)

13 begin {A2,A1,A0} = 3'b111; GS = 1'b1; EO = 1'b0; end

14 else if(!D7)

15 begin {A2,A1,A0} = 3'b000; GS = 1'b0; EO = 1'b1; end

16 else if(!D6)

17 begin {A2,A1,A0} = 3'b001; GS = 1'b0; EO = 1'b1; end

18 else if(!D5)

19 begin {A2,A1,A0} = 3'b010; GS = 1'b0; EO = 1'b1; end

20 else if(!D4)

21 begin {A2,A1,A0} = 3'b011; GS = 1'b0; EO = 1'b1; end

22 else if(!D3)

23 begin {A2,A1,A0} = 3'b100; GS = 1'b0; EO = 1'b1; end

24 else if(!D2)

25 begin {A2,A1,A0} = 3'b101; GS = 1'b0; EO = 1'b1; end

26 else if(!D1)

27 begin {A2,A1,A0} = 3'b110; GS = 1'b0; EO = 1'b1; end

28 else

29 begin {A2,A1,A0} = 3'b111; GS = 1'b0; EO = 1'b1; end

30 end

31

32 endmodule

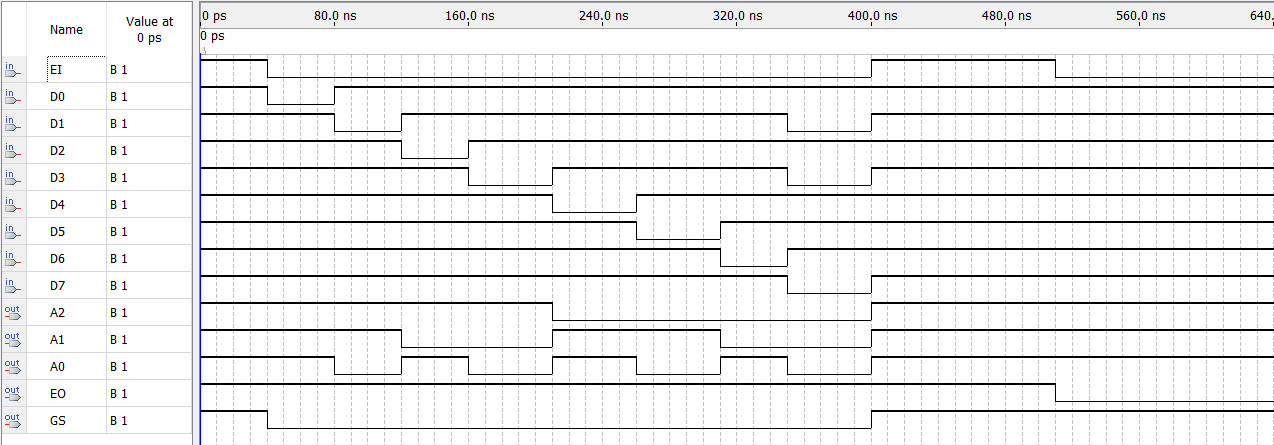

6 波形仿真测试结果

参考资料:

(1)优先编码器74ls148引脚图及功能介绍(工作原理,逻辑图及应用电路) - 电子常识 - 电子发烧友网 (elecfans.com);

基于FPGA的74ls148设计的更多相关文章

- 基于FPGA的DDS设计(一)

最近在学习基于FPGA的DDS设计,借此机会把学习过程记录下来,当作自己的学习笔记也希望能够帮助到学习DDS的小伙伴. DDS(Direct Digital Synthesizer)直接数字合成器,这 ...

- 基于FPGA的DDS设计(二)

在DDS设计中,如果相位累加器每个时钟周期累加1,就会输出频率为195.313KHz的波形.如果每个时钟周期累加2,就会输出频率为2*195.313KHz的波形·······,如果每两个时钟周期累加1 ...

- 38.基于FPGA的FIR设计二

利用fdatool工具生成的滤波器系数与用代码生成的系数不一致,在网上查询得知,fdatool生成的滤波器系数是有符号小数,而且是浮点型,而代码生成的滤波器系数是定点型有符号数,故不一样. 浮点型数据 ...

- 优化基于FPGA的深度卷积神经网络的加速器设计

英文论文链接:http://cadlab.cs.ucla.edu/~cong/slides/fpga2015_chen.pdf 翻译:卜居 转载请注明出处:http://blog.csdn.net/k ...

- 自己动手写CPU(基于FPGA与Verilog)

大三上学期开展了数字系统设计的课程,下学期便要求自己写一个单周期CPU和一个多周期CPU,既然要学,就记录一下学习的过程. CPU--中央处理器,顾名思义,是计算机中最重要的一部分,功能就是周而复始地 ...

- 基于FPGA的XPT2046触摸控制器设计

基于FPGA的XPT2046触摸控制器设计 小梅哥编写,未经许可,文章内容和所涉及代码不得用于其他商业销售的板卡 本实例所涉及代码均可通过向 xiaomeige_fpga@foxmail.com 发 ...

- 基于FPGA的HDMI显示设计(三)

上一篇:基于FPGA的VGA显示设计(二) 10月10日 ~ 20日期间实习,令我万万没想到的是实习题目是 “便携式高清电视显示屏测试系统原型设计” 也就是 “基于FPGA的视频显示”. 实习要求用 ...

- 基于FPGA的VGA显示设计(二)

上一篇:基于FPGA的VGA显示设计(一) 参照 CrazyBingo 的 基于FPGA的VGA可移植模块终极设计代码 的工程代码风格,模块化处理了上一篇的代码,并增加了一点其它图形. 顶层 ...

- 基于FPGA的VGA可移植模块终极设计【转】

本文转载自:http://www.cnblogs.com/lueguo/p/3373643.html 略过天涯 基于FPGA的VGA可移植模块终极设计 一.VGA的诱惑 首先,VGA的驱动,这事, ...

- 基于FPGA的SPI FLASH控制器设计

1.SPI FLASH的基本特征 本文实现用FPGA来设计SPI FLASH,FLASH型号为W25Q128BV.支持3种通信方式,SPI.Dual SPI和Quad SPI.FLASH的存储单元无法 ...

随机推荐

- Mybatis - 精巧的持久层框架 - 注解开发深刻理解

Mybaits的注解开发是现代Java项目(特别是Spring Boot项目)中非常主流的开发方式.它能让你摆脱繁琐的XML文件,以一种更"Java-Native"的方式编写数据访 ...

- Flink初体验-批处理与流处理

一.环境准备 本机环境:jdk11.scala2.12.maven3.6 新建一个maven项目,pom如下 <?xml version="1.0" encoding=&qu ...

- 极大提高项目部署的生产力!分享一个半自动化的CICD实现方案

前言 完全自动化的 CICD 确实好,代码提交后就自动构建自动发布新版本,实现不停机更新的情况下,还能随时回滚,这搁谁不喜欢啊~ 但理想很丰满,现实往往很骨感,不是所有开发/生产环境都具备部署 CIC ...

- 第三代长安75p安装三方软件

前言 长安的车机系统是 长安与腾讯联合且基于安卓自研的 梧桐车联系统. 通过一些特殊方式,打开了车机的系统信息真身 此系统极为封闭,默认情况下,不允许安装除了车机本身应用商店之外的三方软件,本身内置的 ...

- docusaurus默认访问地址前缀 以及多实例

前言 默认情况下 所有的md文档 都应该以docs为根目录. you-project |--docs |--test.md 而访问路由 也是默认的http://localhost:3000/docs/ ...

- Rust修仙之道 第十二章:宽度境 · 类型尺寸认知与不定形之术

第十二章:宽度境 · 类型尺寸认知与不定形之术 "形有大小,道有边界.不能测其尺者,不可轻控其灵." 当顾行云修炼 Trait 技法至高阶,试图为"无定形灵体" ...

- jq 插件 的两个相关的函数 jQuery.fn.extend(object); jQuery.extend(object);

jQuery为开发插件提拱了两个方法,分别是: http://www.cnblogs.com/wyjgreat/archive/2011/07/19/2110754.html jq.fn 的实现 是 ...

- Terminai:重新定义终端的革命性工具

Terminai 是 Codigger 推出的一款革命性终端工具,它巧妙地将传统终端命令的强大功能与图形用户界面(GUI)的直观易用性无缝融合,旨在为用户带来前所未有的编辑体验 .它不仅是一个工具,更 ...

- 兄弟们!!!15天超100k

两周之前为了满足自己的一个小需求,开始构思做一个在线拼图网站,我出想法和思路,编码则全部交给了AI,仅一天时间第一个可用版本上线,网站做好颇有成就,于是分享给了朋友们体验,至此开启了一段美妙的旅程,朋 ...

- Windows关闭自动更新

方法1:修改注册表编辑器 文字流程 Win+R 输入 regedit 输入路径 计算机\HKEY_LOCAL_MACHINE\SYSTEM\CurrentControlSet\Services\Uso ...