FPGA中亚稳态相关问题及跨时钟域处理

前言

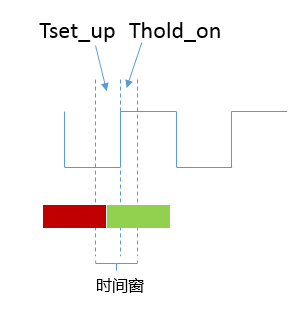

触发器输入端口的数据在时间窗口内发生变化,会导致时序违例。触发器的输出在一段时间内徘徊在一个中间电平,既不是0也不是1。这段时间称为决断时间(resolution time)。经过resolution time之后Q端将稳定到0或1上,但是稳定到0或者1,是随机的,与输入没有必然的关系。

触发器由于物理工艺原因,数据并不是理想化的只要触发沿时刻不变即可。触发器有固定的建立时间,保持时间。

建立时间:在时钟有效沿到来前数据需要稳定的时间。

保持时间:在时钟有效沿之后数据还需要保持不变的时间。

后果:会给设计带来致命的功能故障。

一般来说,信号是在异步信号,跨时钟域,复位电路中产生亚稳态。

解决方式:

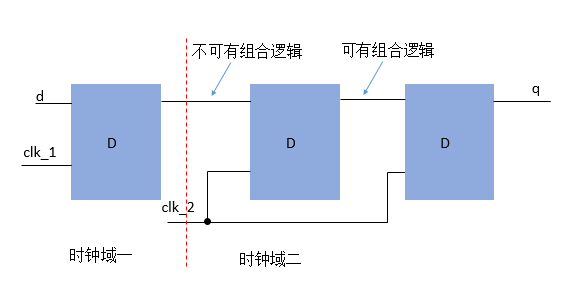

1.单比特信号:

①采用同步器同步,低速设计打两拍,高速设计可能需要打三拍。

低速到高速时钟域,低速信号一般能被高速时钟域采到甚至多次。但高速时钟域到低速时钟域就不太好办了:

②闭环解决方案:采用握手反馈信号,这会导致延时开销大。

③开环解决方案:把信号展宽,至少为采样T的1.5倍。这样至少能采到一次。

2.多比特信号:

传递多比特信号,普通同步器就没啥卵用了,因为多比特信号偶发数据变化歪斜,导致采到的不一定是正确数据。

①多比特信号融合:把多比特信号转换为单比特信号,再用同步器同步。

②多周期路径规划:数据不需要同步,至需要同时传递一个同步的使能信号到接收时钟域即可,使能信号没被同步到接收时钟域并被识别之前数据不被采集。即在信号某个沿产生同步脉冲指示信号。

③异步fifo。

以上。

FPGA中亚稳态相关问题及跨时钟域处理的更多相关文章

- FPGA跨时钟域处理方法

文章主要是基于学习后的总结. 1. 时钟域 假如设计中所有的触发器都使用一个全局网络,比如FPGA的主时钟输入,那么我们说这个设计只有一个时钟域.假如设计有两个输入时钟,如图1所示,一个时钟给接口1使 ...

- 异步FIFO跨时钟域亚稳态如何解决?

跨时钟域的问题:前一篇已经提到要通过比较读写指针来判断产生读空和写满信号,但是读指针是属于读时钟域的,写指针是属于写时钟域的,而异步FIFO的读写时钟域不同,是异步的,要是将读时钟域的读指针与写时钟域 ...

- FPGA基础学习(3) -- 跨时钟域处理方法

文章主要是基于学习后的总结. 1. 时钟域 假如设计中所有的触发器都使用一个全局网络,比如FPGA的主时钟输入,那么我们说这个设计只有一个时钟域.假如设计有两个输入时钟,如图1所示,一个时钟给接口1使 ...

- FPGA中亚稳态——让你无处可逃

1. 应用背景 1.1 亚稳态发生原因 在FPGA系统中,如果数据传输中不满足触发器的Tsu和Th不满足,或者复位过程中复位信号的释放相对于有效时钟沿的恢复时间(recovery ti ...

- 基于FPGA的跨时钟域信号处理——专用握手信号

在逻辑设计领域,只涉及单个时钟域的设计并不多.尤其对于一些复杂的应用,FPGA往往需要和多个时钟域的信号进行通信.异步时钟域所涉及的两个时钟之间可能存在相位差,也可能没有任何频率关系,即通常所说的不同 ...

- cdc跨时钟域处理-结绳握手法

参考文档 https://blog.csdn.net/u011412586/article/details/10009761 前言 对于信号需要跨时钟域处理而言,最重要的就是确保数据能稳定的传送到采样 ...

- 跨时钟域设计【一】——Slow to fast clock domain

跨时钟域设计是FPGA设计中经常遇到的问题,特别是对Trigger信号进行同步设计,往往需要把慢时钟域的Trigger信号同步到快时钟域下,下面是我工作中用到的慢时钟域到快时钟域的Verilog HD ...

- 跨时钟域设计【二】——Fast to slow clock domain

跨时钟域设计中,对快时钟域的Trigger信号同步到慢时钟域,可以采用上面的电路实现,Verilog HDL设计如下: // Trigger signal sync, Fast clock dom ...

- FPGA跨时钟域握手信号的结构

FPGA跨时钟数据传输,是我们经常遇到的问题的,下面给出一种跨时钟握手操作的电路结构.先上图 先对与其他人的结构,这个结构最大的特点是使用 req 从低到高或者高到低的变化 来表示DIN数据有效并开始 ...

随机推荐

- Python Revisited Day 02 (数据类型)

目录 Python 关键字 整数 整数转换函数 整数位逻辑操作符 浮点类型 math模块函数与常量 复数 精确的十进制数字 decimal 字符串 str.format() 格式规约 Python 关 ...

- long double

long double 输入输出 scanf("%Lf",&a); printf("%.20Lf\n",a);

- 为什么HashMap初始大小为16,为什么加载因子大小为0.75,这两个值的选取有什么特点?

先看HashMap的定义: public class HashMap<K,V>extends AbstractMap<K,V>implements Map<K,V> ...

- Oracle和Elasticsearch数据同步

Python编写Oracle和Elasticsearch数据同步脚本 标签: elasticsearchoraclecx_Oraclepython数据同步 Python知识库 一.版本 Pyth ...

- 软工网络15团队作业7——Alpha冲刺之事后诸葛亮

Deadline: 2018-5-16 22:00PM,以博客提交至班级博客时间为准 事后诸葛亮分析 Alpha冲刺,很多同学经历了"Learning by doing"的学一门新 ...

- 03-Linux的shell命令 .doc

快捷键 基本操作和命令 Cd转换文件夹 以/开头的是绝对路径 没有/相对路径 ../代表上一级目录 Tab补充 Ctrl+R 查找历史输入过的命令 箭头上也代表能够查询以往输入的命令 Ctrl+C 终 ...

- 生成短链接的URL

假设你想做一个像微博短链接那样的短链接服务,短链接服务生成的URL都非常短例如: http://t.cn/E70Piib, 我们应该都能想到链接中的E70Piib对应的就是存储长链接地址的数据记录的I ...

- API接口TOKEN设计

首先需要知道API是什么? API(Application Programming Interface)即应用程序接口.你可以认为 API 是一个软件组件或是一个 Web 服务与外界进行的交互的接 ...

- JS刷新当前页面的几种方法总结

reload 方法,该方法强迫浏览器刷新当前页面. 语法:location.reload([bForceGet]) 参数: bForceGet, 可选参数, 默认为 false,从客户端缓存里取当前页 ...

- React Native之FlatList的介绍与使用实例

React Native之FlatList的介绍与使用实例 功能简介 FlatList高性能的简单列表组件,支持下面这些常用的功能: 完全跨平台. 支持水平布局模式. 行组件显示或隐藏时可配置回调事件 ...