FPGA基础学习(6) -- 原语

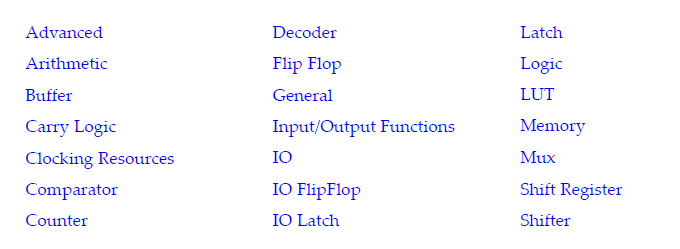

原语,即primitive。不同的厂商,原语不同;同一家的FPGA,不同型号的芯片,可以也不一样;原语类似最底层的描述方法。使用原语的好处,可以直接例化使用,不用定制IP;即可通过复制原语的语句,然后例化IP,就可使用;Xilinx是通过直接修改原语中的参数再例化IP来使用;Xilinx公司的原语分为10类,包括:计算组件,IO端口组件,寄存器/锁存器,时钟组件,处理器组件,移位寄存器,配置和检测组件,RAM/ROM组件,Slice/CLB组件,G-tranceiver。下图所示为UG799中对原语的分类列表。

项目中主要用到的原语与IO端口有关,所以基本在Input/Output Functions 和IO两类中。下面着重介绍实际中所用到的几个原语,芯片A7系列。

1. IBUF和IBUFDS(IO)

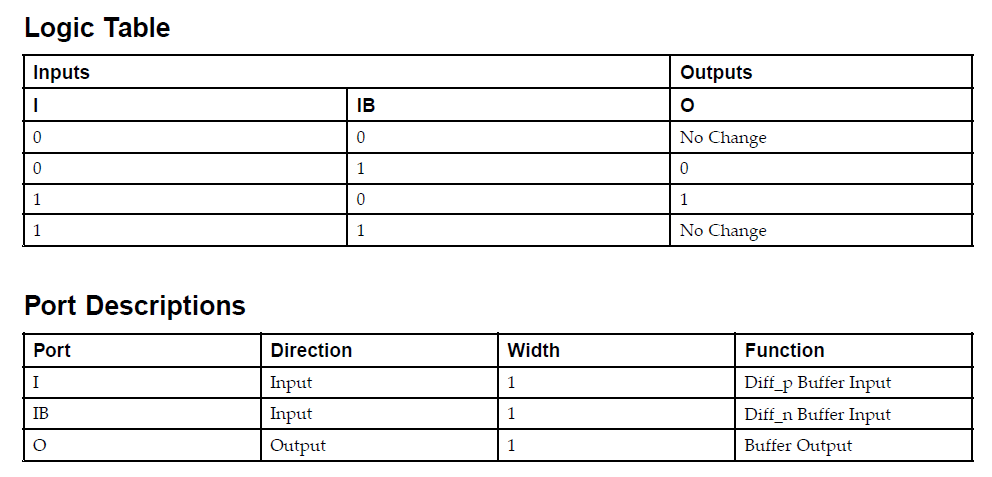

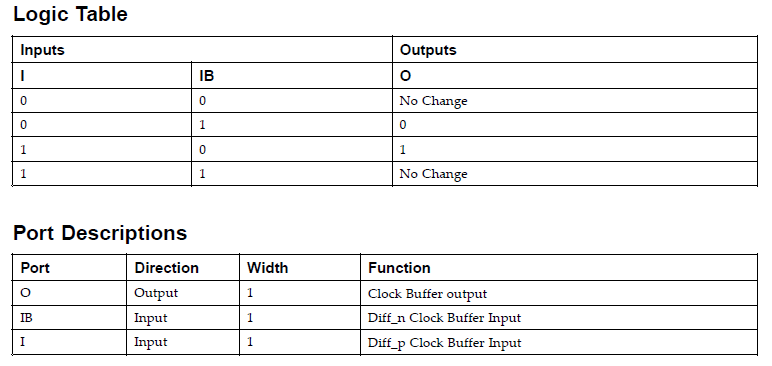

IBUF是输入缓存,一般vivado会自动给输入信号加上,IBUFDS是IBUF的差分形式,支持低压差分信号(如LVCMOS、LVDS等)。在IBUFDS中,一个电平接口用两个独特的电平接口(I和IB)表示。一个可以认为是主信号,另一个可以认为是从信号。主信号和从信号是同一个逻辑信号,但是相位相反。

举例说明:

LVDS_25的差分输入的ADC数据。

IBUFDS #( // 差分输入原语,用于LVDS_25端口

.DIFF_TERM("TRUE"),

.IOSTANDARD("LVDS_25")

) IBUFDS_ADC01 (

.O(ADC01_D[i]),

.I(ADC01_P_D[i]),

.IB(ADC01_N_D[i])

);

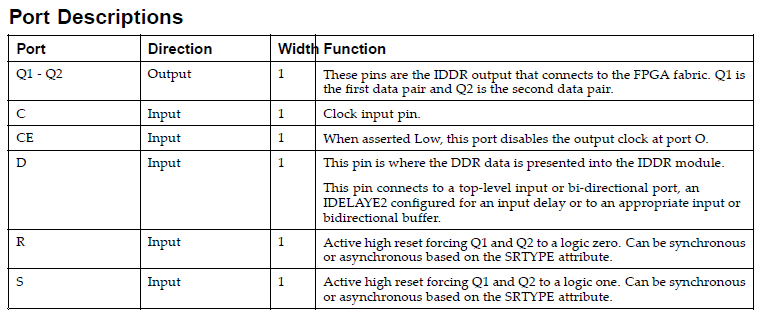

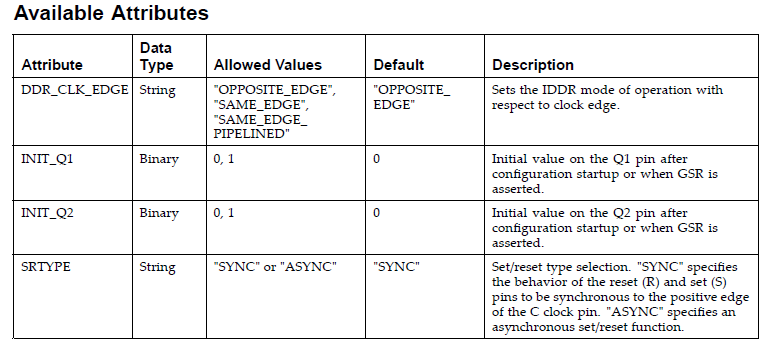

2. IDDR(Input/Output Functions)

被设计用来接收DDR数据,避免额外的时序复杂性。

举例说明:

差分数据源经过差分转单端后,生产ADC01_D,在同步时钟ADC01_DCO的驱动下,产生DDR数据adc01_a_d和adc01_b_d。

IDDR #(

.DDR_CLK_EDGE("SAME_EDGE_PIPELINED"),

.INIT_Q1(1'b0),

.INIT_Q2(1'b0),

.SRTYPE("SYNC")

) IDDR_ADC01_D (

.Q1(adc01_a_d),

.Q2(adc01_b_d),

.C(ADC01_DCO),

.CE(1'b1),

.D(ADC01_D),

.R(1'b0),

.S(1'b0)

);

3. IBUFG和IBUFGDS(IO)

IBUFG即输入全局缓冲,是与专用全局时钟输入管脚相连接的首级全局缓冲。所有从全局时钟管脚输入的信号必须经过IBUF元,否则在布局布线时会报错。 IBUFG支持AGP、CTT、GTL、GTLP、HSTL、LVCMOS、LVDCI、LVDS、LVPECL、LVTTL、PCI、PCIX和 SSTL等多种格式的IO标准。

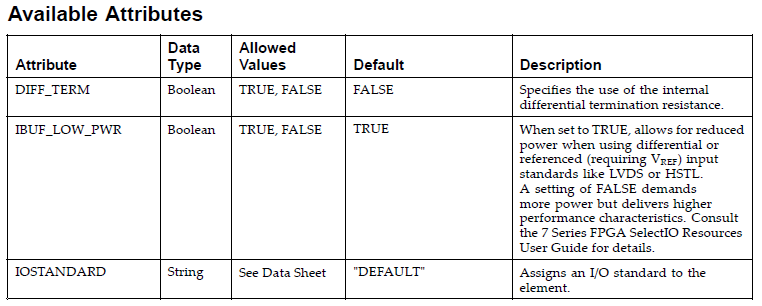

IBUFGDS是IBUFG的差分形式,当信号从一对差分全局时钟管脚输入时,必须使用IBUFGDS作为全局时钟输入缓冲。IBUFG支持BLVDS、LDT、LVDSEXT、LVDS、LVPECL和ULVDS等多种格式的IO标准。

举例说明:

差分时钟芯片输入的100MHz时钟,作为FPGA的全局时钟。

IBUFGDS #(

.DIFF_TERM ("TRUE" ),

.IBUF_LOW_PWR ("FALSE")

) u_ibufg_clk_100 (

.I (FP_CLK_100M_P),

.IB (FP_CLK_100M_N),

.O (clk_100m )

);

参考文献:

《Xilinx 7 Series FPGA and Zynq-7000 All Programmable SoC Libraries Guide for Schematic Designs》(UG799)

FPGA基础学习(6) -- 原语的更多相关文章

- FPGA基础学习(7) -- 内部结构之CLB

目录 1. 总览 2. 可配置逻辑单元 2.1 6输入查找表(LUT6) 2.2 选择器(MUX) 2.3 进位链(Carry Chain) 2.4 触发器(Flip-Flop) 参考文献: 一直以来 ...

- FPGA基础学习(3) -- 跨时钟域处理方法

文章主要是基于学习后的总结. 1. 时钟域 假如设计中所有的触发器都使用一个全局网络,比如FPGA的主时钟输入,那么我们说这个设计只有一个时钟域.假如设计有两个输入时钟,如图1所示,一个时钟给接口1使 ...

- FPGA基础学习(9) -- 复位设计

目录 1. 常见问题 2. 常见的复位方式 3. 合理的复位设计 3.1 复位电平 3.2 异步复位同步化 3.3 恰到好处的复位 4. 补充 4.1 所谓的上电初始化 参考文献 一开始接触到FPGA ...

- FPGA基础学习(5) -- 时序约束(实践篇)

目录 1. 理论回顾 2. 时间裕量 3. 最大延迟和最小延迟 4. 案例分析 参考文献: 距离上一篇有关时序的理论篇已经有一段时间了(可以参考博文FPGA时序约束--理论篇),实际上此段时间,甚至到 ...

- FPGA基础学习(8) --内部结构之存储单元

目录 1. 基本结构 2. BRAM与DRAM的比较 3. BRAM的特点 4. Block Memory的使用 4.1 配置为RAM或ROM 4.2. 配置为FIFO 参考文献: 上一篇中提到了SL ...

- FPGA基础学习(4) -- 时序约束(理论篇)

在FPGA 设计中,很少进行细致全面的时序约束和分析,Fmax是最常见也往往是一个设计唯一的约束.这一方面是由FPGA的特殊结构决定的,另一方面也是由于缺乏好用的工具造成的.好的时序约束可以指导布局布 ...

- FPGA基础学习(1) -- FFT IP核(Quartus)

为了突出重点,仅对I/O数据流为steaming的情况作简要说明,以便快速上手,有关FFT ip核模型及每种设置详细介绍请参考官方手册FFT MegaCore Function User Guide. ...

- FPGA基础学习(2) -- FIFO IP核(Quartus)

ALTERA在LPM(library of parameterized mudules)库中提供了参数可配置的单时钟FIFO(SCFIFO)和双时钟FIFO(DCFIFO).FIFO主要应用在需要数据 ...

- FPGA基础知识了解

FPGA学习的一些误区 FPGA入门必看资源 FPGA百度百科 FPGA基础知识及其工作原理 高端设计工具为少有甚是没有硬件设计技术的工程师和科学家提供现场可编程门阵列(FPGA).无论你使用图形化设 ...

随机推荐

- java简单例子介绍IOC和AOP

IOC和AOP的一些基本概念 介绍 IOC 一.什么是IOC IoC就是Inversion of Control,控制反转.在Java开发中,IoC意味着将你设计好的类交给系统去控制,而不是在你的类内 ...

- Smarty模板的引用

(1)include用法和php里的include差不多(2)smarty的include还具备自定义属性的功能例如 {include file="header.tpl" titl ...

- java中jar打包的方法

jar 应用 先打开命令提示符(win2000或在运行筐里执行cmd命令,win98为DOS提示符),输入jar -help,然后回车(如果你盘上已经有了jdk1.1或以上版本),看到什么:用法:ja ...

- sql语言的一大类 DML 数据的操纵语言

-DML(insert,update,delete) 1.插入数据insert into 表名(列,列...)values(值,值...)//当插入的数据与表格一一对应时,列可以省略insert in ...

- Android PendingIntent小结

官方文档的解释 A description of an Intent and target action to perform with it. 注意有一个target action,既Pen ...

- C#调用windows命令行(CMD)

using System.Diagnostics; public static void StartCmd(String command){Process p = new Process();p.St ...

- JavaScript学习总结——转

JavaScript学习总结(一)——JavaScript基础 JavaScript学习总结(二)——逻辑Not运算符详解 JavaScript学习总结(三)——逻辑And运算符详解 JavaScri ...

- WPF学习资源整理

WPF(WindowsPresentation Foundation)是微软推出的基于Windows Vista的用户界面框架,属于.NET Framework 3.0的一部分.它提供了统一的编程模型 ...

- 使用华邦的SPI FLASH作为EPCS时固化NIOS II软件报错及解决方案

Altera器件有EPCS系列配置器件,其实,这些配置器件就是我们平时通用的SPIFlash,据AlteraFAE描述:“EPCS器件也是选用某家公司的SPIFlash,只是中间经过Altera公司的 ...

- APUE(5)---标准I/O库 (2)

六.读和写流 一旦打开了流,则可在3种不同类型的非格式化I/O中进行选择,对其进行读.写操作:1)每次一个字符的I/O,一次读或写一个字符,如果刘时代缓冲的,则标准I/O函数处理所有缓冲:2)每次一行 ...