DRAM(动态)存储器

一、DRAM的存储元电路

常见的DRAM存储元电路有四管式和单管式两种,它们的共同特点是靠电容存储电荷的原理来存储信息。电容上存有足够多的电荷表示“1”,电容上无电荷表示“0”。 由于电容存储的电荷会逐渐泄漏,即使电源不掉电,信息也会很快消失,应用中需要定时恢复存储的电荷。与SRAM相比,DRAM具有集成度高,功耗低等特点,目前被广泛应用于各类计算机中。

四管DRAM存储元

二、

刷新操作:由于存储的信息电荷终究是有泄漏的,时间久了,信息就会丢失。为此,必须设法由外界按一定规律不断给栅极进行充电,补足栅极的信息电荷,这就是所谓“再生”或“刷新”。

设原存信息为“1”,T1管截止,T2管导通。若经过一段时间,T2管栅极上漏失一部分信息电荷,使A端的电压稍小于存“1”时的满值电压。此时,在字选择线上加脉冲,T5、T6开启,A端与位线D相连,从而充电到满值电压,刷新了原存“1”的信息。因此,定时给全部存储单元电路执行一遍读操作,就可以实现信息再生。

三、单管DRAM存储元

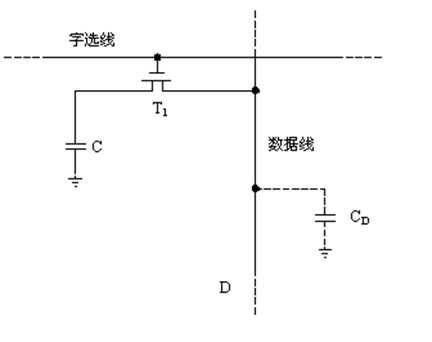

为提高芯片的存储密度,现在动态RAM芯片中一般采用图4-9所示的单管动态存储元电路,其中T1管为字选控制管,字选线有效(高电位)使其导通。

读操作:字选择线为“1”,使T1管导通。若原存“1”,则C上电荷通过T1管向位线(数据线)泄放,通过读出放大器形成读“1”信号。反之,若原存“0”,则无泄放电流。因为读出时C电荷泄放,电位下降,所以是破坏性读出,在读出后应有重写操作。

写操作:字选择线为“1”,使T1管导通。要写“1”,在位线(数据线)上加高电位,经T1管对C充电;写“0”则在数据线上加低电位,使CD上无电荷。

刷新操作:由于MOS管栅极电容上存储的电荷会缓慢泄放,超过一定时间(2~3.3ms),就会丢失信息。因此必须定时给栅级电容补充电荷,进行“刷新”操作。

单管DRAM存储元电路

四、DRAM存储器芯片的读/写周期

读周期

DRAM的读周期时序如图4-11(a)所示。

为了使芯片能正确地接收行、列地址并实现读操作,各信号的时间关系应符合下面的要求:行地址必须在RAS#信号有效之前送到芯片的地址输入端;CAS#信号应滞后RAS#一段时间,并滞后于列地址送到芯片地址输入端的时间;RAS#、CAS#应有足够的宽度;WE#信号为高,并在CAS#有效之前建立。

图为DRAM时序

写周期

DRAM的写周期时序如图4-11(b)所示。

有两点需要说明一下:

1、WE#信号为低,并在信号CAS#有效之前建立。

2、数据必须在CAS#有效之前出现在DIN端。

五、DRAM的刷新

刷新的实质是先将原存信息读出,再由刷新放大器形成原信息并重新写入的再生过程。由于存储元被访问是随机的,有可能某些存储元长期得不到访问,无读出也就无重写,其原信息必然消失。为此,必须采用定时刷新的方法,规定在一定的时间内,对DRAM的全部存储元电路做一次刷新,这一段时间间隔叫做刷新周期,或叫再生周期,一般取2ms、4ms或8ms。

DRAM(动态)存储器的更多相关文章

- [CSAPP笔记][第六章存储器层次结构]

第六章 存储器层次结构 在简单模型中,存储器系统是一个线性的字节数组,CPU能够在一个常数访问每个存储器位置. 虽然是一个行之有效的模型,但没有反应现代系统实际工作方式. 实际上,存储器系统(memo ...

- 简单介绍nandflash、norflash、ram、sram、dram、rom、eeprom、flash的差别

1.nandflash Nandflash是IO设备,数据.地址.控制线都是共用的,须要软件区控制读取时序, 所以不能像nor flash.内存一样随机訪问,不能EIP(片上执行).因此不能直 ...

- 第22章 常用存储器介绍—零死角玩转STM32-F429系列

第22章 常用存储器介绍 全套200集视频教程和1000页PDF教程请到秉火论坛下载:www.firebbs.cn 野火视频教程优酷观看网址:http://i.youku.com/firege ...

- int指令

body, table{font-family: 微软雅黑; font-size: 13.5pt} table{border-collapse: collapse; border: solid gra ...

- 深入解析内存原理:RAM的基本原理

1. 寻址原理概述RAM 主要的作用就是存储代码和数据供CPU 在需要的时候调用.但是这些数据并不是像用袋子盛米那么简单,更像是图书馆中用有格子的书架存放书籍一样,不但要放进去还要能够在需要的时候准确 ...

- 【ARM】arm系列知识框架

[ARM编程模型] 硬件: 电路原理图 软件: 体系结构, 指令集, 寄存器组 [ARM编程技术] 汇编/C语言 编译, 链接, 烧写和调试 windows: MDK linux : gcc [AR ...

- 【CSAPP】一、计算机系统漫游

一.位+上下文 文本文件 / 二进制文件: 文本文件是只由ASCII码构成的文件 二.从源代码到可执行文件的顺序 源代码 ——> 可执行文件(机器代码)共有四步: 全过程代码 gcc hello ...

- 系统启动时,BIOS与影子内存_5

问题:“当我们按下电源开关时,电源开始供电,芯片组撤去RESET信号,CPU马上就从地址FFFF0H处开始执行指令,这个地址在系统BIOS的地址范围内,无论是Award BIOS还是AMI BIOS, ...

- FPGA第一篇:SRAM工作原理

一.SRAM概述 SRAM主要用于二级快速缓存(Level2 C ache). 它利用晶体管来存储数据.与DRAM相比,SRAM的速度快,但在同样面积中SRAM的容量要比其它类型的内存小. 大部分FP ...

- 【CUDA 基础】4.1 内存模型概述

title: [CUDA 基础]4.1 内存模型概述 categories: - CUDA - Freshman tags: - CUDA内存模型 - CUDA内存层次结构 - 寄存器 - 共享内存 ...

随机推荐

- 部署rails遇到问题

underfined method for has_attched_file when installing paperclip 解决 create the file paperclip.rb ins ...

- 使用单体模式设计原生js插件

----------基于上次写的jquery插件进行改造 http://www.cnblogs.com/GerryOfZhong/p/5533773.html 背景:jQuery插件依赖jQuery ...

- win10+GTX1080+Tensorflow1.6安装

安装参考网站:http://blog.csdn.net/lp654063449/article/details/79340655 依照安装目录依次安装,所需安装包均已下载,在最后的一步中,打开cuda ...

- 10 阻塞队列 & 生产者-消费者模式

原文:http://www.cnblogs.com/dolphin0520/p/3932906.html 在前面我们接触的队列都是非阻塞队列,比如PriorityQueue.LinkedList(Li ...

- cnblog博客停用

本博客从今日起停止更新,后续的文章将会发布在新的博客mrbackkom.github.io

- Datenstruktur und Algorithmus

In der Informatik und Softwaretechnik ist eine Datenstruktur ein Objekt zur Speicherung und Organisa ...

- 远程服务通讯Service(Remote--AIDL)

服务端代码:https://github.com/maogefff/AndroidTest/tree/develop-ServiceLocal2 客户端代码:https://github.com/ma ...

- CodeIgniter 目录结构详解

1. myshop 2. |-----system 框架程序目录 3. |-----core 框架的核心程序 4. |-----CodeIgniter.php 引导性文件 5. |-----Commo ...

- DataGrridView 当前行显示不同颜色

如果想让选中DataGridview的行显示不同颜色,就要通过DataGridview控件RowPerpaint事件中重新设置所选行的DefauleCellStyle属性来实现 private voi ...

- thinkphp htmlspecialchars_decode

一 百度编辑器 与 htmlspecialchars_decode *Thinkphp百度编辑器 存的时候为了安全把进行了字符转换,数据库: <p> 测试测试</ ...