14-Verilog for Verification

Verilog for Verification

1.引言

Testbench也是一个模块(module...endmodule)

Testbench没有输入和输出,因为它是一个闭环,自己产生激励,灌给module,module输出响应,testbench会捕捉响应,进行比较,自己在自己内部形成闭环

完成对待测设计的例化,测试代码的封装,提供测试激励,收集测试结果

无需综合,行为级描述优先

module module_name_tb;

//测试代码

endmodule

2.变量声明

- 给待测设计的输入端口提供激励

- 通过待测实际的输出端口收集激励

- 提供激励的信号:reg类型信号进行声明,便于在initial和always中进行赋值

- 收集激励的信号:reg或wire,多数情况下使用wire

- 也可以使用logic变量进行声明

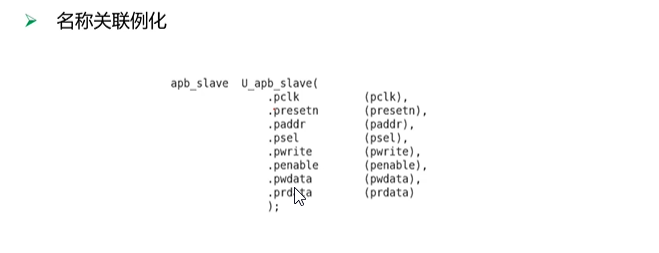

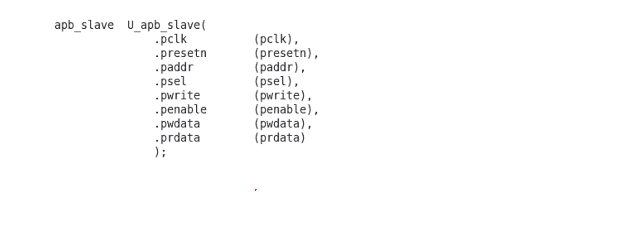

// 名称关联的方式

apd_slave U_apb_slave(

.pclk (pclk),

.prestn (prestn),

.paddr (paddr),

.psel (psel),

.pwrite (pwrite),

.penable (penable),

.pwdata (pwdata),

.prdata (prdata)

);

3.激励

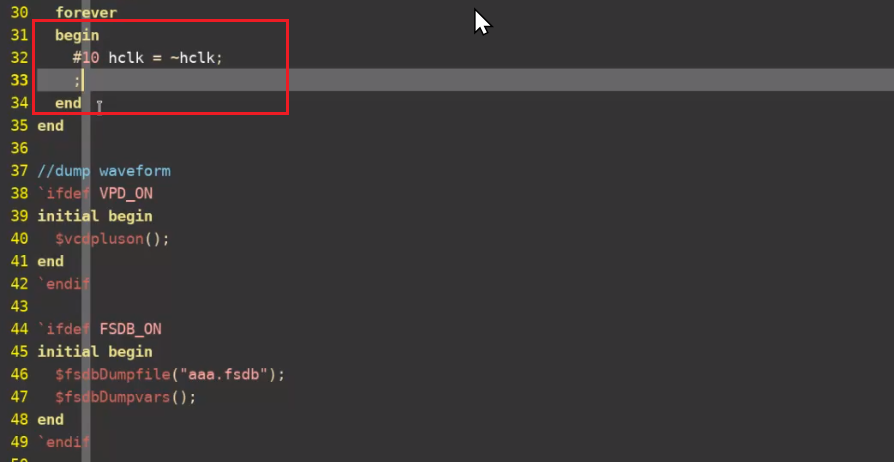

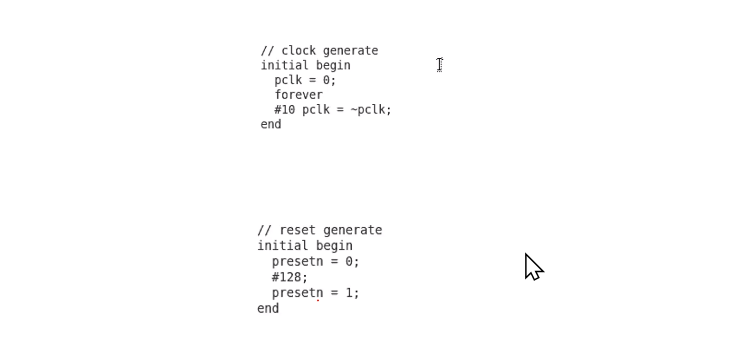

3.1 时钟产生

- forever语句,必须写在initial中

- forever后面执行多条语句,加begin end

// clock generate

initial begin

pclk = 0;

forever

begin

#10 pclk = ~pclk; // 时钟周期是20个时间单位

end

3.2 reset信号

- 低电平有效

- 在某个时间点将reset置为0

reg rst_n;

initial begin

rst_n = 1'b0; // 复位信号置为低电平

#45;

rst_n = 1'b1; // 延迟45个时间单位之后,将复位撤销

end

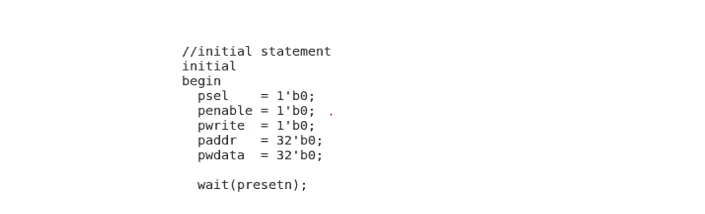

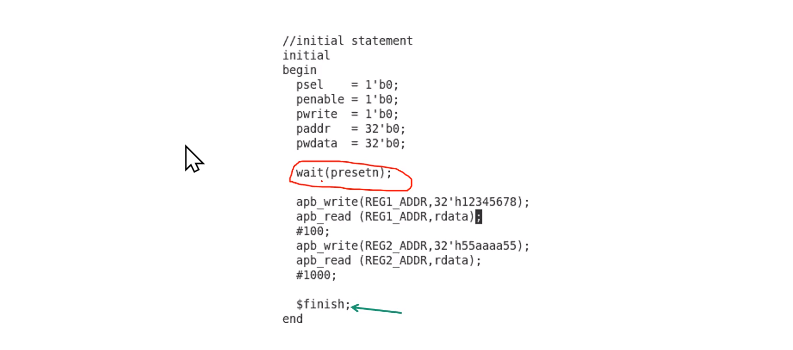

3.3 产生激励

- wait(条件表达式),条件表达式为真的时候解除等待

initial begin

......

wait(rst_n = 1'b1);

wait(sim_start)

......

end

- @(posegde clk) ...

initial

begin

.....

wait(rst_n = 1'b1);

wait(sim_start);

@(posedge pclk);

a = 1'b1;

end

initial

begin

.....

wait(rst_n = 1'b1);

wait(sim_start);

@(posedge pclk);

#3; // 寄存器d到q端的延迟

a = 1'b1;

end

- function是不能有延迟信息语句的

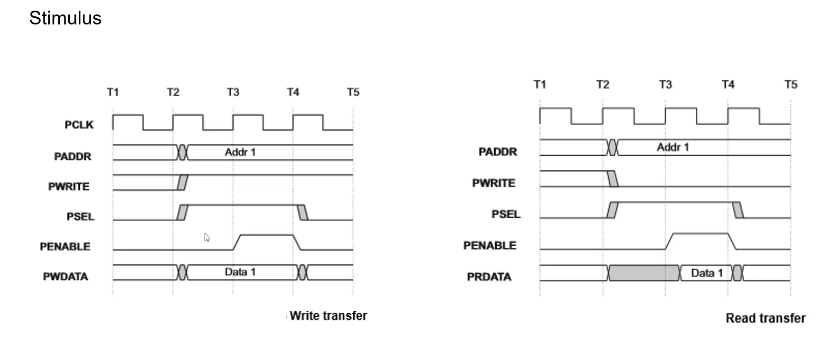

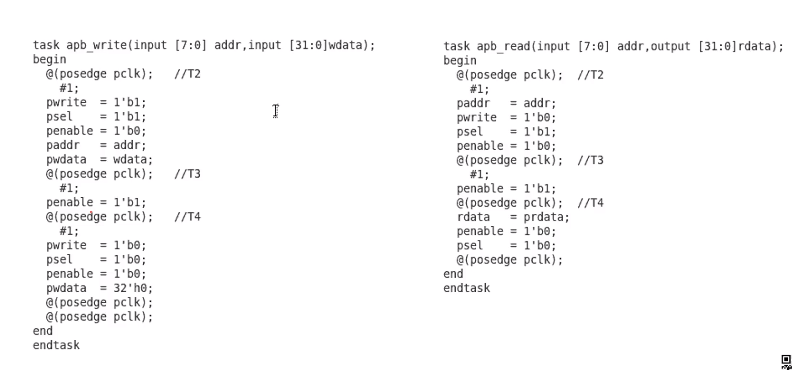

- task是可以具有延迟信息语句的

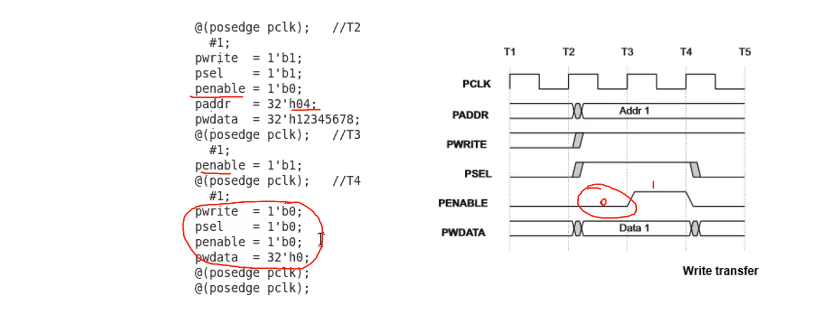

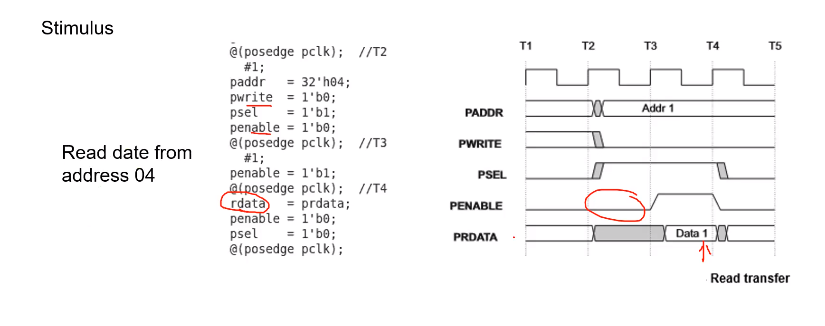

- 将读写操作封装成task

task apb_write(input [31:0] addr,input [31:0] wdata);

begin

end

endtask

task apb_read(input [31:0] addr,output [31:0] rdata);

begin

end

endtask

reg [31:0] memory [1024:0]

FILE0 = $open("block90");

for(address=32'h0,address<32'h80;address=address+1)

$fwriteh(FILE0,32'hFFFFFFFF,"\n")

$fclose(FILE0)

$readmemh("block0",memory);

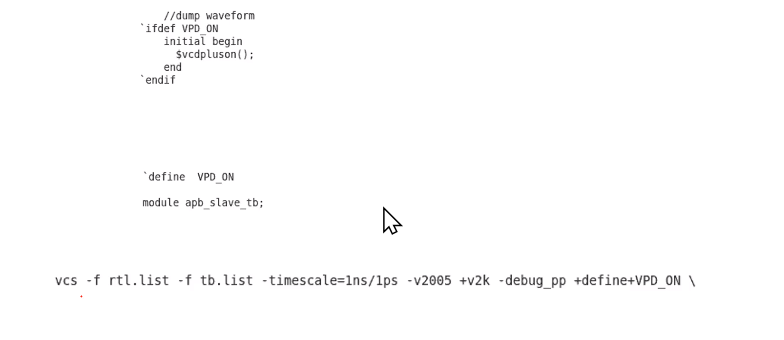

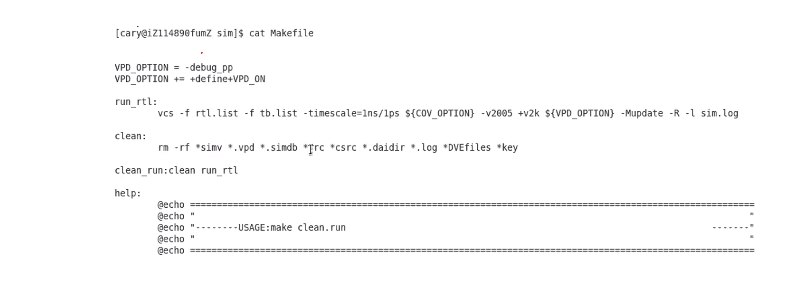

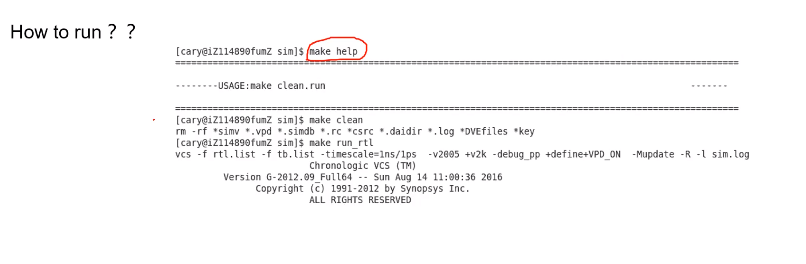

3.4 dump 波形

`ifdef VPD_ON

initial begin

$vcdpluson();

end

`endif

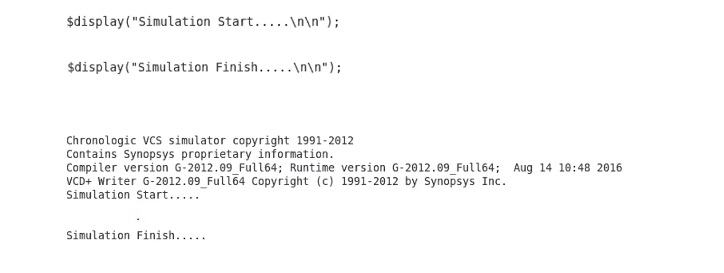

3.5 显示激励

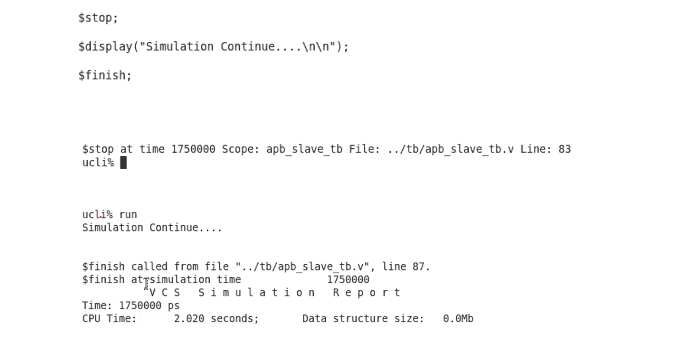

3.6 结束仿真

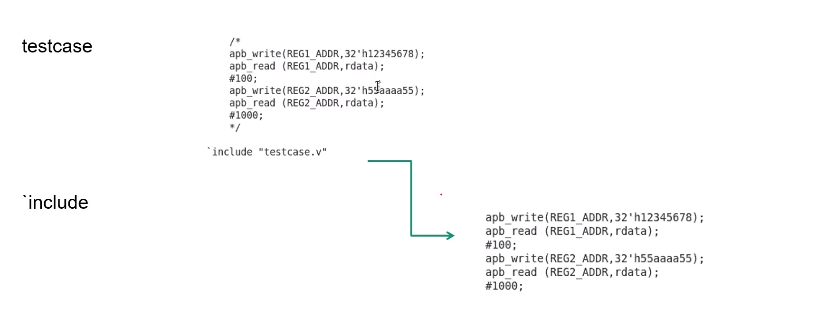

3.7 预编译

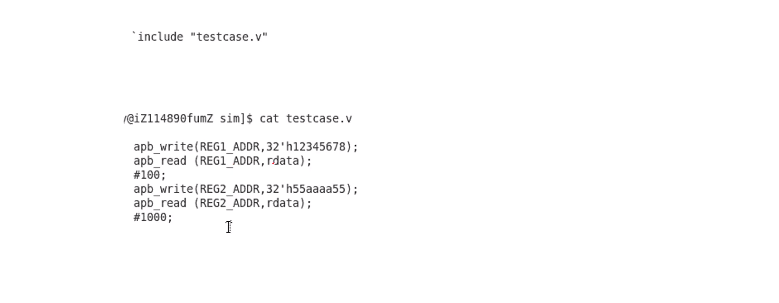

3.8 include

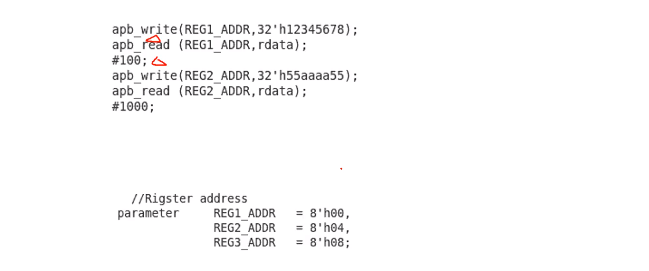

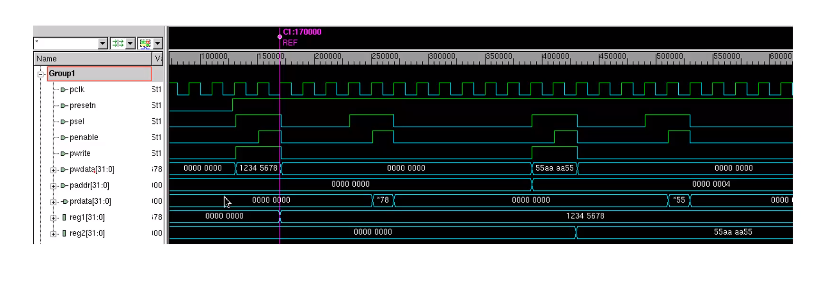

4.实例

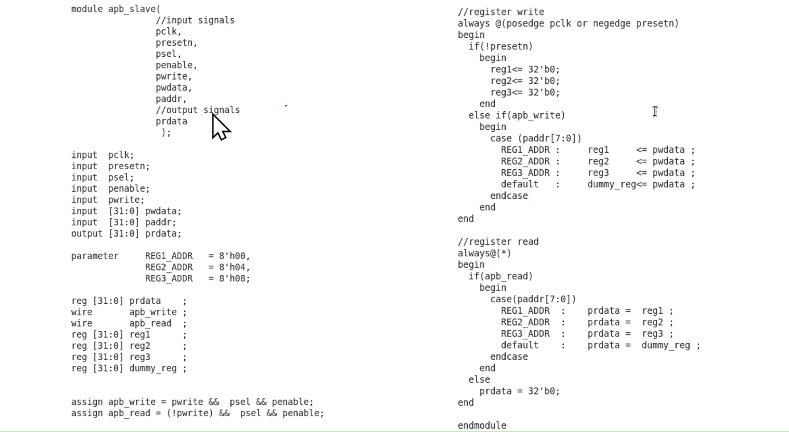

4.1 设计代码

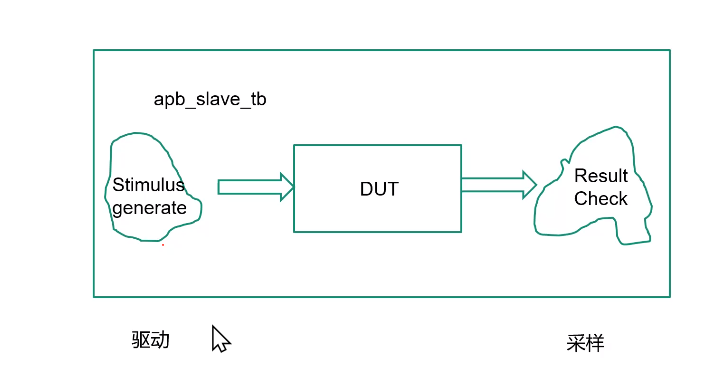

4.2 验证流程

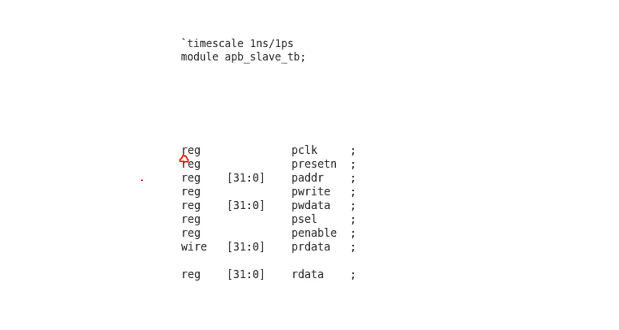

4.3 APB Slave testbench

- testbench中输入定义为reg,输出定义为wire

- 例化模块

- 产生时钟和复位

- 产生激励,产生激励的时候要给模块的输入一定的初始值,不给初始值就会产生x态

14-Verilog for Verification的更多相关文章

- Team Foundation Server 2013 with Update 3 Install LOG

[Info @10:14:58.155] ====================================================================[Info @ ...

- SpringBoot+mybatis:报错Fri Oct 19 14:29:24 CST 2018 WARN: Establishing SSL connection without server's identity verification is not recommended. According to MySQL 5.5.45+, 5.6.26+ and 5.7.6+ requiremen

报错:Fri Oct 19 14:29:24 CST 2018 WARN: Establishing SSL connection without server's identity verifica ...

- Xilinx ISE 14.1利用Verilog产生clock

<一>建立如下的Verilog Module module myClock( input clock ); endmodule <二>建立 Verilog Test Fixtu ...

- Verilog Tips and Interview Questions

Verilog Interiew Quetions Collection : What is the difference between $display and $monitor and $wr ...

- 【设计经验】5、Verilog对数据进行四舍五入(round)与饱和(saturation)截位

一.软件平台与硬件平台 软件平台: 操作系统:Windows 8.1 64-bit 开发套件:Vivado2015.4.2 Matlab2016a 仿真工具:Vivado自带仿真器 二.引言 在利用 ...

- Verilog对数据进行四舍五入(round)与饱和(saturation)截位

转自https://www.cnblogs.com/liujinggang/p/10549095.html 一.软件平台与硬件平台 软件平台: 操作系统:Windows 8.1 64-bit 开发套件 ...

- verilog FAQ(zz)

1. What is the race condition in verilog? Ans :The situation when two expressions are allowed to exe ...

- system verilog的一些总结(从其他博客复制来的)

转载自 http://blog.sina.com.cn/s/blog_e7fec2630101f5t9.html SystemVerilog是一种硬件描述和验证语言(HDVL),它基于IEEE 136 ...

- FPGA Verilog HDL 系列实例--------步进电机驱动控制

[连载] FPGA Verilog HDL 系列实例 Verilog HDL 之 步进电机驱动控制 步进电机的用途还是非常广泛的,目前打印机,绘图仪,机器人等等设备都以步进电机为动力核心.那么,下面我 ...

- Verilog语法基础讲解之参数化设计

Verilog语法基础讲解之参数化设计 在Verilog语法中,可以实现参数化设计.所谓参数化设计,就是在一个功能模块中,对于一个常量,其值在不同的应用场合需要设置为不同的置,则将此值在设计时使用 ...

随机推荐

- 微软成为PostgreSQL主要贡献者

微软成为PostgreSQL主要贡献者 微软对PostgreSQL贡献的很多新功能都来自于客户在使用微软Azure上的PostgreSQL管理实例数据库,所以这些新功能都来自于真实的客户需求 微软对P ...

- linux文件和文件夹的筛选、查找及用户和组管理命令

1.列出当前系统上所有已经登陆的用户的用户名, 注意:同一个用户登录多次,则只显示一次即可. 查看系统用户的命令为: (1)getent passwd 查看系统上的所有用户信息 (2)w 查看登录用户 ...

- Luogu P1298 最接近的分数 做题记录

算是水紫,不过也学到一些有用的东西. 题意 给定正小数 \(N\).求分子不大于 \(n\),分母不大于 \(m\) 的分数 \(\dfrac{n}{m}\),使得 \(\dfrac{n}{m}\) ...

- docker: 'buildx' is not a docker command

解决方法 sudo apt install docker-buildx-plugin

- 日常Bug排查-集群逐步失去响应

前言 日常Bug排查系列都是一些简单Bug排查.笔者将在这里介绍一些排查Bug的简单技巧,同时顺便积累素材_ Bug现场 最近碰到一个产线问题,表现为某个应用集群所有的节点全部下线了.导致上游调用全部 ...

- antd5中文设定

antd5中文设定 import zhCN from "antd/lib/locale/zh_CN" <ConfigProvider locale={zhCN} theme= ...

- 在云南,我用华为云AI开发出千万级用户的应用

摘要:创造无限,当"燃"是开发者,华为云1024程序员节,陶新乐和大家分享独立开发者的自由之路. 本文分享自华为云社区<在云南,我用华为云AI开发出千万级用户的应用>, ...

- 一文详解Java日志框架JUL

摘要:JUL(Java util logging),Java原生日志框架,不需要引入第三方依赖包,使用简单方便. 本文分享自华为云社区<Java 日志框架 JUL 详解大全>,作者: 陈皮 ...

- 云小课|CDN第5课 CDN入门之—我的网站可以用CDN加速吗?

摘要:CDN(Content Delivery Network,内容分发网络)通过将源站资源缓存到遍布各地的边缘节点服务器上,用户可以就近获取资源,从而达到加速的效果. 本文分享自华为云社区<[ ...

- 火山引擎 DataLeap 推出全链路智能监控报警平台

更多技术交流.求职机会,欢迎关注字节跳动数据平台微信公众号,回复[1]进入官方交流群 随着大数据开发场景下需要运维管理的任务越来越多,在日常运维中开发者经常会面临以下几个问题: 任务多,依赖关系复杂: ...