初试高云FPGA

前言

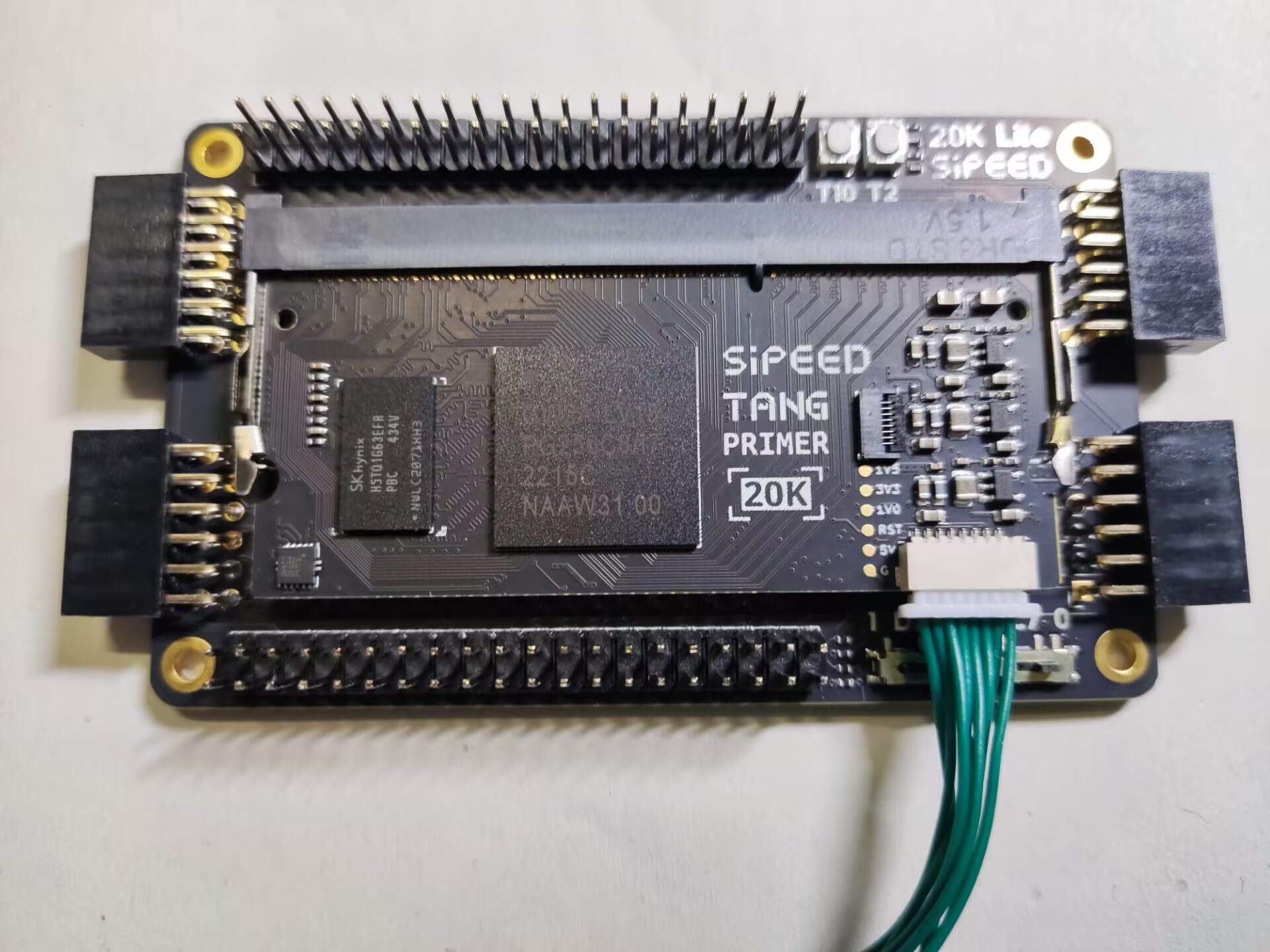

之前一直眼馋Sipeed的Tang系列,正好遇到有工程需要高速控制并行总线,就买了NANO 9K和Primer 20K试试水

买回来先拆的贵的20k,结果发现Sipeed设计师有奇怪的脑回路:

- 核心板没有指示灯,没有集成下载器

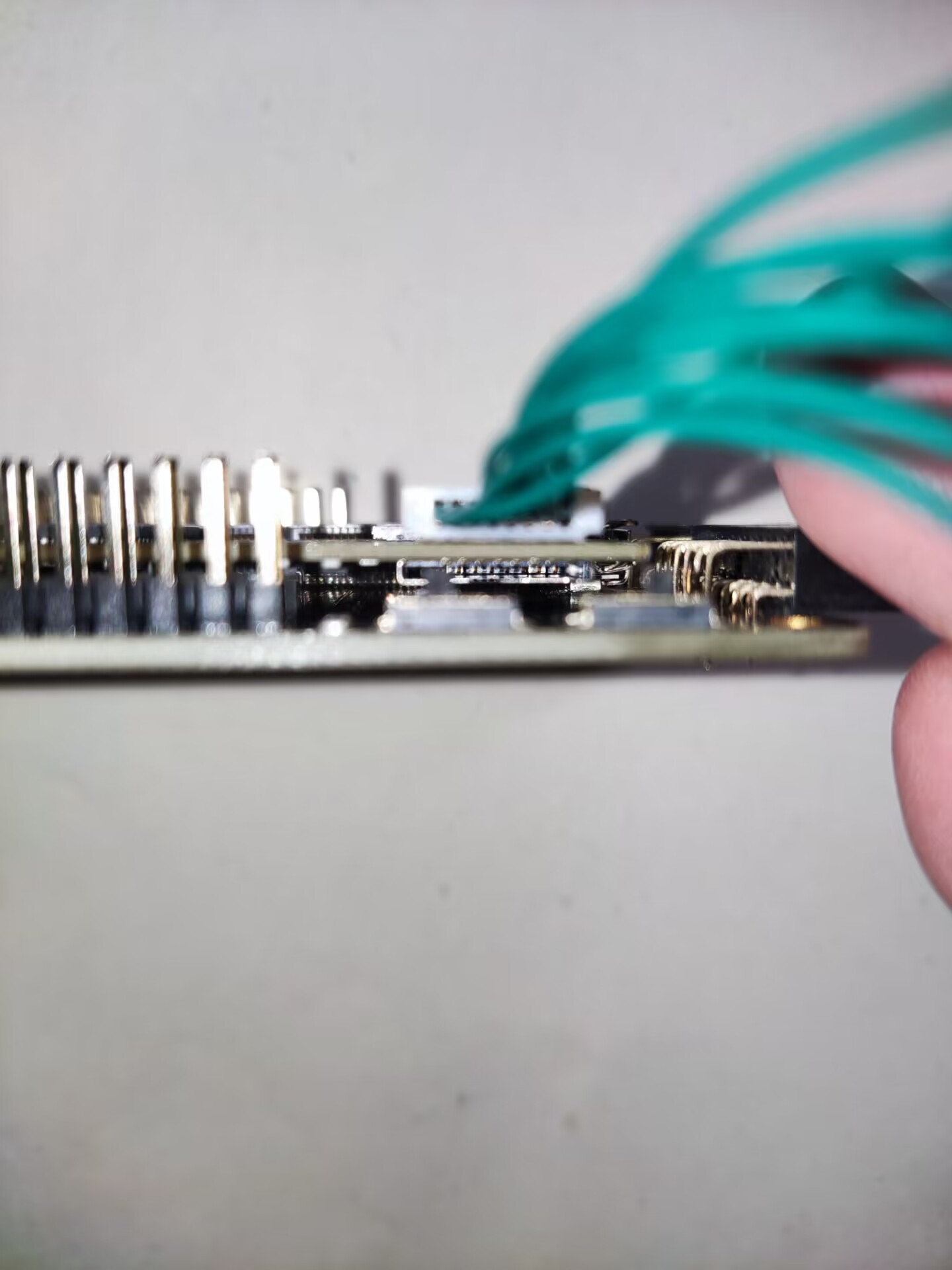

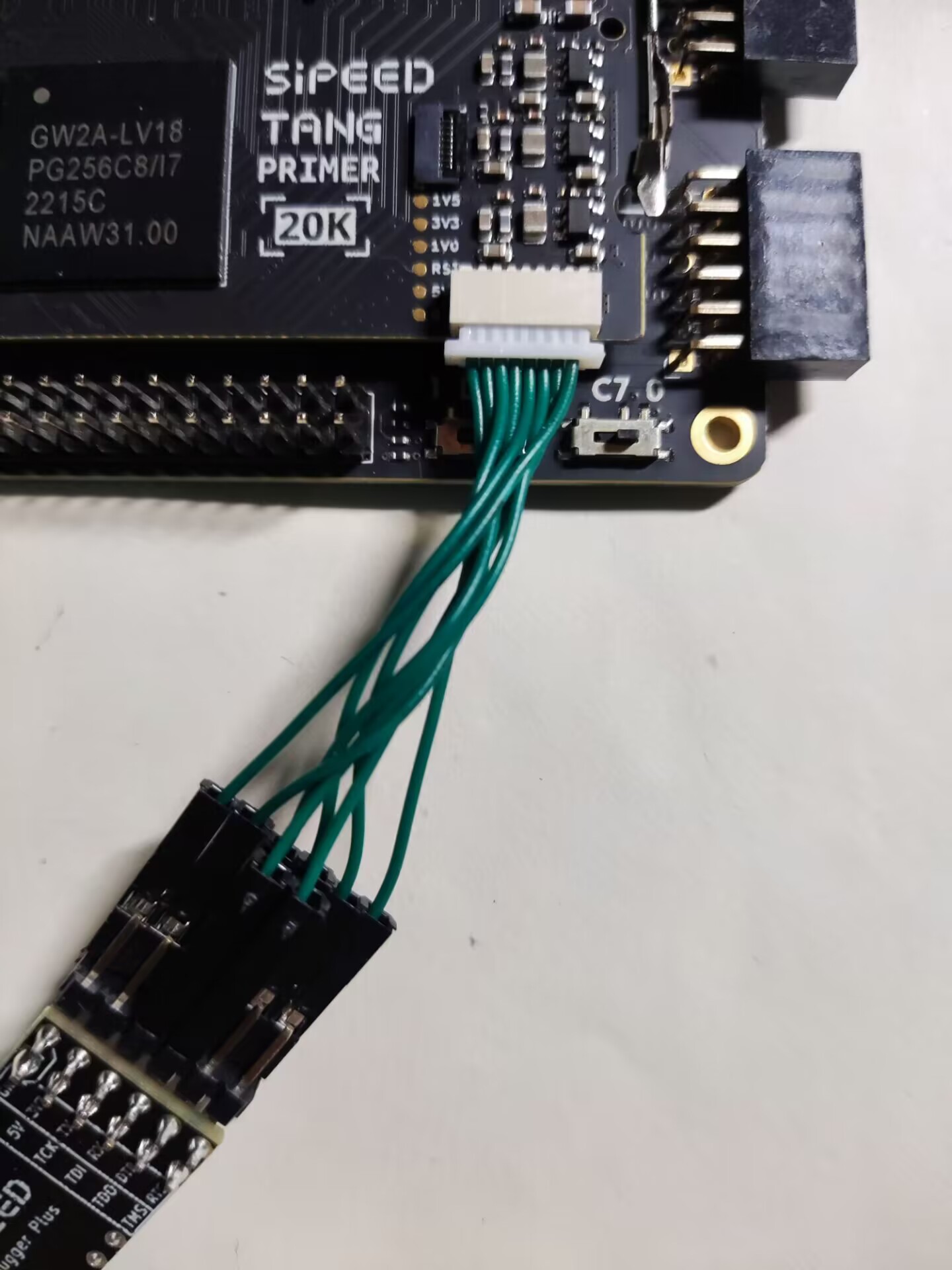

- tf卡在核心板与底板中间藏着,JTAG丝印在背面

- JTAG接口和官方下载器需要扭麻花形式连接

- 调整供电bank需要手动拆除0R电阻。

- 板载晶振27MHz,很奇怪的频率

结果就是失去了调试的兴趣,随便写了个分频器输出1pps脉冲了事。

之后拆了NANO 9K,这个就比20K好用多了,板载一串LED,虽然一些板载资源占用了IO,但还是比较方便调试的。

Sipeed还有个问题就是,例程太少,点灯、点屏幕,没了。好在高云的手册比较多,虽然各个功能的手册是分别发布的,没有系统教程,但好在详细。摸索了一天,算是明白了这个工具要怎么用,因此先写一篇博客记录一下。

软件准备

- 前往高云官网下载软件和各种参考手册。推荐使用教育版,不用申请license。

- 安装下载好的云源软件,我安装的1.9.8.09教育版,有的教程说要另外下载programmer,该版本已自带。软件安装问题可以参考SUG501手册。

- 打开软件,界面功能问题可以参考SUG100手册。

- 新建工程,点灯测试,详见Sipeed点灯例程。

- 综合、约束、下载之类的基础操作在例程中已有详解,这里列一下可能用到的手册

- 综合问题在SUG550

- 约束在SUG935和SUG940

- 下载在SUG502

- 其他高级功能样例在SUG918,所有功能有独立说明手册

所以说高云手册虽然不系统,但好在很详细

IP核调用

IP核怎么调用,没有专门教程参考,仅在SUG100中放了个界面。各各IP核手册中也只是用Verilog或VHDL实例化原语,搞得我这Verilog入门菜鸟一头雾水。在此随手记录一下IP核调用方式。

项目目标

点灯教程中系统时钟来自于板载时钟27MHz,这个时钟我猜测是为了保留3M时钟基频,以便精确PLL出如21M、12M、24M等时钟(那为什么不用21M时钟,还包含7M基频)。

但是我看27MHz不顺眼,于是项目目标就是,利用GW1NR-9C自带的可编程时钟,产生一个25MHz频率,再用这个25MHz进PLL产生100MHz时钟,同时把25MHz用缓冲器输出到引脚上,以检测板子的信号完整性。最后固化到内部Flash,完成烧录与脱机运行。

这样,该项目检测了逻辑单元、IO、IO速率、PLL、CLK,只剩下DSP、SRAM和一些PHY没测试了,之后可以写一个DDS工程,测一下DSP和SRAM。

IP核配置

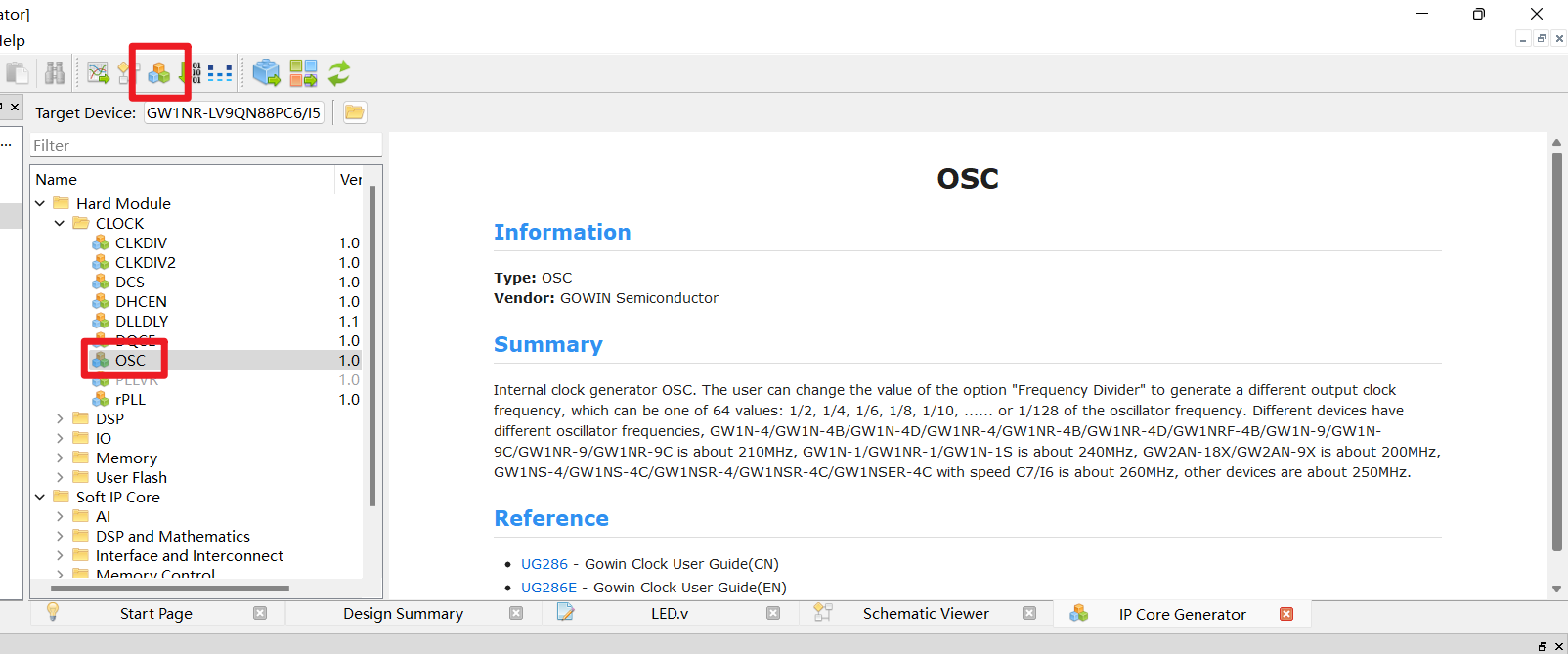

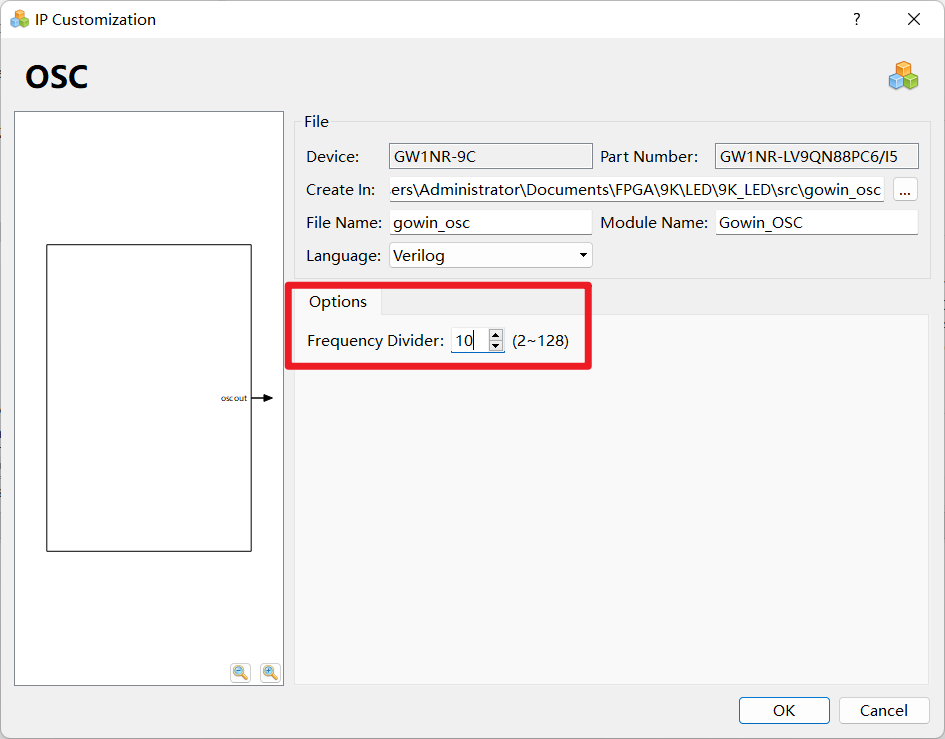

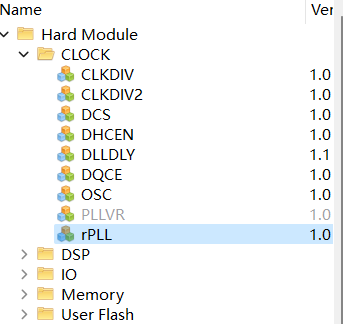

- 首先是打开IP核界面,选择时钟模型,选择OSC,双击

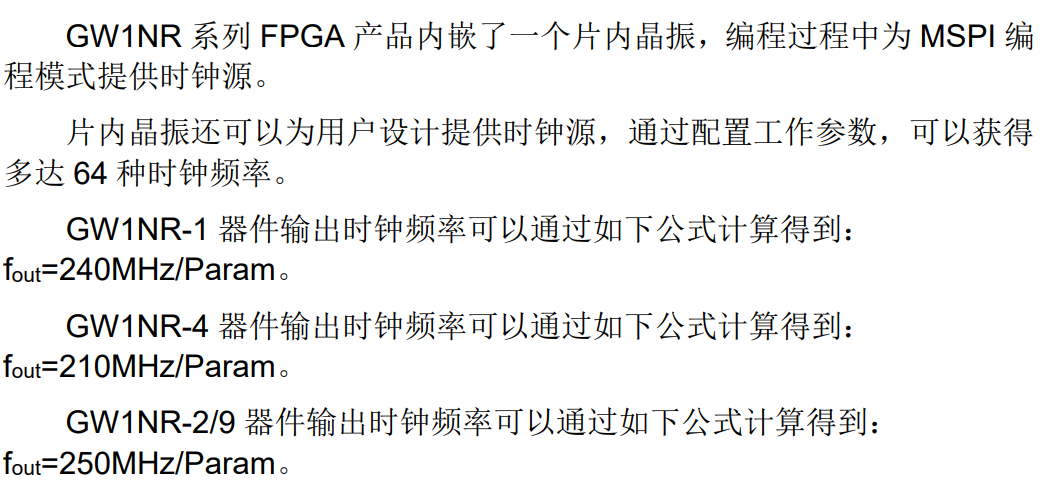

- 可以看到内部可编程时钟的配置是很简单的,只需要填一个分频数就好。该IP核的详细说明见UG286,具体搭载的时钟原频率是多少,不要参考软件中IP核的说明,要参考IC的Datasheet,如GW1NR-9的DS117的晶振时钟章节

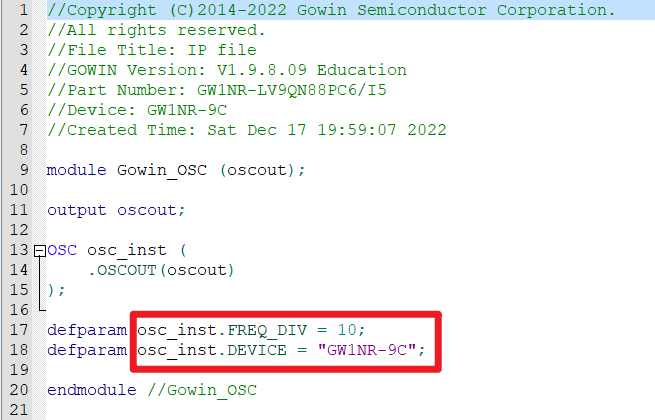

- 软件自动生成verilog文件,自己也可以仿照该文件直接在主模型文件中例化原语。

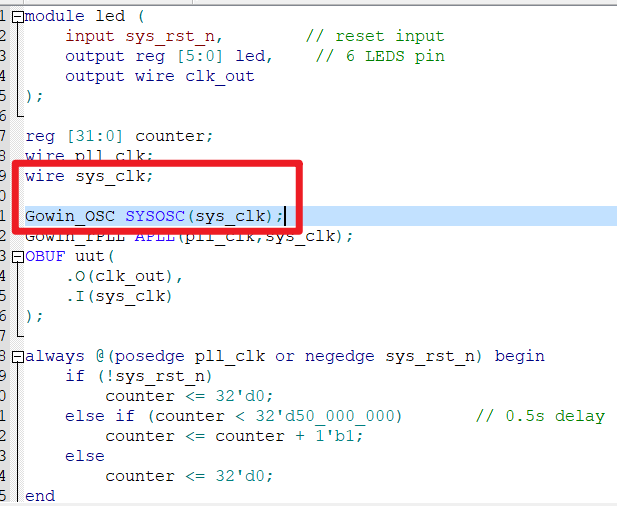

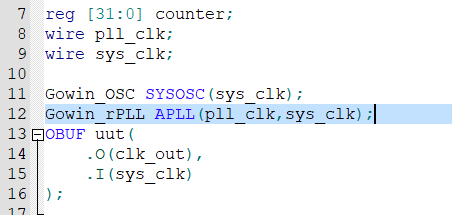

- 在主模型文件中将该OSC模型实例化

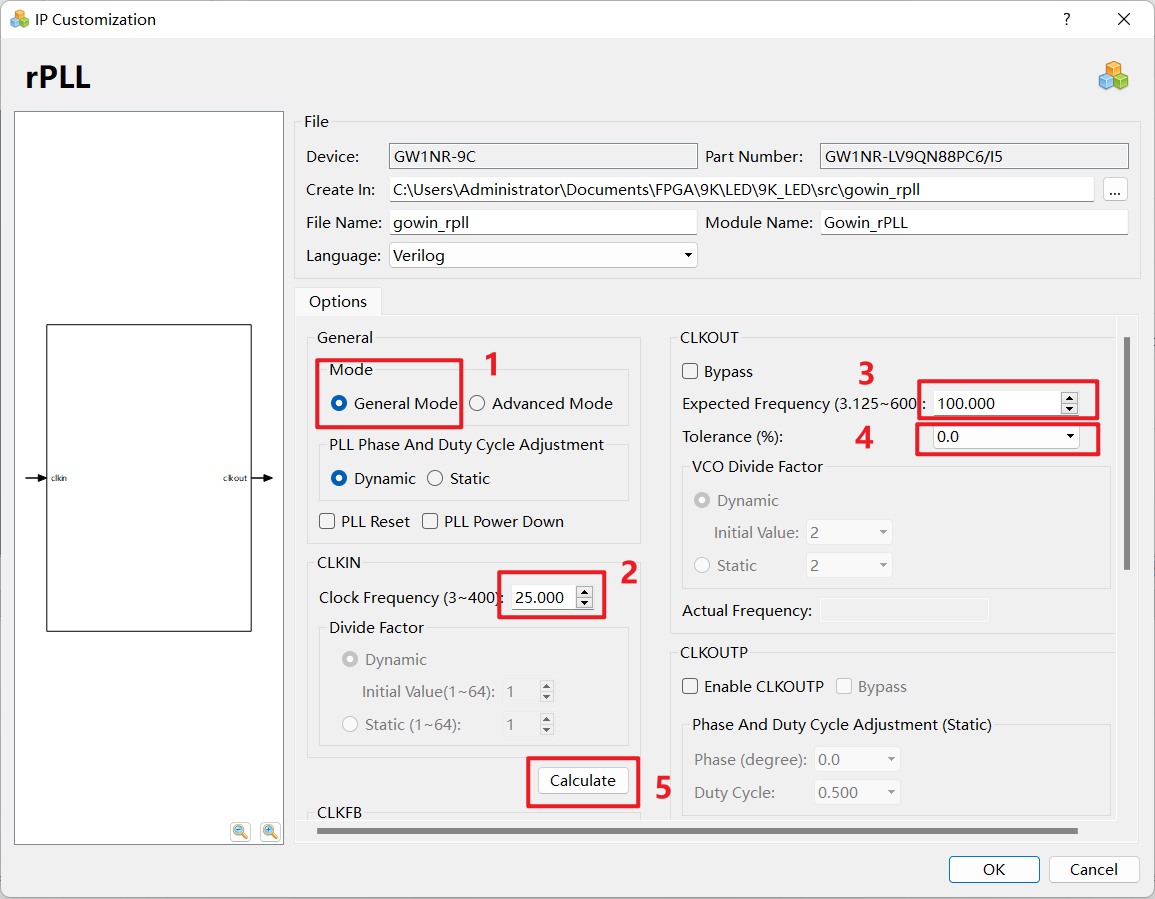

- 接着,在IP核管理界面选择rPLL模块,一般使用普通模式即可,填入输入时钟、输出时钟、误差容忍度,点击计算即可自动配置。需注意,有些需求时钟是不能产生的,或者它自动生成参数后综合软件认为不在VCO适用频率内,这时就需要手动凑数计算了。详细参数计算综合报错时会有,UG286也有计算方法。

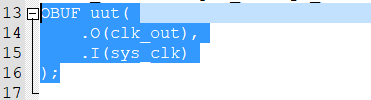

- 在主文件中将该PLL实例化

- 直接在主文件中将25M时钟连到OBUF上,输出带缓冲的clk_out

- 对点灯例子中的一些计数值稍作修改,即可完成代码

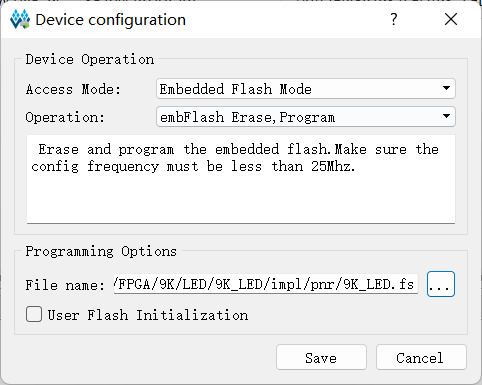

- 综合约束,烧录。烧录选择烧录在内部Flash里,这样可以离线运行

附

代码如下:

module led (

input sys_rst_n, // reset input

output reg [5:0] led, // 6 LEDS pin

output wire clk_out

);

reg [31:0] counter;

wire pll_clk;

wire sys_clk;

Gowin_OSC SYSOSC(sys_clk);

Gowin_rPLL APLL(pll_clk,sys_clk);

OBUF uut(

.O(clk_out),

.I(sys_clk)

);

always @(posedge pll_clk or negedge sys_rst_n) begin

if (!sys_rst_n)

counter <= 32'd0;

else if (counter < 32'd49_999_999) // 0.5s delay

counter <= counter + 1'b1;

else

counter <= 32'd0;

end

always @(posedge pll_clk or negedge sys_rst_n) begin

if (!sys_rst_n)

led <= 6'b111110;

else if (counter == 32'd49_999_999) // 0.5s delay

led[5:0] <= {led[4:0],led[5]};

else

led <= led;

end

endmodule

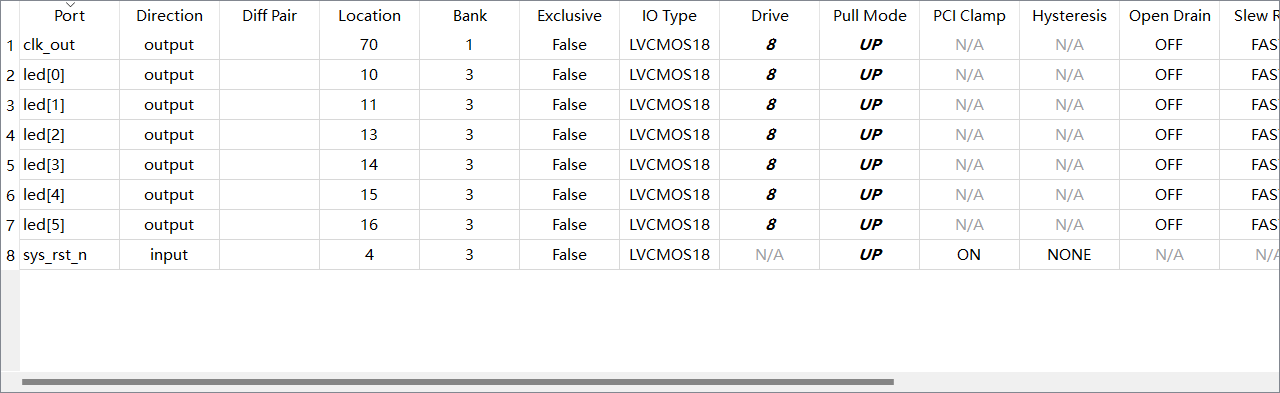

约束:

初试高云FPGA的更多相关文章

- FPGA各大厂商,不可不知

引言: FPGA市场前景诱人,但是门槛之高在芯片行业里无出其右.全球有60多家公司先后斥资数十亿美元,前赴后继地尝试登顶FPGA高地,其中不乏英特尔.IBM.德州仪器.摩托罗拉.飞利浦.东芝.三星这样 ...

- Lattice并购案和我国FPGA发展道路

引用 http://www.cnblogs.com/alifpga/p/9292588.html FPGA作为通信.航天.军工等领域的关键核心器件,是保障国家战略安全的重要支撑基础.近年来,随着数字化 ...

- 了解FPGA市场现状和未来趋势

转, 来源: http://www.sohu.com/a/204640373_740053 可编程的“万能芯片” FPGA——现场可编程门阵列,是指一切通过软件手段更改.配置器件内部连接结构和逻辑单元 ...

- Lattice并购案&我国FPGA发展路径

FPGA作为通信.航天.军工等领域的关键核心器件,是保障国家战略安全的重要支撑基础.近年来,随着数字化.网络化和智能化的发展,FPGA的应用领域得到快速扩张.美国在FPGA领域拥有绝对的垄断优势,已成 ...

- 从云端到边缘 AI推动FPGA应用拓展

近日,全球最大的FPGA厂商赛灵思宣布收购深鉴科技的消息,引发人工智能芯片行业热议,这也是首起中国AI芯片公司被收购的案例.值得注意的是,收购深鉴科技的赛灵思在2018年下半年重点发展方面是汽车自动驾 ...

- FPGA该如何应对ASIC的大爆发?

有人认为,除了人才短缺.开发难度较大,相比未来的批量化量产的ASIC芯片,FPGA在成本.性能.功耗方面仍有很多不足.这是否意味着,在ASIC大爆发之际,FPGA将沦为其“过渡”品的命运? 安路科技市 ...

- ARM、MCU、DSP、FPGA、SOC各是什么?区别是什么?(转)

ARM ARM处理器是Acorn计算机有限公司面向低预算市场设计的第一款RISC微处理器.更早称作Acorn RISC Machine.ARM处理器本身是32位设计,但也配备16位指令集,一般来讲比等 ...

- 国产FPGA市场分析 该如何破局

2018年上半年对于中国半导体行业而言是多事之秋,发生了几件让国人深入思考的大事.我作为IC产业的逃兵,最近也在思考很多的问题,包括资本市场.集成电路行业和研究所的一些不成熟的想法. 2008年进入华 ...

- 推动FPGA发展箭在弦上,国内厂商须走差异化之路

7月25日,由中国电子报与深圳投资推广署共同举办的“第六届(2018)中国FPGA产业发展论坛”在深圳召开. 作为四大通用集成电路芯片之一,FPGA(现场可编程门阵列)的重要性与CPU.存储器.DSP ...

- 再续FPGA初心,京微齐力脱胎京微雅格重新起航(700万元天使轮,泰有基金领投,水木基金、臻云创投、泰科源跟投。数千万元Pre-A轮融资,领投方为海康基金)

集微网消息,新的一年开启新的希望,新的空白承载新的梦想.这是年初一集微网给读者们拜年时写的寄语.在中国农历新年开年之际,半导体产业里也迎来了许多新的起点.例如长江存储在与苹果就采购前者的Nand闪存芯 ...

随机推荐

- 开心档之MySQL 导入数据

MySQL 导入数据 本章节我们为大家介绍几种简单的 MySQL 导入数据命令. 1.mysql 命令导入 使用 mysql 命令导入语法格式为: mysql -u用户名 -p密码 < 要导入的 ...

- 对话 BitSail Contributor | 梁奋杰:保持耐心,享受创造

2022 年 10 月,字节跳动 BitSail 数据引擎正式开源.同期,社区推出 Contributor 激励计划第一期,目前已有 13 位外部开发者为 BitSail 社区做出贡献,成为了首批 B ...

- ThreadPoolExecutor 使用

ThreadPoolExecutor 介绍 简写: package com.vipsoft.Thread; import java.util.concurrent.*; import java.uti ...

- Socket | 大小端问题和网络字节序转换函数

不同 CPU 中,4 字节整数 1 在内存空间的存储方式是不同的.4 字节整数 1 可用 2 进制表示如下: 00000000 00000000 00000000 00000001 有些 CPU 以上 ...

- #627 DIV3 题解

A. 每组给一个和个数(),每次操作可以给一个加2,求是否能使n个数相等 4 3 1 1 3 4 1 1 2 1 2 11 11 1 100 YES NO YES YES 直接扫一遍,记录最大值与当前 ...

- 2019年第十届蓝桥杯国赛C++A组

蓝桥杯历年国赛真题汇总:Here 最后编辑时间: 2021年5月27日 统一声明 如果不写默认带有常用头文件 如果不表明主函数默认表示在 void solve(){} 默认使用 using names ...

- 彻底解决 gcr、quay、DockerHub 镜像下载难题

在使用 Docker 和 Kubernetes 时,我们经常需要访问 gcr.io 和 quay.io 镜像仓库,由于众所周知的原因,这些镜像仓库在中国都无法访问,唯一能访问的是 Docker Hub ...

- python json.loads()、json.dumps()和json.dump()、json.load()区别

json.loads().json.dumps()和json.dump().json.load()分别是两组不同用法 带s的用于数据类型的转换,不带s的用于操作文件. json.loads().jso ...

- spring--集成RocketMQ

在Spring Boot中集成RocketMQ通常涉及以下步骤: 1. **添加依赖**:首先,需要在项目的`pom.xml`文件中添加RocketMQ的Spring Boot Starter依赖. ...

- std::istringstream的用法

1.概要 std::istringstream 是 C++ 标准库中的一个类,它用于从字符串中提取数据,并将数据转换为不同的数据类型.它通常用于从字符串中解析数据,例如整数.浮点数等.以下是关于 st ...