RV32A指令集

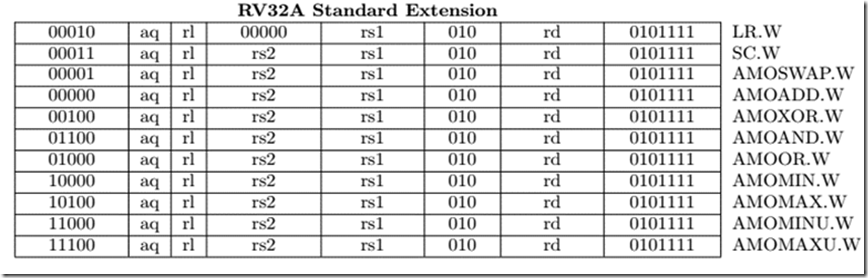

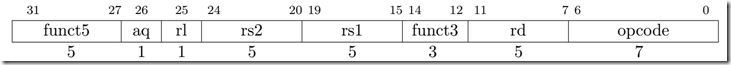

RV32A指令包括两类:AMO(atomic memory operation)指令,Load-Reserved/Store-Conditional指令

| Category | Fmt | RV32I base | machine code(bin) | comment | |

| AMO(atomic memory-operation指令 |

从地址rs1指定的存储器中读出一个数据,存放到rd寄存器中,并且将读出的数据和rs2寄存器中的值进行计算,再将结果写回rs1指定的存储器中。 | R | amoswap.w rd, rs2,(rs1) | 00001[26,aq][25,rl][20-24,rs2][19-15,rs1]010[11-7,rd]0101111 | 将读出的数据与rs2寄存器的值进行互换。 |

| R | amoadd.w rd, rs2,(rs1) | 00000[26,aq][25,rl][20-24,rs2][19-15,rs1]010[11-7,rd]0101111 | 将读出的数据与rs2寄存器的值进行加法操作。 | ||

| R | amoand.w rd, rs2,(rs1) | 01100[26,aq][25,rl][20-24,rs2][19-15,rs1]010[11-7,rd]0101111 | 将读出的数据与rs2寄存器的值进行与运算。 | ||

| R | amoor.w rd, rs2,(rs1) | 01000[26,aq][25,rl][20-24,rs2][19-15,rs1]010[11-7,rd]0101111 | 将读出的数据与rs2寄存器的值进行或操作。 | ||

| R | amoxor.w, rd, rs2,(rs1) | 00100[26,aq][25,rl][20-24,rs2][19-15,rs1]010[11-7,rd]0101111 | 将读出的数据与rs2寄存器的值进行异或操作。 | ||

| R | amomax.w, rd, rs2,(rs1) | 10100[26,aq][25,rl][20-24,rs2][19-15,rs1]010[11-7,rd]0101111 | 将读出的数据与rs2寄存器的值进行(当作有符号数)取最大值操作。 | ||

| R | amomaxu.w rd, rs2,(rs1) | 11100[26,aq][25,rl][20-24,rs2][19-15,rs1]010[11-7,rd]0101111 | 将读出的数据与rs2寄存器的值进行(当作无符号数)取最大值操作。 | ||

| R | amomin.w rd, rs2,(rs1) | 10000[26,aq][25,rl][20-24,rs2][19-15,rs1]010[11-7,rd]0101111 | 将读出的数据与rs2寄存器的值进行(当作有符号数)取最小值操作。 | ||

| R | amominu.w rd, rs2,(rs1) | 11000[26,aq][25,rl]00000[19-15,rs1]010[11-7,rd]0101111 | 将读出的数据与rs2寄存器的值进行(当作无符号数)取最小值操作。 | ||

| Load_Reserved/store-conditional指令 | R | lr.w rd, (rs1) | 00001[26,aq][25,rl][20-24,rs2][19-15,rs1]010[11-7,rd]0101111 | 从rs1指定的存储器地址中读出一个32位数据,结果放入rd中。 | |

| R | lsc.w rd, rs2,(rs1) | 00010[26,aq][25,rl][20-24,rs2][19-15,rs1]010[11-7,rd]0101111 | 向rs1指定存储器地址中写入一个32位数据,数据来自于rs2寄存器。Sc指令不一定能够执行成功,只有满足一下条件,才能执行成功。 1.LR和SC指定成对的访问相同的地址。 2.LR和SC指令之间没有任何其他的写操作(来自任何一个hart)访问过相同的地址。 3.LR和SC指令之间没有任何中断与异常发生。 4.LR和SC指令之间没有任何的MRET指令。 如果执行成功,则向rd寄存器中写回数值0,如果失败,则向rd寄存器中写回一个非0值。如果执行失败,意味着没有真正写入存储器。 |

||

计算机体系结构中的存储器模型(或者说存储器一致性模型)主要分为三类:按序一致性模型,松散一致性模型,释放一致性模型。

更详细存储器一致性介绍请看:https://blog.csdn.net/jfengamarsoft/article/details/70923658?utm_source=blogxgwz2

按序一致性模型就是严格按序模型,如果处理器指令集架构符合按序一致性模型,那么多个处理器核上执行的程序就好像一个单核处理器上顺序执行一样。例如两个处理器核core0,core1,core0上执行了A,B,C,D四条存储器访问指令,core1 上执行了a,b,c,d四条访存指令。按序一致性模型系统上执行这8条指令的效果就好像在一个core上顺序执行了A a B b C c D d的指令流,或者A B a b C c D d,或者其他顺序,总之,只要符合core0和core1程序顺序,即从core0看,是A,B,C,D,从core1看是a,b,c,d的任意顺序都是合法的。

按序一致性模型的两条规则:

1.各个处理器核安装其程序顺序来执行,执行完一条厚启动执行下一条指令,不能改变存储器访问指令的顺序(即便访问的是不同的存储器地址)。

2.从全局看,每一个存储器写指令的操作都需要能够被系统中的所有处理器核同时观测到。就好像处理器系统(包括所有的处理器核)和存储系统之间有一个开关,一次只会连接一个处理器核和存储系统,因此对存储器的访问都是原子的,串行化的。

松散一致性模型:对于不同存储器访问指令,就单核而言,理论上是可以改变其执行顺序的。松散一致性模型允许多核系统中,每个单核改变其存储器访问指令(比如是访问不同的地址)的执行顺序。

松散一致性模型可以通过fence指令,来同步多核之间的存储器访问。在fence之前的所有存储器访问指令,必须比该fence指令之后的所有存储器访问指令先执行。

释放一致性模型进一步支持获取(acquire)释放(release)机制:

定义一种获取acquire指令,它仅屏障其之前的所有存储器访问操作。

定义一种释放release指令,它仅屏障其之后的所有存储器访问。

AMO指令要求整个读出,计算,写回必须为原子性质,就是读出和写回之间,该存储器地址不能被其它进程访问,通常总线会锁定。

AMO指令也可以支持释放一致性模型,可以通过指令中的aq/rl位,来设置获取或释放属性。

amoswap.w rd, rs2,(rs1) 指令不具有获取和释放属性,不具备屏障功能。

amoswap.w.aq rd, rs2,(rs1) 指令具有获取属性,能够屏蔽其之后的所有存储器访问操作。

amoswap.w.rl rd, rs2,(rs1)指令具有释放属性,能够屏蔽其之前的所有存储器访问操作。

amoswap.w.aqrl rd, rs2,(rs1)指令具有获取释放属性,能够屏蔽其之前之后的所有存储器访问操作。

AMO指令实现上锁操作例子:

li t0, 1 #t0寄存器初始值为1

again:

amoswap.w.aq t0, t0, (a0)

bnez t0, again #如果锁中的值非0,意味着当前的锁仍然被其它进程占用,因此从新读取该锁的值。

…

critical section

…

amoswap.w.rl x0, x0,(a0) #写操作完成,向锁中写0

对于RV32A,LR/SC指令访问的地址,必须32位对齐,否则会产生异常,LR/SC指令也支持释放一致性模型,和AMO指令类似。

LR/SC 能够实现lock-free 数据结构.

下面是一个inline的比较交换函数,仅需要3条指令。

# a0 holds address of memory location

# a1 holds expected value

# a2 holds desired value

# a0 holds return value, 0 if successful, !0 otherwise

cas:

lr.w t0, (a0) # Load original value.

bne t0, a1, fail # Doesn’t match, so fail.

sc.w a0, a2, (a0) # Try to update.

jr ra # Return.

fail:

li a0, 1 # Set return to failure.

jr ra # Return.

RV32A指令集的更多相关文章

- Risc-V指令集

https://riscv.org/specifications/ Risc-V文档包括:用户层指令集文档和特权架构文档,下面这两个文件的官网链接. User-Level ISA Specificat ...

- SSE指令集学习:Compiler Intrinsic

大多数的函数是在库中,Intrinsic Function却内嵌在编译器中(built in to the compiler). 1. Intrinsic Function Intrinsic Fun ...

- ARM-汇编指令集(总结)

ARM汇编指令集 指令.伪指令 (汇编)指令: 是机器码的助记符,经过汇编器编译后,由CPU执行. (汇编)伪指令:用来指导指令执行,是汇编器的产物,最终不会生成机器码. 有两种不同风格的ARM指 ...

- iOS------苹果设备处理器指令集(iPhone初代到iPhone5s)

(via 雅香小筑) Arm处理器,因为其低功耗和小尺寸而闻名,几乎所有的手机处理器都基于arm,其在嵌入式系统中的应用非常广泛,它的性能在同等功耗产品中也很出色. Armv6.armv7.armv7 ...

- SSE指令集优化学习:双线性插值

对SSE的学习总算迈出了第一步,用2天时间对双线性插值的代码进行了优化,现将实现的过程梳理以下,算是对这段学习的一个总结. 1. 什么是SSE 说到SSE,首先要弄清楚的一个概念是SIMD(单指令多数 ...

- RISC指令集的五个周期

RISC指令集的五个周期 RISC(reduced instruction set computer,精简指令集计算机)简称为精简指令集.RISC把执行指令的精力主要放在了经常使用的指令上面.本文主要 ...

- x86指令集同频性能提升

x86近5000条指令,迄今为止最复杂的指令集.这里不研究CISC & RISC,也不考虑process制程变化,主要是看最近几代IA架构对于同频率下性能的提升. x86指令集nasm文档 h ...

- CPU指令集

cpu作为一台电脑中的核心,它的作用是无法替代的.而cpu本身只是在块硅晶片上所集成的超大规模的集成电路,集成的晶体管数量可达到上亿个,是由非常先进复杂的制造工艺制造出来的,拥有相当高的科技含量. C ...

- 在UWP应用中加入Cortana语音指令集

本文介绍小娜语音指令集的使用场景,如何将UWP应用接入小娜的语音指令集,使用户直接通过小娜启动应用并使用应用中 一些轻量级的功能.文中以必应词典作为实例讲解必应词典UWP版本是如何接入小娜语音功能的. ...

随机推荐

- odoo权限管理(二.记录管理)

规则保存在ir.rule模型表里,需要设置关联某个模型,关联很多组,访问权限控制和domian. 通过domain_force过滤出的一些记录来执行约束. 例子:经理只能删除状态为'cancel'的客 ...

- 循序渐进学.Net Core Web Api开发系列【10】:使用日志

系列目录 循序渐进学.Net Core Web Api开发系列目录 本系列涉及到的源码下载地址:https://github.com/seabluescn/Blog_WebApi 一.本篇概述 本篇介 ...

- 在mac中调试网页

一.谷歌浏览器 //打开控制台 option + command + j 二.safari浏览器 safari > 偏好设置 > 勾选开发菜单 1.打开控制台 A.可以在网页中右键,检查元 ...

- BZOJ.1011.[HNOI2008]遥远的行星(思路 枚举)

题目链接 设当前为\(i\),令\(j=\lfloor a*i\rfloor\),\(1\sim j\) 即为对\(i\)有贡献的行星,这一区间的答案应为\[f[i]=M_i*\sum_{k=1}^j ...

- hdu Encoding

Encoding Time Limit : 2000/1000ms (Java/Other) Memory Limit : 65536/32768K (Java/Other) Total Subm ...

- 在ASP.NET MVC中实现一种不同于平常的三级联动、级联方式, 可用于城市、车型选择等多层级联场景

三级或多级联动的场景经常会碰到,比如省.市.区,比如品牌.车系.车型,比如类别的多级联动......我们首先想到的是用三个select来展示,这是最通常的做法.但在另外一些场景中,比如确定搜索条件的时 ...

- (Delphi) Using the Disk Cache 使用磁盘缓存

The Chilkat Spider component has disk caching capabilities. To setup a disk cache, create a new dire ...

- Android 之窗口小部件高级篇--App Widget 之 RemoteViews

Android 之窗口小部件高级篇--App Widget 之 RemoteViews 在之前的一篇博文(Android 之窗口小部件详解--App Widget)中,已经介绍了App Widget的 ...

- redis实现异步任务队列

redis实现异步任务队列 先说思路: 将任务对象序列为JSON字符串,然后推入REDIS缓存,这叫入队. 通过独立的工作线程从REDIS拉出一个任务,这叫出队,工作线程将JSON字符串还原为任务对象 ...

- The Topo to Raster tool returns errors 010235 and 010067转

Problem: The Topo to Raster tool returns errors 010235 and 010067 Description The Topo to Raster geo ...