verilog代码 想法验证---与寄存器输出有关

verilog代码 想法验证---与寄存器输出有关

1.

module test_mind(

input wire clk,

input wire reset,

input wire i,

output wire A,

output wire B

); reg reg_A;

always @ (posedge clk or negedge reset)

if(reset)

reg_A <= 'b0;

else if(i)

reg_A <= 'b1;

else

reg_A <= 'b0; reg reg_B;

always @ (posedge clk or negedge reset)

if(reset)

reg_B <= 'b0;

else if(reg_A)

reg_B <= 'b1;

else

reg_B <= 'b0; assign A = reg_A;

assign B = reg_B;

endmodule

2.

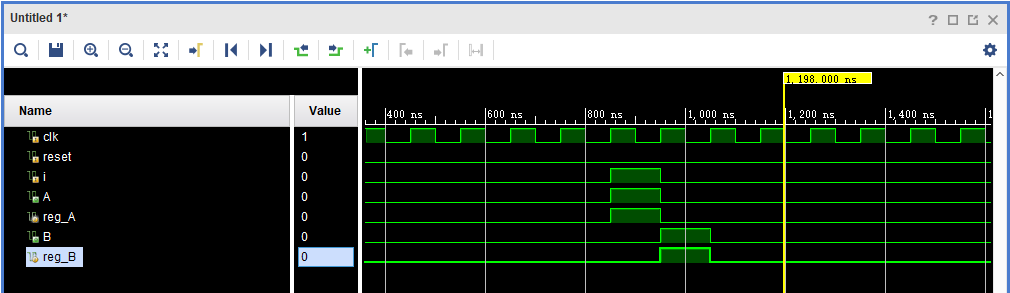

add_force {/test_mind/clk} -radix hex { 0ns} { 50000ps} -repeat_every 100000ps

add_force {/test_mind/reset} -radix hex { 0ns} { 100000ps}

add_force {/test_mind/i} -radix hex { 0ns} { 850000ps} { 950000ps}

3.

4.

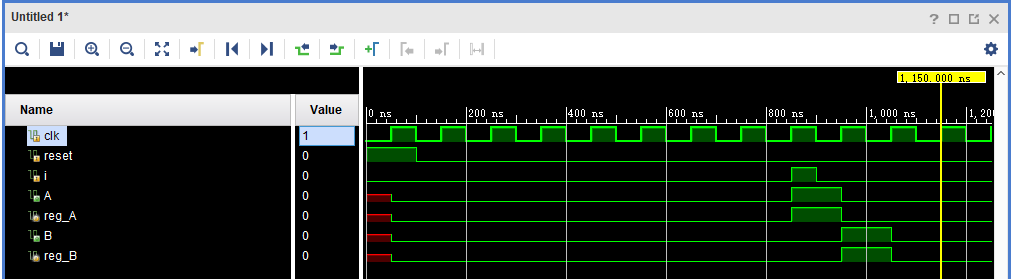

add_force {/test_mind/clk} -radix hex { 0ns} { 50000ps} -repeat_every 100000ps

add_force {/test_mind/reset} -radix hex { 0ns} { 100000ps}

add_force {/test_mind/i} -radix hex { 0ns} { 850000ps} { 900000ps}

5.

结论:1.第二级寄存器还是会比第一级延时一个周期

2.输入信号一点被采集到,即使在一个时钟周期内发生跳变,也不会影响寄存器的输出结果。

verilog代码 想法验证---与寄存器输出有关的更多相关文章

- 学会使用Hdlbits网页版Verilog代码仿真验证平台

给大家推荐一款网页版的 Verilog代码编辑仿真验证平台,这个平台是国外的一家开源FPGA学习网站,通过“https://hdlbits.01xz.net/wiki/Main_Page” 地址链接进 ...

- Verilog代码和FPGA硬件的映射关系(一)

代码和硬件之间的映射关系是一个很奇妙的过程,也展现出人类的智慧.单片机内部的硬件结构都是固定的,无法改变,我们通过代码操作着寄存器的读写,来执行各种复杂的任务.FPGA的硬件结构并不像单片机一样是固定 ...

- verilog 代码分析与仿真

verilog 代码分析与仿真 注意:使用vivado 自带的仿真工具, reg和wire等信号需要赋予初始值 边沿检测 module signal_test( input wire cmos_pcl ...

- 分享:FIFO 同步、异步以及Verilog代码实现

FIFO 很重要,之前参加的各类电子公司的逻辑设计的笔试几乎都会考到. FIFO是英文First In First Out 的缩写,是一种先进先出的数据缓存器,他与普通存储器的区别是没有外部读写地址线 ...

- MVVM架构~knockoutjs系列之验证信息自定义输出

返回目录 这个文章非常重要,也是非常必要的,在我们进行项目开发时,后台无所谓,对样式无要求,而网站前台来说,对样式要求严格,你的验证信息都是前台设计好的,所以,不能使用knockoutjs自带的了,我 ...

- Verilog代码规范I

Verilog代码规范I "规范"这问题 "规范"这个富含专业气息的词汇(个人感觉),其实规范这种东西,就是大家都约定熟成的东西,一旦你不遵守这个东西,专业人士 ...

- 用Sublime Text搭建简易IDE编写Verilog代码

前言 Verilog是一种硬件描述语言(HDL),该语言在Windows上有集成开发环境可以使用,如ModelSim,但ModelSim的编辑器不太好用因此笔者萌生了用Sublime Text3来编写 ...

- 串口接收端verilog代码分析

串口接收端verilog代码分析 `timescale 1ns / 1ps ////////////////////////////////////////////////////////////// ...

- FPGA边沿检测Verilog代码

FPGA边沿检测Verilog代码(上升沿,下降沿,双边沿) 实现思路:用两个一位寄存器直接异或可以实现 代码实现: module edge_detect( input clk, input rs ...

随机推荐

- log4j下载地址及日志文件输入位置配置

ERROR StatusLogger Log4j2 could not find a logging implementation. Please add log4j-core to the clas ...

- maven项目中的pom.xml

需要配置的内容 1.配置头(自动生成) 2.maven项目的坐标(自动生成) <modelVersion>4.0.0</modelVersion> <groupId> ...

- python list和numpy互换

http://blog.csdn.net/baiyu9821179/article/details/53365476

- JavaBasic_10

JVM中的对一个对象的所有初始化动作,是javac在字节码文件中帮我们生成的 1.成员变量的显式初始化 2.初始化代码块(构造代码块) 3.构造方法 初始化静态的东西 在Java中,一个没有方法体的方 ...

- How did I Install DCGAN

https://github.com/carpedm20/DCGAN-tensorflow how to install pillow(python image library) http://www ...

- animate.css动画

添加类名的时间不要只添加动画的类名,也要加上animated,使用的时间可以把自己需要的效果复制出来

- xdoj 1146 (逆向01背包)

背包 有:01背包 逆向背包 多重背包 完全背包 所有的背包都可以根据更新的方向一维实现 amazing?! #include <iostream> #include <cstd ...

- ACM-ICPC 2018 沈阳赛区网络预赛-D:Made In Heaven(K短路+A*模板)

Made In Heaven One day in the jail, F·F invites Jolyne Kujo (JOJO in brief) to play tennis with her. ...

- Install Java on Ubuntu server

准备工作 a) 获得超级用户权限 关于超级用户访问权限的说明: 要将 Java 安装在系统级位置(例如 /usr/java),则必须以超级用户身份登录,从而获得必要的权限.如果您不具有超级用户访问权限 ...

- 【带权并查集】【HDOJ】

http://acm.hdu.edu.cn/showproblem.php?pid=3047 Zjnu Stadium Time Limit: 2000/1000 MS (Java/Others) ...