基于FPGA摄像头图像采集显示系统

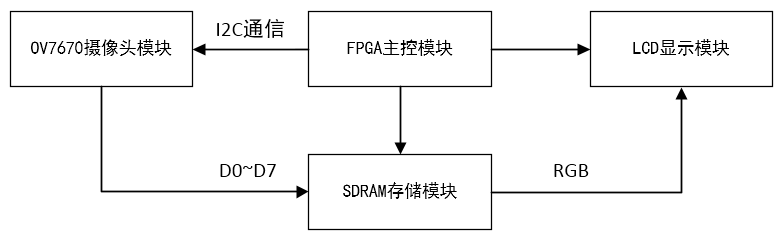

本系统主要由FPGA主控模块、图像采集模块、图像存储模块以及图像显示模块等模块组成。其中图像采集模块选择OV7670摄像头模块,完成对视频图像的采集和解码功能,并以RGB565标准输出RGB 5:6:5信号;图像处理模块选用的FPGA是Altera 公司生产的Cyclone IV EP4CE10F17C8芯片,完成对整个系统的控制,将采集到的视频图像数据处理、存储以及发送到LCD显示屏上。图像存储模块使用256M存储空间的SDRAM进行视频图像数据存储。图像显示模块采用TFT4.3寸LCD液晶显示器显示视频图像。编程语言采用VHDL语言。

由于LCD片内RAM太小,显示不了这么大的分辨率图像,因此,需要将图像数据缓存到SDRAM当中。根据OV7670摄像头VGA格式,即两个字节共16位表示一位像素点。因此,以16位进行缓存到SDRAM当中。本FPGA使用的时钟为50MHZ,芯片EP4CE10F17C8 片内自带4个PLL(锁相环),可以用于分频和倍频。因此,可以通过软件进行设计。分频为25MHZ用于液晶工作时钟,24MHZ用于摄像头工作时钟。倍频为100MHZ用于SDRAM工作时钟。

第一部分摄像头工作原理

OV7670摄像头寄存器配置采用的通信方式为SCCB通信(兼容I2C通信),I2C通信方式和SCCB通信方式非常类似。IIC总线是philips公司推出的新一代串行通信标准总线。它仅靠两根线实现全双工通信:SDA(数据线),SCL(时钟线)。I2C通信方式如下:

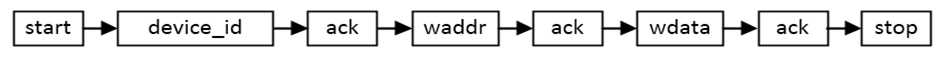

写时序:

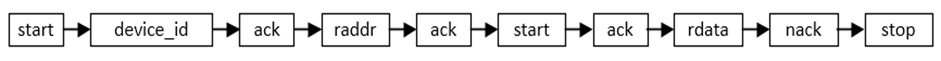

读时序:

I2C时序读写分析:

1、start表示启动总线:在时钟SCL为高电平期间,数据线SDA由高电平拉低,启动I2C总线。

2、device_id:I2C总线是个多主控总线,主机和任何一个从设备之间都可以形成主线,最后一位表示读写操作码,0-写,1-读;(OV7670设备地址为0x42,即0x42为写,0x43为读)。

3、ack:写操作码发送完主机释放总线,从机返回一个应答信号给主机表示写入数据完成。

4、waddr:表示寄存器地址;raddr:表示写对应的寄存器数据

5、wdata:表示写寄存器数据;rdata:表示读对应的寄存器数据。

6、stop:在时钟SCL为高电平期间,数据线SDA由低电平拉高,关闭I2C总线。

7、由于I2C总线支持连续写,故写完地址之后不需要再发送起始信号,读就需要重新发起始信号。

OV7670摄像头的工作原理:

1、首先判断摄像头是否正常工作

通过读取寄存器PID(厂商高位识别号)、VER(厂商低位识别号)、MIDH(厂商识别字节高位)、MIDL(厂商识别字节低位)的默认值来进行判断摄像头是否能够正常工作。

PID地址为:0x0A,默认值为:0x76

VER地址为:0x0B,默认值为:0x73

MIDH地址为:0x0C,默认值为:0x7F

MIDL地址为:0x0D,默认值为:0xA2

2、当摄像头正常工作后,进行摄像头寄存器配置

主要是配置成以下模式:

VGA分辨率(640*480),RGB565模式,水平成像,关闭PLL分频,直接使用外部时,PCLK正常模式,不分屏XCLK=PCLK,不设置彩条等等。

|

寄存器名称 |

地址 |

数据 |

|

MIDH(只读) |

0x0C |

0x7F(判断是否相等) |

|

MIDL(只读) |

0x0D |

0XA2(判断是否相等) |

|

TSLB(写) |

0x3A |

0x04 |

|

COM15 |

0x40 |

0xd0 |

|

COM7 |

0x12 |

0x04 |

|

…………………… |

||

|

COM11 |

0x3b |

0x42 |

通过I2C通信方式,读取寄存器MIDH(厂商识别字节高位)、MIDL(厂商识别字节低位)的默认值来判断摄像头是否正常工作。然后配置寄存器。从寄存器TSLB到寄存器com11,一共配置了166个寄存器(详细请见0V7670摄像头数据手册)。

3、摄像头图像数据的读取

当完成对摄像头寄存器配置后,就可以对摄像头模块进行图像数据的采集。主要通过引脚HREF、VSYNC、PCLK、XCLK以及数据引脚data0~data7来对图像数据进行读取。

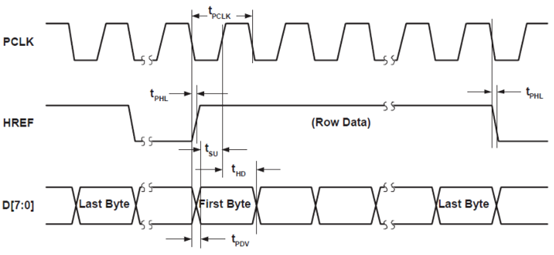

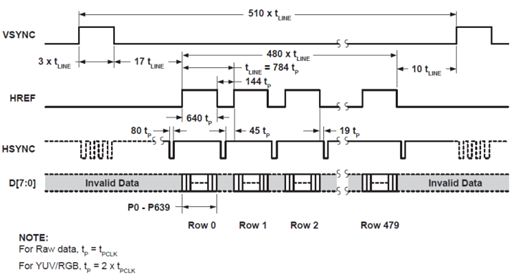

一行图像数据获取时序图如下:

PCLK为像素时钟,一个时钟周期输出一个字节的数据,由于前面将摄像头分辨率配置为RGB565(640*480)格式,因此,前后两个字节组成16位表示一个像素点。由于一行图像数据有640个像素点,故需要读取640*2个像素时钟周期的数才表示一行图像数据获取完成。

一帧图像数据获取时序图如下所示:

根据VGA格式,像素为640*480,因此,需要获取完480行图像数据才表示一帧。

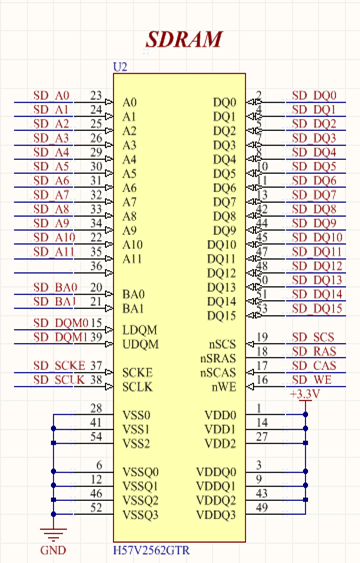

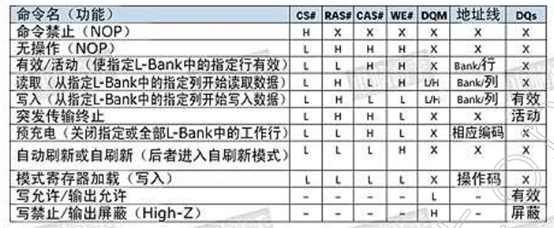

第二部分:SDRAM工作原理

A0~A11:地址线(行列共用地址线),BA0~BA1:用来选择L-BANK的地址线

SCLK:时钟引脚,SCKE:时钟有效引脚

nSCS:芯片选择,nRAS:行地址选通引脚,nSCAS:列选通引脚,WE:写允许

DQ0~DQ15为数据引脚。

SDRAM 并不像SRAM,可以在一个Cycle 内完成一个Access,SDRAM 的Accesses过程分做几个Command,而且通常要3~7 个左右的Cycle 才能完成,我们需要执行一连串的动作才能开始读写:

1)初始化RAM 内的寄存器和存储单元。

2)SDRAM Controller 接收到Data,分析Address,用高位的Address(Row address)进行Active 的动作。

3)SDRAM Controller 用低位Address(Column address) 进行WRITE 或READ。

SDRAM 根据Row address 和Column address 完成读写操作。

由于SDRAM 的电气特性,每隔一段时间存储单元的信息会衰减到无法辨认,所以一段时间之内,要执行Refresh 的动作,以确保信息的正确性,而执行这个动作是依靠Selfrefresh和Auto refresh 两个Command 来完成的。下面具体讲一下每个操作的特点及时序。

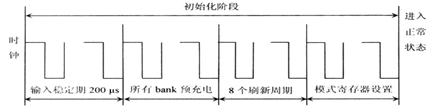

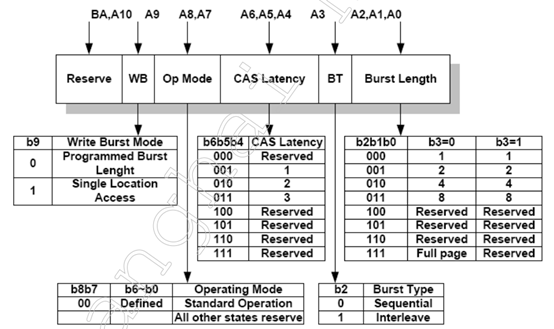

1、芯片初始化

在SDRAM 芯片内部还有一个逻辑控制单元,并且有一个模式寄存器为其提供控制参数。因此,每次上电时(开机时)SDRAM 都要先对这个控制逻辑核心进行初始化。有关预充电和刷新的含义在下文有讲述,关键的阶段就在于模式寄存器(MR,Mode Register)的设置,简称MRS(MR Set),寄存器的信息由地址线来提供。

本设计将模式寄存器配置为BA<=”00”,A<=”000000000000”;即:选择突发读突发写操作模式、潜伏期保留、选择顺序传输的突发传输方式、突发长度为1。配置完成模式寄存器之后,就开始了进入正常的工作状态。

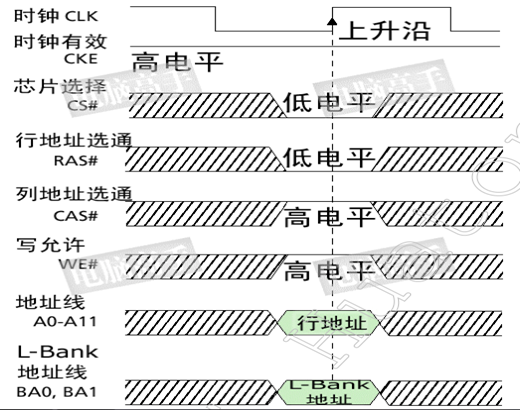

2、行激活有效

初始化完成后,要想对一个L-Bank 中的阵列进行寻址,首先就要确定行(Row),使之处于活动状态(Active),然后再确定列。虽然之前要进行片选和L-Bank 的定址,但它们与行有效可以同时进行。

从图中可以看出,在CS#、L-Bank 定址的同时,RAS(Row Address Strobe,行地址选通脉冲)也处于有效状态。此时An 地址线则发送具体的行地址。如图中是A0-A11,共有12个地址线,由于是二进制表示法,所以共有4096 个行(2^12 =4096),A0-A11 的不同数值就确定了具体的行地址。行地址确定之后,就要对列地址进行寻址了。在SDRAM 中,行地址与列地址线是共用的。

因为没有一个信号是发送读或写的明确命令的,而是通过芯片的可写状态的控制来达到读/写的目的。显然WE#信号就是一个关键。WE#无效时,当然就是读取命令。

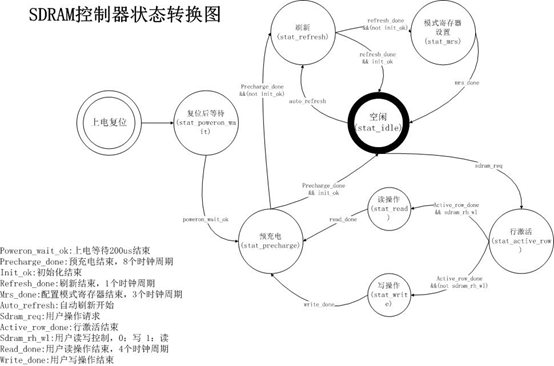

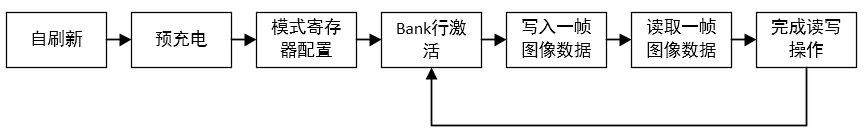

SDRAM工作流程图:

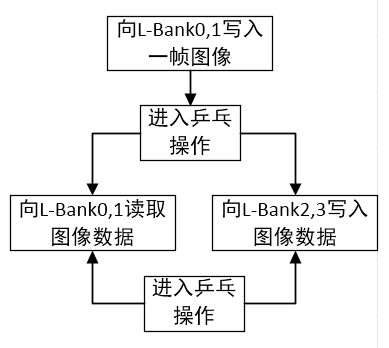

在实时视频采集系统中,为了保证数据的稳定性和连续性,通常采用乒乓操作对SDRAM进行读写操作。

第三部分:LCD工作原理

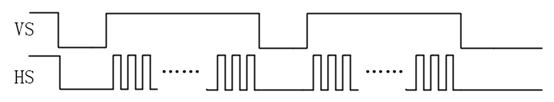

LCD主要由垂直同步脉冲(VS)和水平同步脉冲(HS)来分别控制帧显示与行显示,总体时序图如下:

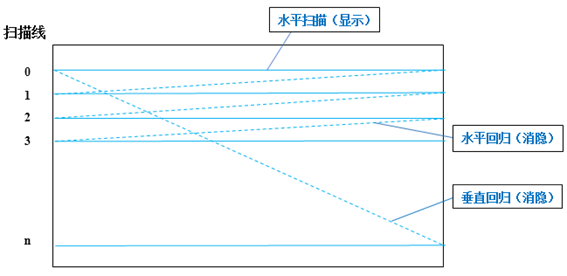

扫描原理如下图所示:

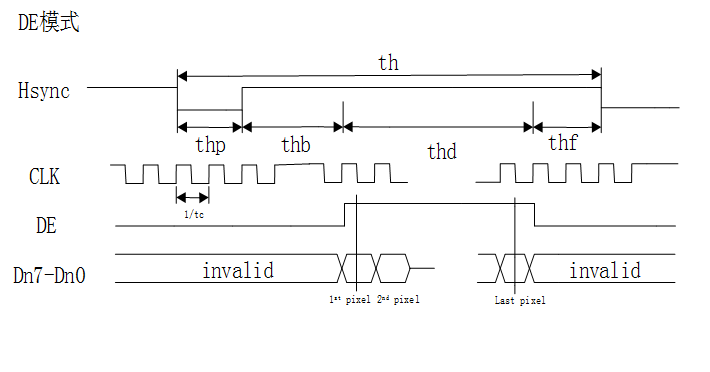

LCD驱动显示时序图如下:

设计两个计数器来表示VS和HS,由于一帧图像分辨率为640*480,因此,当HS=640时,表示一行图像数据,接着VS加1,传输第二行图像数据,当VS=480时,表示传输完一帧图像数据。因此LCD就能够显示一帧图像。

当需要从SDRAM读取一个像素点时,需要LCD发送一个标志位到SDRAM,表示开始读取图像像素点开始显示图像。由于之前摄像头配置的图像模式为RGB565格式,16位表示一个像素点。也就是说R为高5位,G为中间6位,B为最低5位。由于LCDRGB分别为8位,因此,需要将一个像素点的16位拆开,分别送给LCD中的RGB上。其余位补0即可。

基于FPGA摄像头图像采集显示系统的更多相关文章

- 基于FPGA的HDMI显示设计(三)

上一篇:基于FPGA的VGA显示设计(二) 10月10日 ~ 20日期间实习,令我万万没想到的是实习题目是 “便携式高清电视显示屏测试系统原型设计” 也就是 “基于FPGA的视频显示”. 实习要求用 ...

- 基于FPGA的VGA显示实验设计

基于FPGA的VGA显示实验设计 成果展示(优酷视频): 视频: 基于FPGA的VGA显示技术(手机控制) http://v.youku.com/v_show/id_XNjk4ODE3ODUy.htm ...

- 基于FPGA的VGA显示设计(二)

上一篇:基于FPGA的VGA显示设计(一) 参照 CrazyBingo 的 基于FPGA的VGA可移植模块终极设计代码 的工程代码风格,模块化处理了上一篇的代码,并增加了一点其它图形. 顶层 ...

- 基于FPGA的VGA显示静态图片

终于熬到暑假了,记过三四周的突击带考试,终于为我的大二画上了一个完整的句号,接下来终于可以静心去做自己想做的事情了,前一阵子报了一个线上培训班,学学Sobel边缘检测,之前一直在学习图像处理,但是因为 ...

- 基于FPGA的VGA显示设计(一)

前言 FPGA主要运用于芯片验证.通信.图像处理.显示VGA接口的显示器是最基本的要求了. 原理 首先需要了解 : (1)VGA接口协议:VGA端子_维基百科 .VGA视频传输标准_百度 引脚1 RE ...

- 基于FPGA驱动VGA显示图片的小问题

学习VGA显示图片的过程中,遇到了一个小问题,我在显示屏上开了一个60x60的框,放了一张图片进去显示,但是最终的结果如下图所示. 出现了一个竖黑边,看了看代码,分析了一下逻辑没问题,然而看这个显示那 ...

- 基于FPGA的Uart接收图像数据至VGA显示

系统框图 前面我们设计了基于FPGA的静态图片显示,接下来我们来做做基于FPGA的动态图片显示,本实验内容为:由PC端上位机软件通过串口发送一幅图像数据至FPGA,FPGA内部将图像数据存储,最后扫描 ...

- 基于FPGA的DDR3多端口读写存储管理系统设计

基于FPGA的DDR3多端口读写存储管理系统设计 文章出处:电子技术设计 发布时间: 2015/03/12 | 1747 次阅读 每天新产品 时刻新体验专业薄膜开关打样工厂,12小时加急出货 机载 ...

- 基于FPGA的图像去噪

目录 结构图 其中FPGA 控制模块为核心,通过它实现视频图像数据的获取.缓存.处理和控制各模块间通讯[1].由CCD 相机对目标成像,高速图像数据由camera link 实时传输[2],经信号转换 ...

随机推荐

- webpack安装与配置初学者踩坑篇

webpack是基于nodejs开发出来的前端工具 webpack可以处理js文件的依赖关系,webpack能够处理js的兼容问题,把高级浏览器不识别的语法转换成浏览器正常识别的语法 (jnlp是基于 ...

- (4.4)mysql备份还原——备份存储容灾基础知识

存储知识 1.为什么需要存储,存储一般解决哪些问题? 容量.速度.易于管理.安全(容灾与备份).可扩展性 2.存储发展历史 [2.1]大型机 [2.2]c/s结构(客户端->服务器) [2.3] ...

- weblogic学习教程(一)

一.简介 WebLogic是美国Oracle公司出品的一个application server,确切的说是一个基于JAVAEE架构的中间件,WebLogic是用于开发.集成.部署和管理大型分布式Web ...

- python序列元素引用容易出错的地方

python序列分列表和元组,不同之处在于元组的元素不能修改.元组使用小括号,列表使用方括号.元组创建很简单,只需要在括号中添加元素,并使用逗号隔开即可.举个简单的例子,a1是一个元组,a2是一个列表 ...

- The Swift Programming Language 中文版

http://numbbbbb.github.io/the-swift-programming-language-in-chinese/

- what's the python之模块

正则表达式 首先,我们引入了正则表达式的知识.所谓正则表达式,就是对字符串操作的一种逻辑公式,就是用事先定义好的一些特定字符.及这些特定字符的组合,组成一个“规则字符串”,这个“规则字符串”用来表达对 ...

- 全连接与softmax[转载]

转自:https://www.jianshu.com/p/88bb976ccbd9 1.全连接示例: 2.softmax softmax输入层应和输出层(输出维度与类别数一致)纬度一样,如果不一样,就 ...

- [Java in NetBeans] Lesson 11. While Loops

这个课程的参考视频和图片来自youtube. 主要学到的知识点有:(the same use in C/C++) 1. while loop while(i < max){} will keep ...

- datetime函数和random.seed()函数的应用

一,datetime 在python中datetime是一个库是一个模块也是一个函数,作用很多,这里面只对其做简单的最常用的讲解. 首先返回系统时间 import datetime nowTime=d ...

- Charles 安装图解(Mac 抓包工具)

概述 Fidder使用C#开发的,所以就不能在Mac上使用了,不过还有另外一个抓包神器,就是Charles,它是Java开发的,所以跨平台,不仅可以在Mac上使用,Linux以及Window下都是可以 ...