Verilog篇(一)

Verilog在行为级建模时常用到的一些函数,变量等。

1:$random(seed),每次根据seed的值产生一个32位的有符号数,seed的数据类型必须是寄存器(reg),整形(integer),时间(time)等类型。变形$dist_uniform(seed,start,end)。

integer a_time;

integer AP_SEED;

a_time = $dist_uniform(AP_SEED,min_time,max_time);

2: Driver strength spec,只适用于线网等类型的变量,wire tri wand等。可以在变量声明或连续赋值中使用。一对关键字分别表示(0,1)时的strength. 有supply,strong,pull,weak,highz等,strength按8个level划分。

assign (pull0,pull1) SD1_CLK = 1'b0;

3: $display("pc_mon_%d (time: %t): pc_ca7=%h ", PC_NUM,$time,cur_pc);

4: tranfif1 gpio_pads_logic0 (gpio_pads[0], tb_gpio_pads[0], select_gpio_driver);表示select_gpio_driver为1时,两个信号双向连接起来。

5:bufif1 bf1 (outw, inw, controlw); notif1 bf1(outw, inw, controlw); 表示相应的control为1时,输出会为Z,否则正常logic。只能单向传输。

6:buf和not可以有多个输出。 buf b1(out1, out2, in); in输入,out1,out2输出。只能单向传输。

7: specify模块用于指定source与destination之间的时延,参数用specparam表示。

8:final begin...end,在$finish之前,会显式调用的procedure。

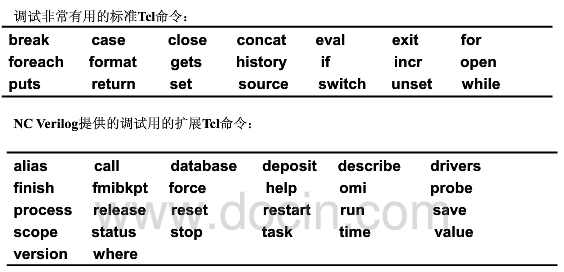

9:NC verilog调试的一些tcl命令:

deposit,与force信号作用类似,但是如果有驱动自然会跟随驱动的情况。

verilog中的位运算符,缩位运算符,逻辑操作符。

1)位运算符:操作数几位,结果就有几位,若两个操作数位数不同,位数短的操作数做段补零。

按位取反:~

按位与:&

按位或:|

按位异或:^

按位同或:^~或~^

2)缩位运算符:结果只有一位。

与缩位运算:&

或缩位运算:|

异或缩位运算:^

与,或,异或,和非运算符组成的复合运算符:~&, ~|, ~^

3)逻辑运算符:

逻辑与:&&

逻辑或:||

逻辑非:!

逻辑与和逻辑非是双目运算符,逻辑非是单目运算符。

Verilog篇(一)的更多相关文章

- 阻塞赋值与非阻塞赋值(verilog篇)

阻塞赋值与非阻塞赋值(verilog篇) 2017-09-30 竹海 相约电子ee 相信刚刚接触verilog的读者,多少对阻塞赋值和非阻塞赋值仍有一些困惑.笔者在这篇文章,带领大家深入的理解这两者的 ...

- Verilog篇(二)系统函数

显示任务:$display,$write, 前者总会输出一个换行符,后者不会.固定输出格式版:$displayb/$displayo/$displayh/$writeb/$writeo/$writeh ...

- Verilog篇(三)仿真原理

首先引入一个例子: `timescale 1ns/100ps module TB; ...

- Verilog篇(四)时序模型

时序模型:仿真器的时间推进模型,它反映了推进仿真时间和调度事件的方式. 1)门级时序模型:适用于分析所有的连续赋值语句,过程连续赋值语句,门级原语,用户自定义原语. 特点:任意时刻,任意输入变化都将重 ...

- TGL站长关于常见问题的回复

问题地址: http://www.thegrouplet.com/thread-112923-1-1.html 问题: 网站配有太多的模板是否影响网站加载速度 月光答复: wp不需要删除其他的模板,不 ...

- FPGA基础(verilog语言)——语法篇(续1)

上一篇文章提到了FPGA中一个模块基本结构,这篇文章开始介绍语法. 首先,我们学习一门语言都要从这门语言的单词学起,所以verilog中的关键词都有哪些呢?看下面: A:always.assign B ...

- Verilog学习笔记基本语法篇(十二)········ 编译预处理

h Verilog HDL语言和C语言一样也提供编译预处理的功能.在Verilog中为了和一般的语句相区别,这些预处理语句以符号"`"开头,注意,这个字符位于主键盘的左上角,其对应 ...

- Verilog学习笔记基本语法篇(十一)········ 常用系统函数

1)系统任务:$monitor 格式: $monitor(p1,p2,p3...pn); $monitor; $monitoron; $monitoroff; 任务$monitor提供了监控输出列 ...

- Verilog HDL那些事_建模篇笔记(实验七:数码管电路驱动)

1.同步动态扫描 多个数码管的显示采用的是同步动态扫描方法,同步动态扫描指的是:行信号和列信号同步扫描,是一种并行操作. 2.数码管驱动电路实现思路 如果要求数码管显示我们想要的数字,首先需 ...

随机推荐

- php--linux环境下的主从复制

1.编辑数据库配置文件my.cnf,一般在/etc/目录下. #vi /etc/my.cnf 在[mysqld]的下面加入下面代码:[第一步查看本文件夹中代码是否已经存在,存在不需要进行添加] 只是修 ...

- One Time Auth

One Time Auth One-time authentication (shortened as OTA) is a new experimental feature designed to i ...

- cf707D. Persistent Bookcase(离线+dfs)

题目链接:http://codeforces.com/problemset/problem/707/D 有一个n*m的书架,有K个操作,求每个操作后一共有多少本书:有4种操作: 1:x y 如果 x ...

- 实战案例:DIV嵌套

缘于页面结构语义化的考虑,我们应该慎用div和span这两个通用元素,只有当划分页面结构模块时才使用div元素,因为模块本身是没有任何语义的,他仅代表一块独立的结构.如果想对段落内部分内联元素或文本应 ...

- iOS block里的self

block是可以捕捉上下文的特殊代码块. block可以访问定义在block外的变量,当在block中使用时,它就会为其在作用域内的每个标量变量创建一个副本. 如果通过self拥有一个block,然后 ...

- UIFont 设置字体

abel.font = [UIFont fontWithName:@"Arial-BoldItalicMT" size:24]; 字体名如下: Font Family: Ameri ...

- CURL常用命令(转)

下载单个文件,默认将输出打印到标准输出中(STDOUT)中 curl http://www.centos.org 通过-o/-O选项保存下载的文件到指定的文件中:-o:将文件保存为命令行中指定的文件名 ...

- yum报错: Error: Cannot retrieve metalink for repository: epel. Please verify its path and try again

在Centos 5.x或6.x上安装RHEL EPEL Repo repository,资源库,源的意思.RHEL EPEL(Extra Packages for Enterprise Linux) ...

- 第五篇 SQL Server代理理解代理错误日志

本篇文章是SQL Server代理系列的第五篇,详细内容请参考原文. 正如这一系列的前几篇所述,SQL Server代理作业是由一系列的作业步骤组成,每个步骤由一个独立的类型去执行.在第四篇中我们看到 ...

- git 查看、创建、删除 本地,远程 分支

1. 查看远程分支 git branch -rorigin/master 2. 查看本地分支 git branch *master 注:以*开头指明现在所在的本地分支 3. 查看本地分支和远程分支 g ...