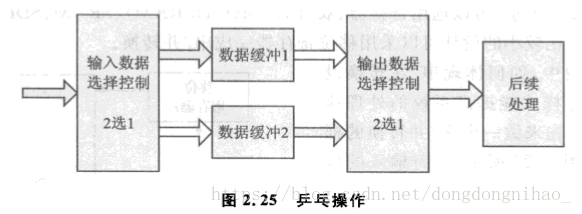

FPGA之乒乓操作

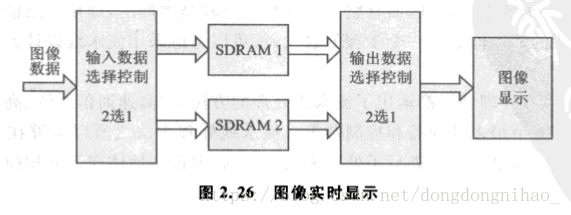

比如将乒乓操作运用在液晶显示的控制模块上,如图所示。

module pingpang

(

input clk ,

input rst_n ,

input [:] data_in , // 输入数据

output reg [:] data_out // 输出数据

); // ------------------------------------------------------ //

reg [:] buffer1 ; // 缓存1

reg [:] buffer2 ; // 缓存2

reg wr_flag ; // 写标志,wr_flag=0,写buffer1,wr_flag=1,写buffer2

reg rd_flag ; // 读标志,rd_flag=0,读buffer2,rd_flag=1,读buffer1

reg state ; // 状态机,0:写1读2,1:写2读1,状态转移和输出分开编码

// ------------------------------------------------------ //

// 状态转移

always @ (posedge clk or negedge rst_n)

begin

if(rst_n == 'b0)

begin

state <= 'b0;

end

else

begin

state <= !state;

//case(state)

// 1'b0 : state <= 1'b0; // 写1读2->写2读1

// 1'b1 : state <= 1'b1; // 写2读1->写1读2

// default : state <= 1'b0;

//endcase

end

end

// ------------------------------------------------------ //

// 状态输出

always @ (state)

begin

case(state)

'b0:

begin

wr_flag = 'b0; // 写1

rd_flag = 'b0; // 读2

end

'b1:

begin

wr_flag = 'b1; // 写2

rd_flag = 'b1; // 读1

end

default:

begin

wr_flag = 'b0;

rd_flag = 'b0;

end

endcase

end

// ------------------------------------------------------ //

// 写buffer数据

always @ (posedge clk or negedge rst_n)

begin

if(rst_n == 'b0)

begin

buffer1 <= 'b0;

buffer2 <= 'b0;

end

else

begin

case(wr_flag)

'b0 : buffer1 <= data_in; // wr_flag = 0,写buffer1

'b1 : buffer2 <= data_in; // wr_flag = 1,写buffer2

default :

begin

buffer1 <= 'b0;

buffer2 <= 'b0;

end

endcase

end

end

// ------------------------------------------------------ //

// 读buffer数据

always @ (posedge clk or negedge rst_n)

begin

if(rst_n == 'b0)

begin

data_out <= 'b0;

end

else

begin

case(rd_flag)

'b0 : data_out <= buffer2; // rd_flag=0,读buffer2

'b1 : data_out <= buffer1; // rd_flag=1,读buffer1

default : data_out <= 'b0;

endcase

end

end

// ------------------------------------------------------ //

endmodule

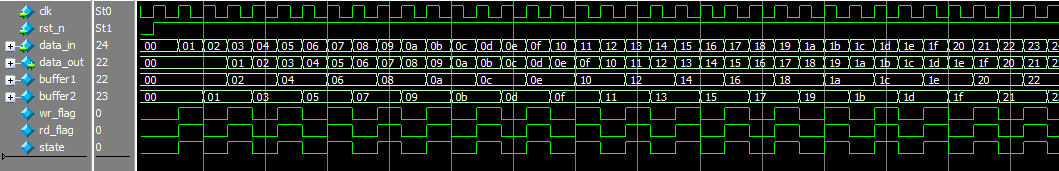

2.2 FPGA仿真代码

`timescale 1ns / 1ps

module pingpang_tb();

reg clk ;

reg rst_n ;

reg [:] data_in ;

wire[:] data_out;

always # clk = ~clk;

initial

begin

rst_n <= 'b0 ;

clk <= 'b0 ;

#;

rst_n <= 'b1 ;

end

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

data_in <= 'd0;

else

data_in <= data_in + 'b1;

end

pingpang dut

(

.clk (clk ),

.rst_n (rst_n ),

.data_in (data_in ),

.data_out (data_out )

);

endmodule

3.仿真结果

FPGA之乒乓操作的更多相关文章

- 【FPGA技巧篇一】FPGA设计的四种常用思想与技巧之一 :乒乓操作

本文篇章将讨论一下的四种常用 FPGA 设计思想与技巧: 乒乓操作. 串并转换. 流水线操作. 数据接口同步化, 都是 FPGA 逻辑设计的内在规律的体现, 合理地采用这些设计思想能在FPGA设计工作 ...

- FPGA SD 卡 之 乒乓操作 、同步fifo

这里记录一个实际的需要使用乒乓操作的例子:读sd卡数据的时,在spi的模式下.发送单数据块的读取命令,在回应之后会有 512字节的数据.使用乒乓操作,可以用两个八位的寄存器,就可以完成连续的512字节 ...

- sdram之乒乓操作

在实时显示时,为了保证画面显示的完整性需要对SDRAM进行乒乓操作. SDRAM 中有 4 个bank ,地址分别为00 01 10 11,后面将用 0 1 2 3来描述 bank 0和1 作为第一个 ...

- DMA缓冲区乒乓操作的处理

http://www.51hei.com/bbs/dpj-141761-1.html https://blog.csdn.net/sunnydreamrain/article/details/8288 ...

- FPGA重要设计思想

FPGA重要设计思想 1.速度和面积互换原则.以面积换速度可以实现很高的数据吞吐率,其实串/并转换.就是一种以面积换速度的思想 2.乒乓操作. 3.串/并转换的思想. 高速数据处理的重要技巧之一. ...

- [华清远见]FPGA公益培训

本套视频教程为华清远见 网络公益培训活动,主讲人:姚远老师,华清远见高级讲师. ------------------------------------------------------------ ...

- 【转】 FPGA设计的四种常用思想与技巧

本文讨论的四种常用FPGA/CPLD设计思想与技巧:乒乓操作.串并转换.流水线操作.数据接口同步化,都是FPGA/CPLD逻辑设计的内在规律的体现,合理地采用这些设计思想能在FPGA/CPLD设计工作 ...

- CPLD VS FPGA

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL.GAL.CPLD等可编程器件的基础上进一步发展的产物.它是作为专用集成电路(ASIC)领域中的 ...

- FPGA/CPLD设计思想与技巧

本文讨论的四种常用FPGA/CPLD设计思想与技巧:乒乓操作.串并转换.流水线操作.数据接口同步化,都是FPGA/CPLD逻辑设计的内在规律的体现,合理地采用这些设计思想能在FPGA/CPLD设计工作 ...

随机推荐

- DDoS攻击新趋势:海量移动设备成为新一代肉鸡

近期,阿里云安全团队观察到数十起大规模的应用层资源耗尽式DDoS攻击(应用层CC攻击).阿里云DDoS高防实现智能防护全程自动化检测并清洗,未对用户侧业务产生任何影响,这类攻击存在一些共同的特征,阿里 ...

- es6 默认参数、rest参数、扩展运算符

1.默认值 现在可以在定义函数的时候指定参数的默认值了,而不用像以前那样通过逻辑或操作符来达到目的了. function sayHello(name){ //传统的指定默认参数的方式 var name ...

- Android 性感美图在线浏览APP

周末无聊,遂整理了下近来常用的几个开源库,无意间又发现了一些开放接口,于是乎决定融合在一起,做个简单的"性感美图"浏览的APP,名字呢,就叫"性感沙滩",效果如 ...

- Shell echo 命令

Shell 的echo 指令与PHP的echo指令类似,都是用于字符串的输出.命令格式: echo string 您可以使用echo实现更复杂的输出格式控制. 1.显示普通字符串: echo &quo ...

- python selenium处理JS只读(12306)

12306为例 js = "document.getElementById('train_date').removeAttribute('readonly');" driver.e ...

- 深入python

while循环知识: while是关键字 格式我们要怎么写:; while 条件 : 缩进 循环(代码块) 这里面有个死循环######条件如果一直为真,就形成了一个环,就成为了死循环 那我们如 ...

- hdu 5744 Keep On Movin (2016多校第二场)

Keep On Movin Time Limit: 4000/2000 MS (Java/Others) Memory Limit: 65536/65536 K (Java/Others)Tot ...

- oracle优化EXPORT和IMPORT

使用较大的BUFFER(比如10MB , 10,240,000)可以提高EXPORT和IMPORT的速度. ORACLE将尽可能地获取你所指定的内存大小,即使在内存不满足,也不会报错.这个值至少要和表 ...

- Java 对象序列化机制详解

对象序列化的目标:将对象保存到磁盘中,或允许在网络中直接传输对象. 对象序列化机制允许把内存中的Java对象转换成平台无关的二进制流,从而允许把这种二进制流持久的保存在磁盘上,通过网络将这种二进制流传 ...

- 【知识小结】PHP使用svn笔记总结

在公司里,我们要养成每天上班前更新代码,下班前提交代码的习惯,并且做好说明. svn更新代码的时候,先右键点击需要更新的项目,在team中进入资源库同步界面,选择incoming mode,显示的文件 ...