Zynq系列FPGA如何固化bit文件到QSPI_Flash

最近由于项目需要,要将bit文件固化到zedboard的flash中,使程序上电自启,断电不丢失。

我们知道,一般板级调试的时候都是直接下载bit流到FPGA就行,固化到Flash的话,也是先生成.mcs文件,然后下载到Flash即可。

但是在经过反复尝试之后,发现对zynq系列好像行不通。

why?这得从zynq的启动流程说起。

一、ZYNQ的启动流程

ZYNQ7000 SOC 芯片可以从 FLASH 启动,也可以从 SD 卡里启动, 本节介绍程序 FLASH 启动的方法。Zynq7000 SOC 芯片上电后,最先运行的是ARM端系统(PS)。然后再通过ARM系统软件部分加载FPGA的比特流文件.bit至FPGA(PL),配置FPGA PL端的逻辑功能。ZYNQ 系统的启劢流程如下:

ZYNQ启动分为两个阶段

- 第一阶段是 BOOT ROM(ZYNQ厂家固化代码)

- 第二阶段是 FSBL (First Stage Bootloader)SDK工具来制作。

经过以上两个阶段,PL端配置程序及应用程序才开始运行。

1.1 第一阶段 (BOOT ROM)

- 上电后,Zynq7000 SOC 会首先执行片内 Boot ROM 代码,Boot ROM 代码读取 Boot mode 寄存器来判断是哪一种启动方式(SD card/QSPI Flash/JTAG)。

- 确定好哪种启劢方式后,Boot ROM 从相应的启动设备(SD Card/QSPI Flash)加载 First Stage Bootloader (FSBL) 到On Chip Memory(OCM) RAM,并且将执行权交付给 FSBL。

1.2 第二阶段 FSBL (First Stage Bootloader)

使用SDK 工具一步步生成 FSBL 代码和可执行文件,结合代码可知 FSBL 主要做了如下工作:

- 初始化 CPU,初始化串口;

- Processor System (PS) 一些控制器的初始化,如 MIO, PLL, CLK and DDR;

- 禁止 L1 Data Cache;

- 注册 ARM 中断向量;

- 通过 Boot mode 寄存器,判断是哪种启动方式。

1.2.1 QSPI Flash 启动方式:

- 初始化 QSPI Flash 控刢器;

- 从 Flash 拷贝 system.bit 到 FPGA (如果 Flash 中存有 system.bit);

- 从 QSPI Flash 拷贝应用程序的代码到DDR3;

- 调转到应用程序执行;

1.2.2 SD Card 启动方式:

- 初始化 SD 控刢器;

- 从 SD Card 拷贝 system.bit 到 FPGA (如果 BOOT.BIN 中存有 system.bit);

- 从 SD card 拷贝应用程序的代码到 DDR3;

- 跳转到应用程序执行;

1.2.3 JTAG 启动方式,直接退出。

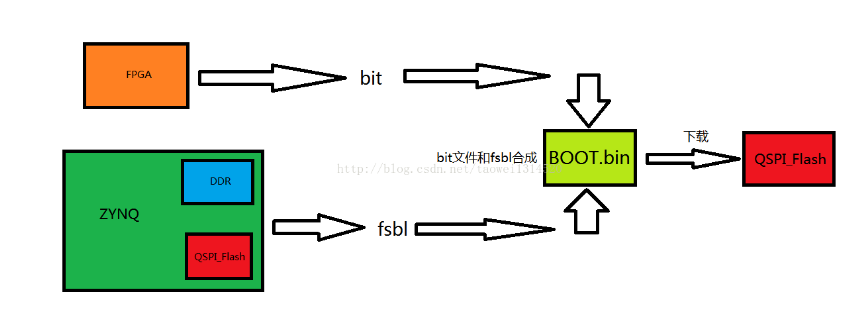

因此,对于Zynq系列的FPGA芯片来说,固化到Flash中的bit文件需要一个引导程序(也就是FSBL),才能被用来配置PL。实际上,FSBL会作为BootLoader和bit文件一起合成一个.bin或者.mcs文件,然后下载到Flash中,过程如下:

二、生成BOOT.bin或者BOOT.mcs

2.1 VIVADO操作

你应该已经有了一个完整的工程,接下来你需要添加并配置PS端,生成新的bit文件:

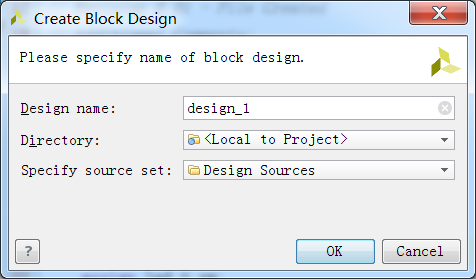

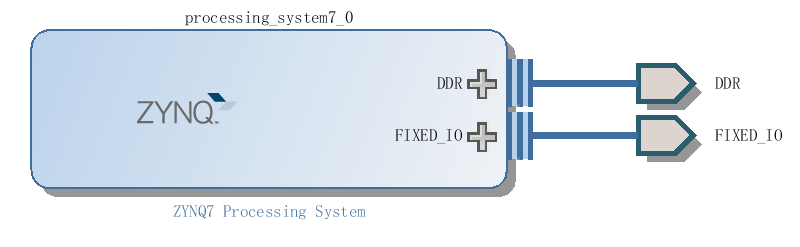

(1)建立一个新的块设计(Create Block Design)

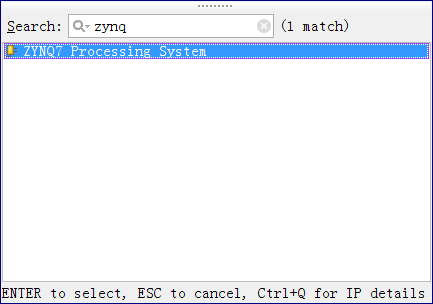

(2)添加ZYNQ7 Processing System

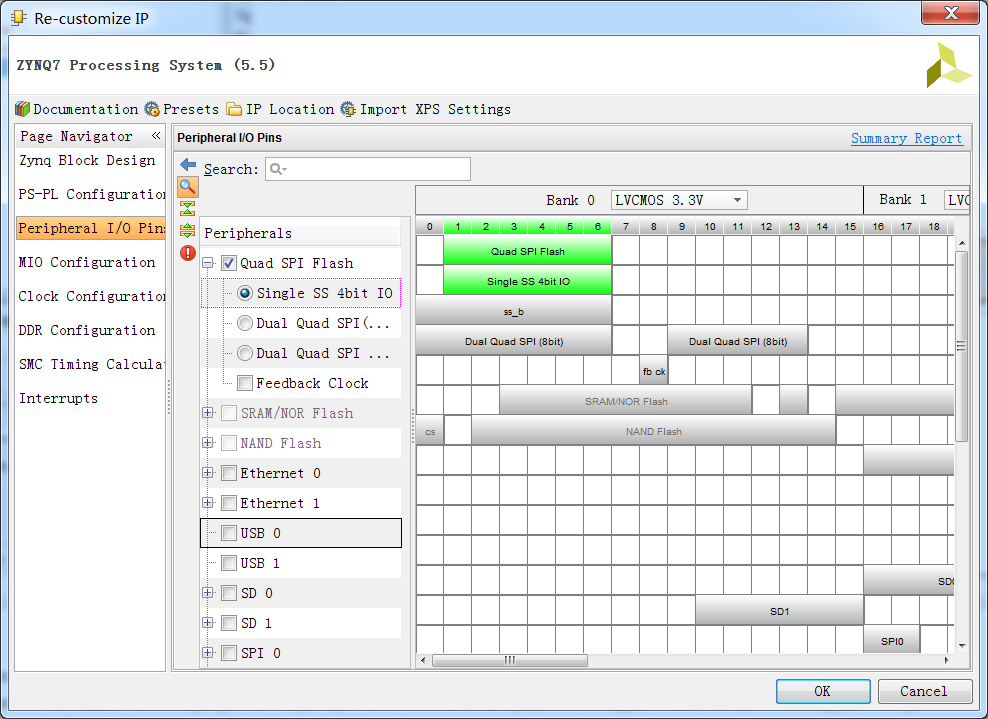

(3)双击所添加的zynq7,配置peripheral I/O,我们只保留Quad SPI Flash

(4)在 Diagram 界面里点击"Run Block Automation"完成对 ZYNQ7 Processing System IP核的配置,生成外部 ZYNQ 系统的外部链接 IO 管脚。

(5)在 Source 窗口中选中 design_1.bd,右键并先后选择Generate Output Projects 和 Create HDL Wrapper 选项,生成顶层文件design_1_wrapper。

(6)在顶层文件中例化我们原来的工程;(特别注意:要将原来工程的外部引脚也例化为现在顶层工程的I/O,并配置好约束)。

(7)重新生成bit流。

(8)Export to Hardware(包含bitstram 文件),Launch SDK,暂时告别VIVADO,进入SDK进行操作。

2.1 SDK操作

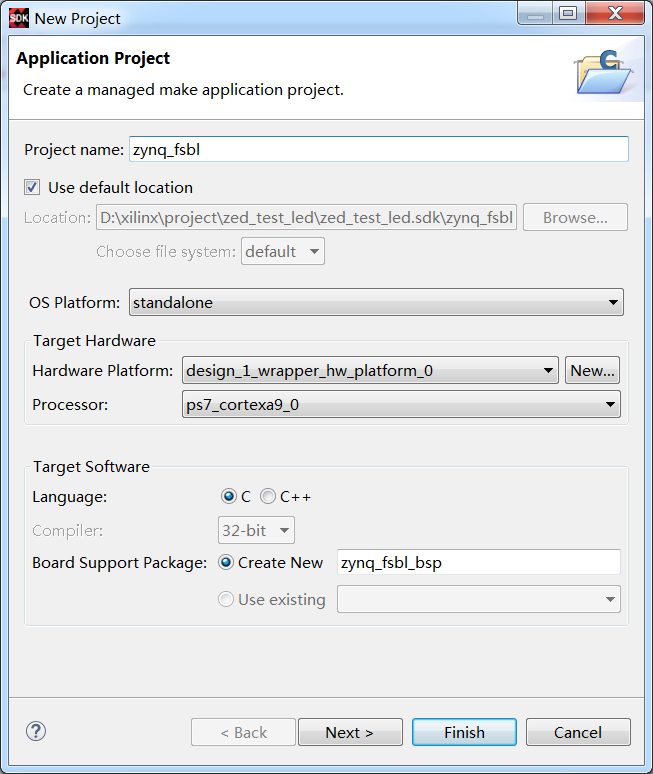

(1)进入SDK 开发环境后,点击菜单 File -> New -> Application Project。

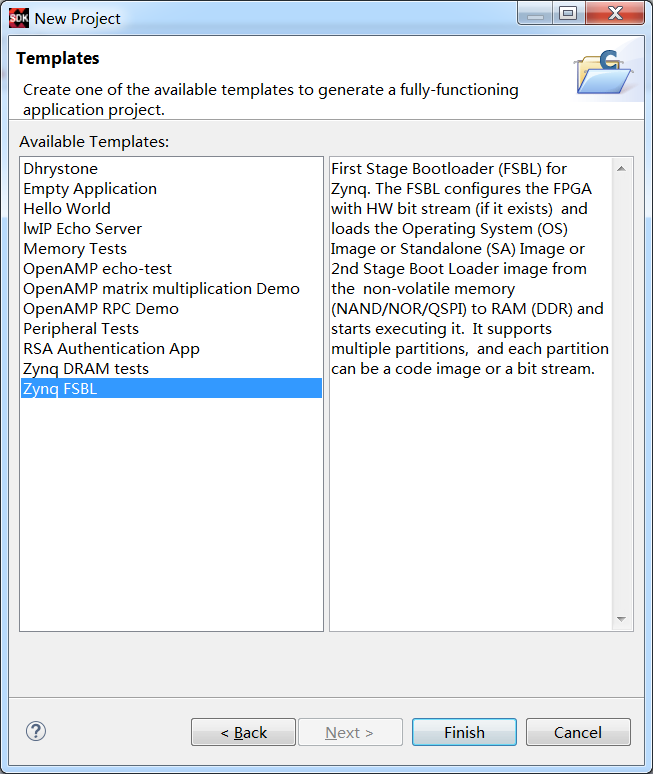

(2)点击next,选择Zynq FSBL

(3)接下去我们要把 FSBL 可执行文件,FPGA PL的bit比特流文件和PS应用程序结合成一个 Bin 文件或Mcs文件。

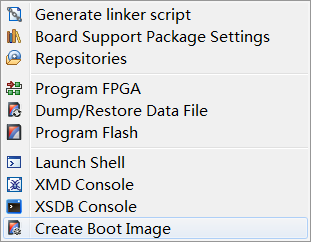

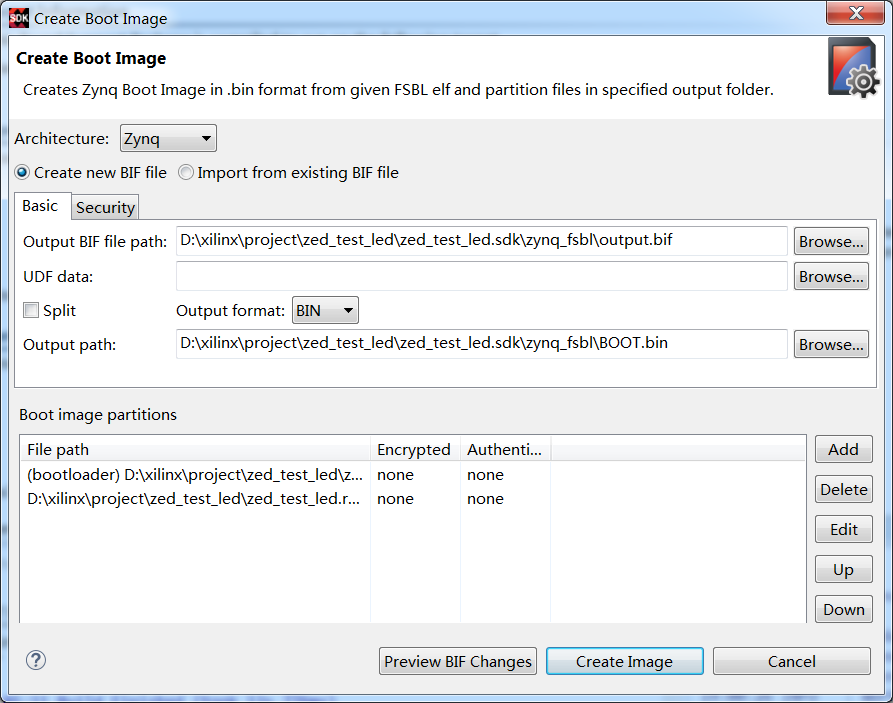

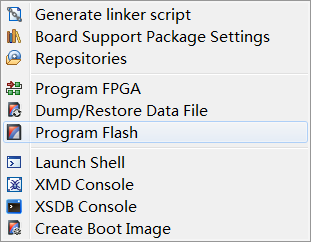

选择菜单 Xilinx Tools->Create Boot Image:

选择output.bif的存放地址,选择生成bin文件还是mcs文件,然后依次添加zynq_fsbl.elf(BootLoader)、bit文件、应用程序elf文件(这个如果没有可以省略),最终生成用于固化的bin或者mcs文件。

(4)将生成的bin或者mcs文件下载到Flash(经过验证,这两种类型的文件都可以)

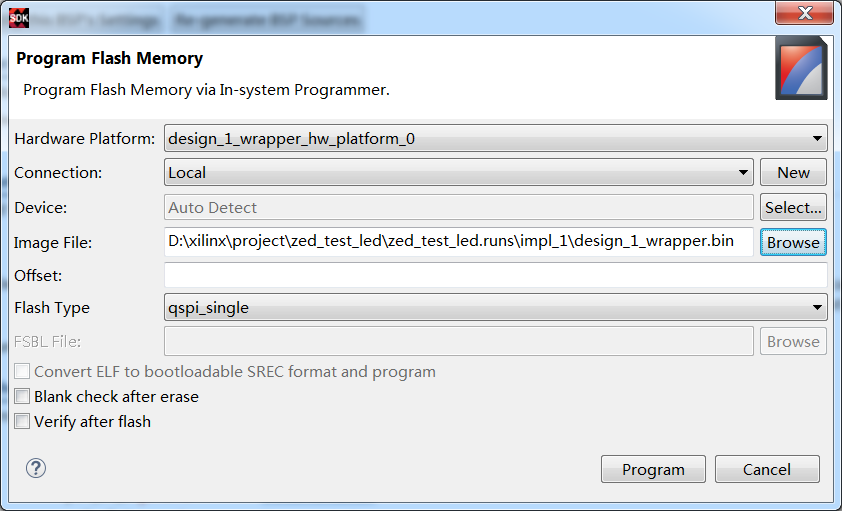

开发板上电,选择菜单 Xilinx Tools->Program Flash:

加载文件:

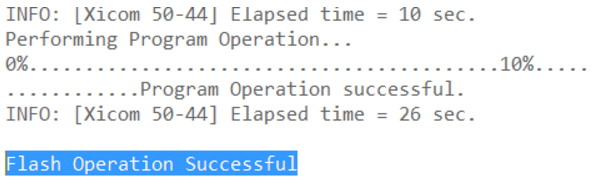

(5)点击Program,出现如下信息,则成功。然后断电,切换板子的启动方式,然后重新上电就会发现板子自动配置完成的灯亮了,搞定!

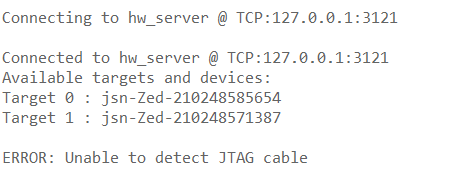

注意:若出现以下信息,排除掉Jtag线缆的问题之后,可能的原因是之前同时连接过多个开发板,导致识别出来的芯片型号有不止一个,然后它就检测到JTAG断开(我就是这个问题)。

解决方法很简单:关掉SDK,重新打开,重新Program Flash即可。

参考连接:1.https://blog.csdn.net/taowei1314520/article/details/78595482

2.https://blog.csdn.net/fengyuwuzu0519/article/details/80411894

Zynq系列FPGA如何固化bit文件到QSPI_Flash的更多相关文章

- Zynq系列程序逻辑固化方法

1.创建一个BOOT镜像 该小节主要讲述zynq平台利用软件套件SDK创建一个可固化BOOT镜像. 1.1 选择Ad9361_Eque1工程,选择Xilinx Tools → Create Boot ...

- Xilinx zynq-7000系列FPGA移植Linux操作系统详细教程

Xilinx zynq-7000系列FPGA移植Linux操作系统详细教程 一:前言 最近手上压了一块米联客的Miz7035,一块xilinx zynq-7000系列的开发板,想着正好学习一下linu ...

- Lattice系列FPGA入门相关0(Lattice与Altera、Xilinx对比及入门)

需求说明:Lattice系统FPGA入门 内容 :Lattice与Altera.Xilinx对比 来自 :时间的诗 1.Lattice与Altera.Xilinx对比 latt ...

- Xilinx 7系列FPGA部分重配置【2】

在之前的“Xilinx 7系列FPGA部分重配置[1]”中已经较为详细地记录了分别在工程模式(Project Mode)和非工程模式(Non-Project Mode)下.使用7系列的Xilinx F ...

- 关于zynq系列板卡设计VREFP_0参考电压的疑问及解答

使用板卡:Z-turn Board 芯片:Xilinx Zynq-7010/7020处理器 有工程师在试用zynq系列Z-turn Board时提出:在原理图P3页 Bank0上VREFP_0端接地的 ...

- ZYNQ系列

赛灵思公司(Xilinx)推出的行业第一个可扩展处理平台Zynq系列.旨在为视频监视.汽车驾驶员辅助以及工厂自动化等高端嵌入式应用提供所需的处理与计算性能水平. 中文名 ZYNQ系列 开发商 赛灵 ...

- (qsf文件 、 tcl文件 和 csv(txt)文件的区别) FPGA管脚分配文件保存、导入导出方法

FPGA管脚分配文件保存方法 使用别人的工程时,有时找不到他的管脚文件,但可以把他已经绑定好的管脚保存下来,输出到文件里. 方法一: 查看引脚绑定情况,quartus -> assignment ...

- webpack4 系列教程(十一):字体文件处理

教程所示图片使用的是 github 仓库图片,网速过慢的朋友请移步<webpack4 系列教程(十一):字体文件处理>原文地址.或者来我的小站看更多内容:godbmw.com 0. 课程介 ...

- 7系列FPGA远程更新方案-QuickBoot(转)

reference: http://xilinx.eetrend.com/d6-xilinx/article/2014-04/7009.html reference : quickboot meth ...

随机推荐

- 还在期待安卓9.0吗?Android 10.0要来了

目前,美国 Google公司的 AndroidP (安卓9.0),已经正式全面推出有几个多月了.众多手机品牌厂商也都在积极的进行更新适配 Android 9.0 系统(修改UI界面也算是二次开发,嗯) ...

- JavaScript入门学习笔记(一)

W3cJavaScript教程 JS是JavaScript的缩写,而JSP是Java Server Page的缩写,后者是用于服务器的语言. JavaScript代码写在标签<script> ...

- 原生javascript实现阻止浏览器默认行为与阻止事件冒泡

不同的浏览器之间存在兼容问题,在IE与标准浏览器之间存在很大的差异,所以在实现阻止浏览器默认行为和阻止事件冒泡就要考虑要它们之间的不同 /** * 取消冒泡 * @param {事件} e */ fu ...

- ssm实现图片上传

在使用ssm完成前后端对接时,总免不了前台传过来的文件问题,而html中的<input>框直接使用时,往往会获取不到路径,今天在完成图片上传后的来做个总结 首先,前台页面 <!DOC ...

- Eclipse安装git插件以及关联导入GitHub项目

一.Eclipse配置git 1.查看自己eclipse的版本 打开eclipse 导航: help->AboutEclipse 如图: 2.检查Eclipse中是否已安装Git插件 菜单栏He ...

- python安装多版本

39.107.96.81 root 123123 pyenv#可以实现python多版本控制与切换 pyenv local 3.5.1 ipython#更方便的编写python,可以补全命令彩色显示等 ...

- Redis 可视化工具:Web Redis Manager

以前用的:RedisDesktopManager (0.9.3以后需要订阅) https://github.com/uglide/RedisDesktopManager/releases 现在需要订阅 ...

- 关于postman各功能的说明及用法以及批量执行

这玩意功能还不错,可以学学,在测试接口或者配合写代码测接口时是有帮助作用的.今天也去打听了一下,一下我就做了一下记录. 首先,主界面: 分开记录,写的详细一些. 左侧菜单栏: 主菜单(请求部分); 输 ...

- 局域网安全-生成树攻击-ARP攻击-MAC攻击-VTP攻击-动态VLAN的攻击

一.MAC layer attacks 1.CAM表的OVERLOAD 第三方设备不断发送变化的MAC地址,填满CAM表,对于后来合法的MAC地址不能学习到从而泛洪,这时攻击者将学习到合法者的数据包. ...

- react_app 项目开发 (8)_角色管理_用户管理----权限管理 ---- shouldComponentUpdate

角色管理 性能优化(前端面试) 需求:只要执行 setState(), 就会调用 render 重新渲染.由于有时调用了 setState,但是并没有发生状态的改变,以致于不必要的刷新 解决: 重写 ...