cadence学习一------>介绍

Allegro常用组件:

1.orcad capture cis------>>原理图

2.PCB editor----->>PCB

3.PAD designer------->>PAD

orcad capture cis------>>原理图

建立文件

工具栏

其中:

off-page connector 端口连接符号 在同一层次电路原理图中,同一页面或不同页面中,名称相同的端口连接符号在电气连接上是相连的。

net alias 网络标号,在原理图中此名称相同,并且此符号是在同一页面中,在电气连接上才是相连的。

绘制总线时格式:

DATA[0..3] DATA[0-3] DATA[0:3]表示一样的总线

注意:总线名称的最后一个字符不要采用数字,防止在生成网络表时产生问题

常用操作:

place bus----place 页面连接符-----place bus entry------place net alias

place part中添加元件库 libraries下虚线框按钮

自带常用库介绍:

| AMPLIFIER.OLB | 共182个零件,存放模拟放大器IC,如CA3280,TL027C,EL4093 |

| ARITHMETIC.OLB | 逻辑运算IC,如TC4032B,74LS85等。 |

| ATOD.OLB | A/D转换IC,如ADC0804,TC7109等 |

| BUS DRIVERTRANSCEIVER.OLB | 驱动IC,如74LS244,74LS373等数字IC。 |

| CAPSYM.OLB | 电源,地,输入输出口,标题栏等。 |

| CONNECTOR.OLB | 连接器,排针,如4 HEADER,CON AT62,RCA JACK等。 |

| COUNTER.OLB | 计数器IC,如74LS90,CD4040B。 |

| DISCRETE.OLB | 分立式元件,如电阻,电容,电感,开关,变压器等常用零件。 |

| DRAM.OLB | 动态存储器 |

| ELECTRO MECHANICAL.OLB | 马达,断路器等电机类元件。 |

| FIFO.OLB | fifo |

| FILTRE.OLB | 滤波器 |

| FPGA.OLB | fpga |

| GATE.OLB | 门 |

| LATCH.OLB | 锁存器 |

| LINE DRIVER RECEIVER.OLB | 线性驱动接收器 |

| MECHANICAL.OLB | 存放机构图件 |

| MICROCONTROLLER.OLB | 微控制器 |

| MICRO PROCESSOR.OLB | 微处理器 |

| MISC.OLB | 存放杂项图件,如电表(METER MA) |

| MISC2.OLB | 存放杂项图件 |

| MISCLINEAR.OLB | 存放线性杂项图件 |

| MISCMEMORY.OLB | memory |

| MISCPOWER.OLB | power |

| MUXDECODER.OLB | 解码器 |

| OPAMP.OLB | 运放 |

| PASSIVEFILTER.OLB | 被动式滤波器 |

| PLD.OLB | 可编程逻辑器件 |

| PROM.OLB | PROM |

| REGULATOR.OLB | 稳压芯片 |

| SHIFTREGISTER.OLB | 移位寄存器 |

| SRAM.OLB | SRAM |

| TRANSISTOR.OLB | 晶体管 |

原理图基本操作:

1、 Place Part(P):放置元件

2、 Place wire(W):连接相连的pin脚

3、 Place Auto wire:自动连线

4、 Place bus(B):总线连接

5、 Place junction(J):交叉点连接,两条wire相交有两种连接关系:连或不连,加J为连

6、 Place bus entry(E):可以理解为总线入口,有bus必有entry

7、 Place net alias(N):相当于wire,用于连接距离远的Pin脚,仅限于同一page电气连接

8、 Place power(F):放置电源

9、 Place ground(G):放置地

10、 Place off-page connector:类似alias,但alias仅用于同一页面,而off-page用于不同页面之间的电气连接

11、 Place no connect(X):用于无电气连接的pin脚,不放会报错

12、 Place text(T):放置文本

常用操作:

1、按住Ctrl滚动鼠标滚轮放大缩小原理图(以鼠标指针为中心);直接滚动鼠标滚轮上下移动;按住Shift滚动左右移动

2、改变原理图尺寸大小:options->Schematic Page Properties->Page Size

3、旋转器件:放置器件前直接按R可旋转,放置后选中按R旋转

4、选中单个或者多个器件,按住Ctrl+鼠标左键,拖动鼠标,可复制所选器件

5、 连线时改变连线角度需先按shift键

6、元件镜像:选定后V键(垂直)和H键(水平)

7、鼠标右键选End mode结束当前操作

8、连线时,终点如不是管脚,双击结束

9、管脚之间不要直接相连,通过线连接以防出错(软件设置管脚之间不允许连接的方法:

Options/Preferences->Miscellaneous->Wire Drag打钩去掉)

后期处理:、

1、 浏览原理图:选中 .dsn , edit->browse 可以浏览parts、nets等,主要检查是否有漏掉的信息,双击可以打开原理图并高亮显示所选内容

2、 元件替换和更新:右键需要修改的元件,选择Replace cache或Update Cache

Replace cache:用于替换

Update Cache:用于更新

3、 Cleanup Cache:右键Design Cache选择Cleanup Cache用于检测Design Cache与原理图是否一致,并删除多余的内容

4、 移动:默认连线与移动元件一同移动,按住Alt 移动仅元件移动

5、 自动编号:右键.dsn 选Annotate 。首先选择Reset part references to ?进行复位,然后选择Unconditional reference update进行编号。

6、 添加footprint(保证与器件封装名称一致):

a、双击元件,找到PCB footprint,右键选择Edit,添加封装名称即可(右键选择Pivot可以切换显示方式)

b、按住Ctrl选择多个元件,右键选择Edit Properties进行添加

c、常用元件可通过元件库添加PCB封装

d、批量添加:右键Page 选择edit Object Properties

7、点击Pivot可以改变视图模式,可多选统一编辑

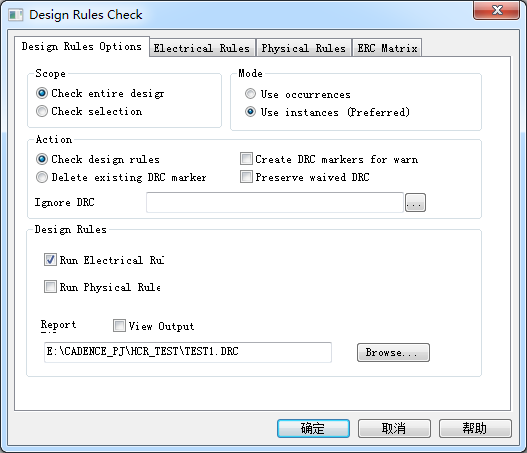

8、DRC检查:Tools->Design Rules Check

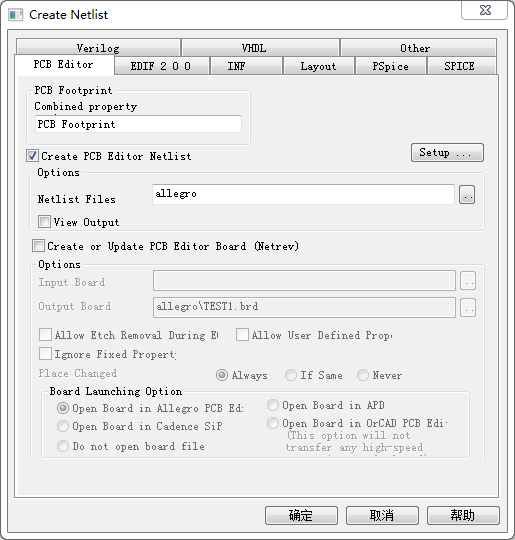

9、生成netlist:Tools->Create Nelist ,选择PCB Editor确认

10、生成BOM:Reports->CIS Bill of Materials

具体细节:

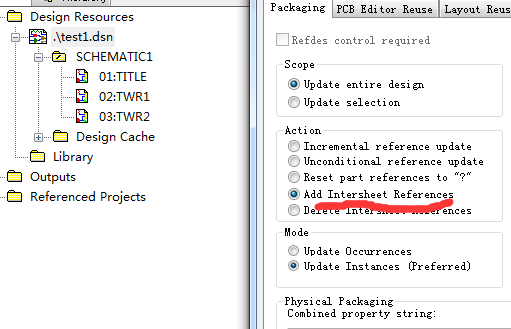

1.当有多个页面时,intersheet references的使用?

添加Intersheet references在页面连接符off page connector 后加上图纸页码编号,方便查找相关对象

offset relative to port 页面编号相对端口放置

offset relative to port name 页面编号相对端口名放置

reset positions 此处设置相对放置的位置

设置好后。页面连接符后会加上图纸页码编号

2.DRC检查

dsn----->>toors------>design rules check------->

3.生成网络表

网络表是原理图和PCB之间的桥梁

dsn------>tools------->create netlist

若网络表无错误,默认在dsn文件夹中将生成3个文件,pstxnet pstxprt pstchip

生成网表,常见错误:

1.封装属性(PCB Footprint)没有填写

2.PCB Footprint中包含不规范字符

3.原理图符号中引脚名重复

4.器件符号重复

5.原理图页码重复

可以通过菜单 Windows-Session Log窗口提示信息修改

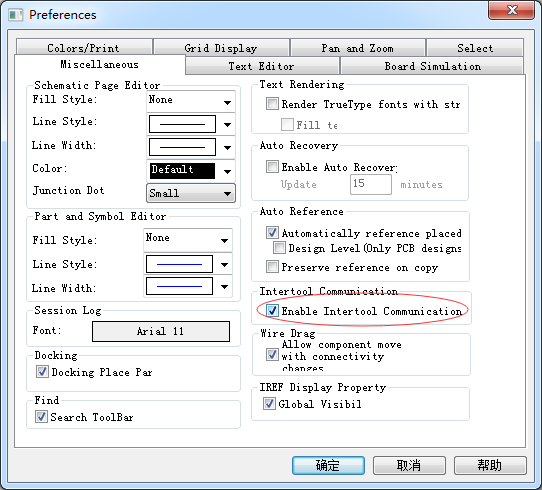

4。交互设置

在Capture中,通过菜单Options-Preferences选择Miscellaneous选项卡

勾选标记处enable Intertool Communication即可

cadence学习一------>介绍的更多相关文章

- C# BackgroundWorker组件学习入门介绍

C# BackgroundWorker组件学习入门介绍 一个程序中需要进行大量的运算,并且需要在运算过程中支持用户一定的交互,为了获得更好的用户体验,使用BackgroundWorker来完成这一功能 ...

- Android Testing学习01 介绍 测试测什么 测试的类型

Android Testing学习01 介绍 测试测什么 测试的类型 Android 测试 测什么 1.Activity的生命周期事件 应该测试Activity的生命周期事件处理. 如果你的Activ ...

- Redis学习01——介绍与搭建环境

Redis学习01介绍与搭建环境一简介二yum配置已经配置了的可以跳过三安装gcc四安装redis1 上传Redis到linux中2 解压到usrlocal下3 编译redis4 安装redis5 拷 ...

- 深度学习与CV教程(8) | 常见深度学习框架介绍

作者:韩信子@ShowMeAI 教程地址:http://www.showmeai.tech/tutorials/37 本文地址:http://www.showmeai.tech/article-det ...

- 硬件开发笔记(一):高速电路设计Cadence Aleego软件介绍和安装过程

前言 红胖子软硬通吃的前提的使用AD,涉及到高速电路板,要配合高速硬件工程师,使用Aleegro更合适,遂开启了Aleegro设计电路板学习,过程保存为开发笔记,旨在普及和沟通技术,共同进步,学无 ...

- Caffe 深度学习框架介绍

转自:http://suanfazu.com/t/caffe/281 Caffe是一个清晰而高效的深度学习框架,其作者是博士毕业于UC Berkeley的贾扬清,目前在Google工作. Caffe是 ...

- Ext学习-布局介绍

1.目标 了解ExtJS中的关于布局和组建的相关原理,并学习相关的布局方式 2.内容 1.布局和组件的相关原理 2.常见的布局方式 3.学习流程 1.首先应该学习一下布局和组件的相 ...

- Hibernate学习---基本介绍+作用+配置

从今天开始重新学习(以前学的太匆忙)Hibernate,这篇文章主要就一下几点进行讲解和说明: Hibernate的基本介绍 Hibernate的作用 Hibernate基本配置 Hibernate的 ...

- 【原创 深度学习与TensorFlow 动手实践系列 - 1】第一课:深度学习总体介绍

最近一直在研究机器学习,看过两本机器学习的书,然后又看到深度学习,对深度学习产生了浓厚的兴趣,希望短时间内可以做到深度学习的入门和实践,因此写一个深度学习系列吧,通过实践来掌握<深度学习> ...

随机推荐

- 【问题解决方案】查看Python安装了哪些库(pandas, matplotlib等等)

查看方法: 一句命令:cmd打开终端后键入pip list END

- Python3 视频教程,全网最全的视频教程,爬虫,从入门到实战

需要联系我:QQ:1844912514 最新Python基础班+就业班视频教程 链接: python分布式爬虫打造搜索引擎链接: https://pan.baidu.com/s/1N7HL7U0gQX ...

- WC2019游记

本来不打算写游记的,但后来想了想这么一次难忘的经历总该留下点痕迹吧...... DAY-1 走之前的最后一天,因为前一天晚上打了CF,所以早上9点才到机房.写了一道圆方树深深地体会到了来自仙人掌的恶意 ...

- How To Configure NetScaler AppFlow for SolarWinds

How To Configure NetScaler AppFlow for SolarWinds 来源 https://support.citrix.com/article/CTX227300 A ...

- python3.6使用pygal模块不具交互性,图片不能显示数据

1.版本 个人电脑版本:win10+python3.6 2.安装 2.1 安装过的版本 1. 先使用pip安装pygal1.7,(参考<python从入门到实践>) pyt ...

- promise和setTimeout执行顺序的问题

提出问题,问题代码为 setTimeout(function(){console.log(1)},0); new Promise(function(resolve){ console.log(2) f ...

- postman随机生成数

postman做重复测试时,随机数就有很大的作用,不用每次都输入 在postman的Params中,输入一个左大括号,会显示三种随机数: 也可以在body中设置 随机数如下: {{$guid}}:添加 ...

- Istio

什么是Istio Istio是Service Mesh(服务网格)的主流实现方案.该方案降低了与微服务架构相关的复杂性,并提供了负载均衡.服务发现.流量管理.断路器.监控.故障注入和智能路由等功能特性 ...

- my live thinkcenter / ThinkCentre M920x Tiny / Thinkpad yoga 12 vPro

s 025-58816312 联想3C服务中心:栖霞区学海路鸿运家园1栋6室 / 珠江路华海大厦8楼联想服务中心 营业时间:周一至周日,9:00∼18:00 ThinkPad Yoga 12 i7 v ...

- [面试]future模式

Future模式 什么是future模式? 传统单线程环境下,调用函数是同步的,必须等待程序返回结果后,才可进行其他处理. Futrue模式下,调用方式改为异步. Futrue模式的核心在于:充分利用 ...