scan design flow(一)

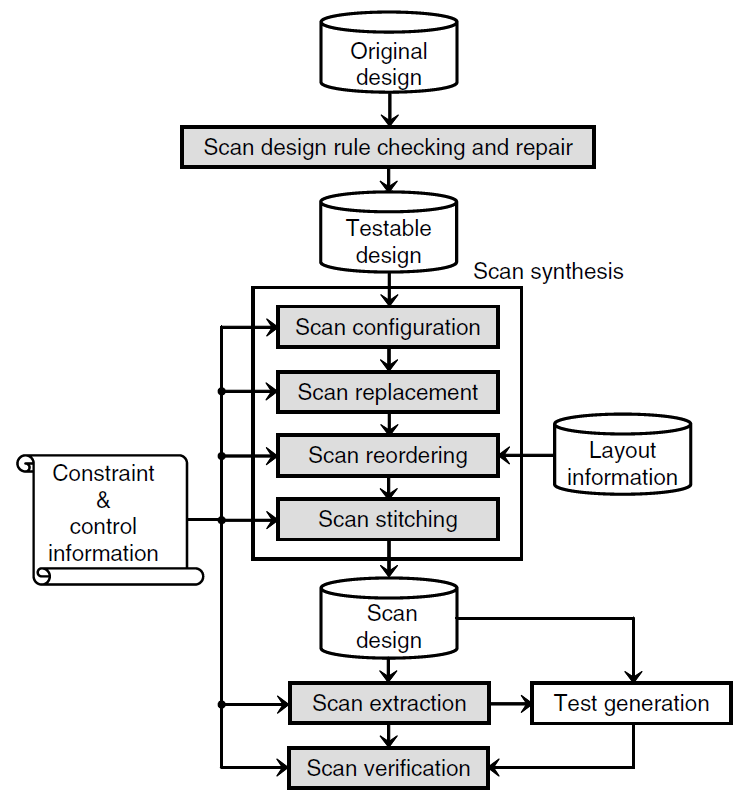

一个典型的scan实现的flow:

clock mux和一些rst,在Scan中都被bypass掉,是不能测到的。所以DFT的test coverage一般就在97%或98%。

scan design rule checking and repair:

可以在presynthesis RTL design或者postsynthesis gate-level design上进行,

经过scan repair之后的design,称为testable design。

scan synthsis是将一个testable design转换为一个scan design,目前design中会包含好几条scan chain。

scan extraction是将最终scan chain的结构提取出来,供ATPG使用。

scan verification针对shift,capture操作,进行response的验证。

Scan Design Rule Checking and Repair

进行scan design rule的check,某些clock control structure需要修改来增加at-speed test。

scan design rule的check也可以在scan synthesis之后,来保证没有新的violation出现。

在shift操作中,所有的clock都可以通过external pin来控制,在相邻的两个scan cell之间的

clock skew必须保证不会引起shift failure。

在capture操作中,data path的originate/terminate的clock可能是不一样的,这时需要考虑

timing来保证capture操作的正确。

Scan Synthesis

scan synthesis将一个testable design转变为一个scan design。

在1990年,scan synthesis的操作是一些分散的tools,将logic synthesis后的gate_level

netlist进行处理。

最近,scan synthesis的操作已经集成在了logic synthesis中,这样的处理,称为one-pass

synthesis或者single-pass synthesis。

主要包括四个部分:1)scan configuration; 2)scan replacement; 3)scan reordering;

4)scan stitching;

scan chain主要包括:

1)the number of scan chain;

2)the type of scan cells to implement these scan chain;

3)storage element to be excluded from scan synthesis;

4)the way of scan cell arranged in scan chain;

scan chain number主要由电路的input和output的个数来决定,high-speed的IO pad是不能

被用来做scan IO复用的。

scan cell的type,主要由lib来决定,一般每一种使用的storage element都会有相应的scan cell type,

来保证functionality和timing在正常操作下,被影响的最小。

exclude的storage element主要因为critical path或者security reason等。

storage element的arrange,主要由这些scan chain上的clock domain的多少来决定。

一般情况下,一个scan chain由属于同一个clock domain的scan cell组成,(因为在DC过程中,整个scan chain是一条data path

此时的异步逻辑在DFT中也会是同步的处理。)

当一个clock domain包含很多的scan cells时,一些scan chain会被结构化的实现,scan-chain operation被用来减小scan-chain的长度。

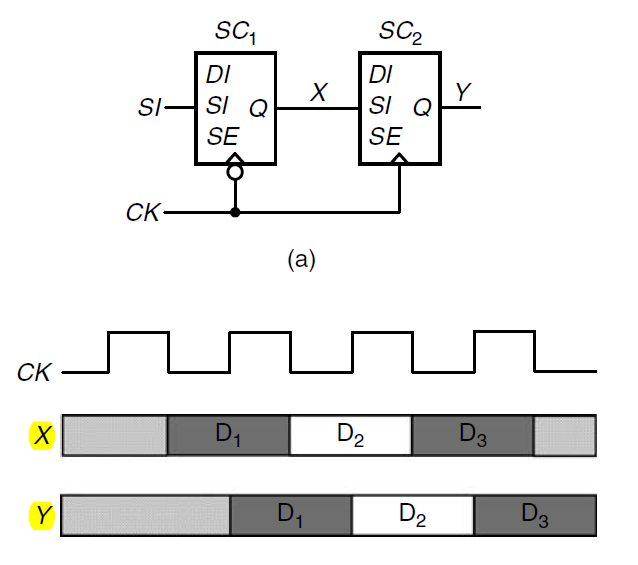

当一个scan-chain中既包含negative-edge scan cell又包括positive-edge scan cell时,negative的scan cell

应该放在positive scan-cell的前边。(为了clock一个周期只移动一位)

scan-chain的长度尽量平衡,方便并行化。

如果positive scan-cell放在前边,那么这两个cell在一个clock周期内,都会shift data。

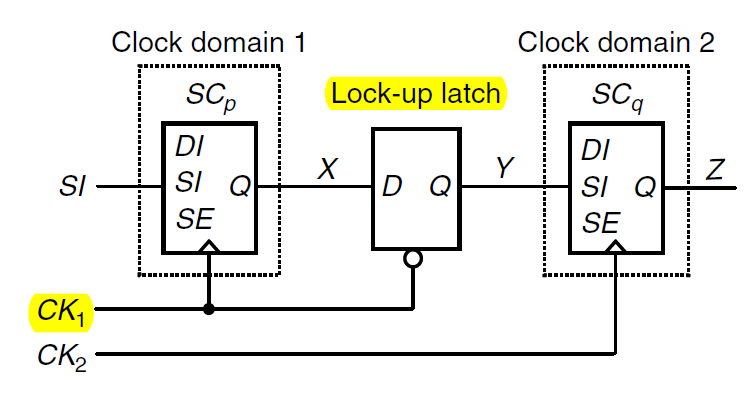

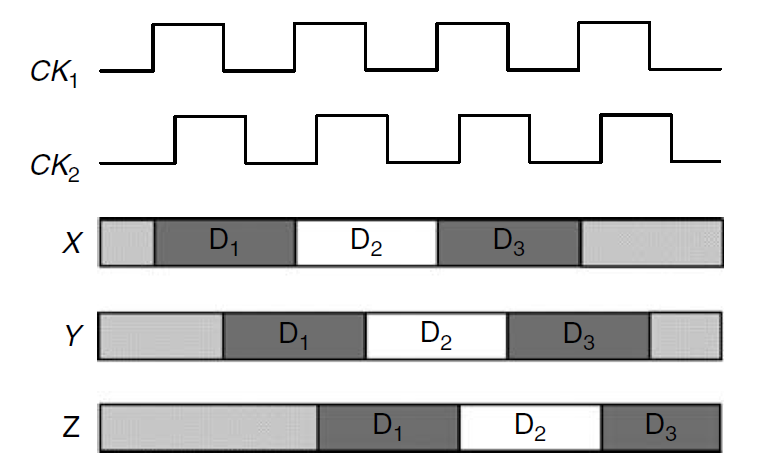

当一个scan-chain的scan cell来自不同的clock domain时,一个lock-up latch需要插入。

这样可以保证,不论CK2优先CK1还是CK1优先CK2,shift的操作都是正确的。

但是必须保证CK1和CK2之间的skew少于一个duty cycle。

当scan chain的clock结构定下来以后,进行scan cell的stitch到scan chain以及这些scan cell的

place,stitch以最小化scan routing为目标。

Scan Replacement:

经过scan configuration,scan replacement将storage element替换为functionally equivalent scan cell

这时的design叫做,scan-ready design。

这些scan cell的input通常连接到同一个scan cell的output来避免floating。这些连接在stitch阶段去除。

目前,在RTL阶段也可以实现部分的scan replacement。

Scan Reordering

反应scan chain中scan cell的reorder。在物理实现之前,一个random的scan order被design使用。

在进行physical implementation时,scan order可以使用intra_scan_chain reordering(scan cell只在该scan

chain内进行reorder)和inter_scan_chain reordering(scan cell在不同的scan chain之间reorder)

scan stitching

将所有的scan cell stitch到一起,组成scan chain。将每一个scan cell的output连接到下一级的input。

将第一个scan cell的input连接到primary input,最后一个scan cell的output连接到primary output。

在stitch的过程中,需要插入一些lock_up的latch和lock_up的FF来保证shift操作正确。

scan design flow(一)的更多相关文章

- scan design flow(二)

在scan stitch之后,scan synthesis就已经完成, Scan extraction主要用来从scan design中extracing所有的instance,来保证scan cha ...

- Atitit vod click event design flow 视频点播系统点击事件文档

Atitit vod click event design flow 视频点播系统点击事件文档 重构规划1 Click cate1 Click mov4 重构规划 事件注册,与事件分发管理器分开 ...

- scan design rules

为了更好的设计一个scan design,一些scan design的rule必须遵循. 1)tristate bus在shift mode下必须保持bus contention: 2)bidirec ...

- FPGA design flow

FPGA engineering process usually involves the following stages: Architecture design. This stage invo ...

- scan cell

scan cell有两种不同的input: 1)data input:由电路的combinational logic驱动: 2)scan input:由另一个scan cell驱动,从而形成scan ...

- scan & ATPG

Testability用来表征一个manufactured design的quality. 将testability放在ASIC前端来做,成为DFT(Design For Test),用可控(cont ...

- SMTS Silicon Design Engineer Location: Beijing, Beijing, CN

https://jobs.amd.com/job/Beijing-Physical-Design-Engineer-Beij/603603700/?locale=en_US What you do a ...

- ARM JTAG 信号 RTCK 应该如何处理?

用户在调试内嵌可综合内核的 CPU 如 ARM7TDMI-S 时,需要通过打开仿真器的自适应时钟功能. 此时,ARM仿真器根据 RTCK 时钟信号的频率,产生可用于 CPU 内核当前时钟主频的最快的 ...

- DFT 问答 III

1.Boundary scan Boundary Scan就是我们俗称的边界扫描.Boundary Scan是上世纪90年代由 Joint Test Action Group(JTAG)提出的,它的初 ...

随机推荐

- C++ 简易时间类

.h file #ifndef LIBFRAME_DATETIME_H_ #define LIBFRAME_DATETIME_H_ #include <stdint.h> #include ...

- [LeetCode]题解(python):038-Count and Say

题目来源 https://leetcode.com/problems/count-and-say/ The count-and-say sequence is the sequence of inte ...

- Combine String---hdu5727 &&& Zipper(LCS变形)

题目链接:http://poj.org/problem?id=2192 http://acm.split.hdu.edu.cn/showproblem.php?pid=5707 http://acm. ...

- HighCharts -教程+例子

Highchart简介: Highcharts是一款免费开源的纯javascript编写的图表库,能够很简单便捷的在Web网站或Web应用中添加交互性的图表, Highcharts目前支持直线图 ...

- js方法参数默认值设置

这里的默认值设置 很容易以为和php相似 function(v1,v2="test") { alert(v2); } 但这样是不对的,js方法,如需传参,甚至可以不用预定义(也就是 ...

- std::map的clear()没有用?

昨天晚上,我徒弟跑过来讲,他的程序的内存占用居高不下,愿意是std::map的clear()没有效果.于是我让他用erase(begin,end); 试试也不行. 代码如下: void release ...

- imx6 otg host support

本文记录添加imx6 otg host支持的过程. 参考链接 http://www.cnblogs.com/helloworldtoyou/p/6108560.html https://communi ...

- 创建数据库和表的SQL语句

创建数据库的SQL语句: 1 create database stuDB 2 on primary -- 默认就属于primary文件组,可省略 3 ( 4 /*--数据文件的具体描述--*/ 5 n ...

- ps、grep和kill联合使用杀掉进程(转)

例如要杀掉hello这个进程,使用下面这个命令就能直接实现. ps -ef |grep hello |awk '{print $2}'|xargs kill -9 这里是输出ps -ef |gre ...

- Linux下获取公网IP地址

curl http://members.3322.org/dyndns/getipcurl http://ip.6655.com/ip.aspx