Verilog (一) assignment, register and net

Verilog 大小写敏感,且所有关键字都是小写

1 寄存器

register = storage,是数据存储单元的抽象,可视为能够存储数值的变量 (variable that can hold value)

关键字 reg; 缺省值 x;

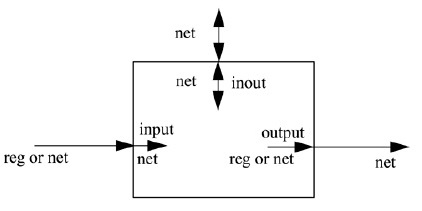

2 网络连接

net = connection, 表示寄存器之间的连接,只能采用连续赋值 (must be driven continuously)

关键字 wire; 缺省值 z;

2.1 D 触发器 (同步复位)

module dff(clk, rst, d, q); //dff with syn reset

input clk, rst, d;

output q;

reg q; always @(posedge clk)

begin

if (rst)

q <= 'b0;

else

q <= d;

end endmodule

2.2 D 触发器 (异步复位)

module dff(clk, rst, d, q); // dff with asyn reset

input clk, rst, d;

output q;

reg q; always @(posedge clk or posedge rst)

begin

if (rst)

q <= 'b0;

else

q <= d;

end endmodule

3 连续赋值 continuous assignment

assign data_left = data_right; // right drive left(net)

例:选择器 mux

assign data_out = select ? data_in1 : data_in0;

4 procedural assignment

1) 阻塞赋值 ("=")

execute sequential

2) 非阻塞赋值 ("<=")

read (right) -> schedule (left) -> execute (<=)

例: synchronizer

reg [:] data_sync; always @ (posedge clk or posedge rst)

begin

if (rst)

data_sync <= 'b00;

else

data_sync <= {data_sync[], data_in};

end assign data_out = data_sync[];

Verilog (一) assignment, register and net的更多相关文章

- Quartus II 中 Verilog 常见警告/错误汇总

Verilog 常见错误汇总 1.Found clock-sensitive change during active clock edge at time <time> on regis ...

- 对Verilog 初学者比较有用的整理(转自它处)

*作者: Ian11122840 时间: 2010-9-27 09:04 ...

- Quartus II中的Waring(转)

1.Found clock-sensitive change during active clock edge at time <time> on register "<n ...

- [转载]Quartus ii 一些Warning/Eeror分析与解决

我会在此基础上继续添加 原文地址:ii 一些Warning/Eeror分析与解决">Quartus ii 一些Warning/Eeror分析与解决作者:yanppf 注:http:// ...

- quartus II Warning 好的时序是设计出来的,不是约束出来的

一.Warning (15714): Some pins have incomplete I/O assignments. Refer to the I/O Assignment Warnings r ...

- Verilog-1995 VS Verilog-2001

http://www.cnblogs.com/tshell/p/3236476.html 2001年3月IEEE正式批准了Verilog‐2001标准(IEEE1364‐2001),与Verilog‐ ...

- uboot之at91sam9g45移植

一.第一阶段,无修改 二.第二阶段 u-boot-1.3.4\lib_arm\board.c 1.增加头文件 2.增加版本号 3.start_armboot中初始化部分 板级初始化部分init_seq ...

- verilog behavioral modeling--procedural continous assignment(不用)

assign / deassgin force /release the procedural continuous assignments(using keywords assign and for ...

- Verilog Tips and Interview Questions

Verilog Interiew Quetions Collection : What is the difference between $display and $monitor and $wr ...

随机推荐

- php实现添加图片水印

实际运行时需要开启php 的gd2功能,运行环境php4.0以上(demo中的路径改为实际路径) <?php/*打开图片*/ //1.配置图片路径 $src="image/61.jpg ...

- 「C语言」单链表/双向链表的建立/遍历/插入/删除

最近临近期末的C语言课程设计比平时练习作业一下难了不止一个档次,第一次接触到了C语言的框架开发,了解了View(界面层).Service(业务逻辑层).Persistence(持久化层)的分离和耦合, ...

- 「C语言」Windows+EclipseCDT下的C语言开发环境准备

之前写过一篇 「C语言」在Windows平台搭建C语言开发环境的多种方式 ,讨论了如何在Windows下用DEV C++.EclipseCDT.VisualStudio.Sublime Test.Cl ...

- jquery只能输入数字方法

本方法为验证文本框的输入内容,如果输入的是数字,则提示"√".否则提示“必填,且只能输入数字字符”.在线体验效果:http://keleyi.com/keleyi/phtml/zz ...

- javascript宿主对象之window.screen、window.close()/open()、window.moveTo、window.resizeTo

window.screen属性所提供的是浏览器以外的信息.这里只简单的概述一下: screen.availWidth - 可用的屏幕宽度 (除去操作系统菜单) screen.availHeight - ...

- ssh无法登录linux服务器的解决办法

最近之前使用的一台linux服务器被长官重装系统了,导致ssh登录的时候出现如下错误: @@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@ ...

- Opengles 管线编程介绍

OpenGL ES 2.0可编程管道 上图橙色部分(Vertex Shader和Fragment Shader)为此管道的可编程部分.整个管道包含以下两个规范: 1) OpenGL ...

- virtualbox迁移至vcenter/vmware workstation

参考文献: http://www.itsecurenet.com/virtualbox-ova-to-vsphere-ovf/ http://www.techrepublic.com/blog/win ...

- iOS多线程技术

iOS多线程技术主要分配NSThread.NSOperation和GCD.下边来简单的介绍一下吧. 随性一点,就不按照顺序来了.所以先介绍一下NSOperation. ---------------- ...

- UINavigationBar 和 UINavigationItem的属性设置

#import "RootViewController.h" @interface RootViewController () @end @implementation RootV ...