Verilog (一) assignment, register and net

Verilog 大小写敏感,且所有关键字都是小写

1 寄存器

register = storage,是数据存储单元的抽象,可视为能够存储数值的变量 (variable that can hold value)

关键字 reg; 缺省值 x;

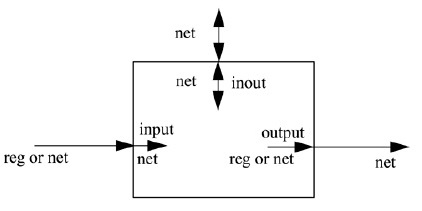

2 网络连接

net = connection, 表示寄存器之间的连接,只能采用连续赋值 (must be driven continuously)

关键字 wire; 缺省值 z;

2.1 D 触发器 (同步复位)

module dff(clk, rst, d, q); //dff with syn reset

input clk, rst, d;

output q;

reg q; always @(posedge clk)

begin

if (rst)

q <= 'b0;

else

q <= d;

end endmodule

2.2 D 触发器 (异步复位)

module dff(clk, rst, d, q); // dff with asyn reset

input clk, rst, d;

output q;

reg q; always @(posedge clk or posedge rst)

begin

if (rst)

q <= 'b0;

else

q <= d;

end endmodule

3 连续赋值 continuous assignment

assign data_left = data_right; // right drive left(net)

例:选择器 mux

assign data_out = select ? data_in1 : data_in0;

4 procedural assignment

1) 阻塞赋值 ("=")

execute sequential

2) 非阻塞赋值 ("<=")

read (right) -> schedule (left) -> execute (<=)

例: synchronizer

reg [:] data_sync; always @ (posedge clk or posedge rst)

begin

if (rst)

data_sync <= 'b00;

else

data_sync <= {data_sync[], data_in};

end assign data_out = data_sync[];

Verilog (一) assignment, register and net的更多相关文章

- Quartus II 中 Verilog 常见警告/错误汇总

Verilog 常见错误汇总 1.Found clock-sensitive change during active clock edge at time <time> on regis ...

- 对Verilog 初学者比较有用的整理(转自它处)

*作者: Ian11122840 时间: 2010-9-27 09:04 ...

- Quartus II中的Waring(转)

1.Found clock-sensitive change during active clock edge at time <time> on register "<n ...

- [转载]Quartus ii 一些Warning/Eeror分析与解决

我会在此基础上继续添加 原文地址:ii 一些Warning/Eeror分析与解决">Quartus ii 一些Warning/Eeror分析与解决作者:yanppf 注:http:// ...

- quartus II Warning 好的时序是设计出来的,不是约束出来的

一.Warning (15714): Some pins have incomplete I/O assignments. Refer to the I/O Assignment Warnings r ...

- Verilog-1995 VS Verilog-2001

http://www.cnblogs.com/tshell/p/3236476.html 2001年3月IEEE正式批准了Verilog‐2001标准(IEEE1364‐2001),与Verilog‐ ...

- uboot之at91sam9g45移植

一.第一阶段,无修改 二.第二阶段 u-boot-1.3.4\lib_arm\board.c 1.增加头文件 2.增加版本号 3.start_armboot中初始化部分 板级初始化部分init_seq ...

- verilog behavioral modeling--procedural continous assignment(不用)

assign / deassgin force /release the procedural continuous assignments(using keywords assign and for ...

- Verilog Tips and Interview Questions

Verilog Interiew Quetions Collection : What is the difference between $display and $monitor and $wr ...

随机推荐

- JPA学习(1)基础认知

JPA 是什么 Java Persistence API:用于对象持久化的API. Java EE 5.0 平台标准的 ORM 规范,使得应用程序以统一的方式访问持久层: JPA和Hibernate的 ...

- struts2进阶篇(5)

一.OGNL简介 OGNL (Object-Graph Navigation Language)的缩写,简称对象图导航语言. OGNL表达式的特特点: >能够取对象的属性,也能调用对象的方法. ...

- T-SQL的回车和换行符(SQL)

T-SQL的回车和换行符(SQL) sql server中的回车换行字符是 char(13)+char(10) 回车:char(13) 换行:char(10) 实例1: DECLARE @c NVA ...

- ahjesus Unity3D XML注释被编译的问题

public class XMLStringReader : MonoBehaviour { public string slectedItem; private bool editing = fal ...

- 胖AP(1602i)与苹果设备之间的问题总结

问题现象: 苹果设备(5GHz)连接不稳定,表现为时断时续,或者加入无线的时候一直加入不进去. 有些2.4GHz设备会在几个AP之间相互跳. 分析: 1. 先说苹果设备,它既支持2.4G 也支持5G, ...

- img标签src不给路径就会出现边框————记一次二笔的编码经历

<img/>在src加载失败或没有给的,浏览器会自动给img加上边框. 如下图这样: 产品觉得影响美观,一定要pass掉. 原码是这样: .ctn{ position: relative; ...

- 在IntelliJ IDEA14中安装go语言插件

go语言的集成开发环境仍不成熟,试用了liteide,感觉很不适应,弹出菜单对程序员的干扰太大.所以就试大牌的IntelliJ IDEA,这工具本来是JAVA开发阵营的,不过它已经变为一个非常强大的支 ...

- 迭代器 iterator(二): 用iterator遍历arraylist

迭代器(iterator)是一种对象,它能够用来遍历标准模板库容器中的部分或全部元素,每个迭代器对象代表容器中的确定的地址.迭代器修改了常规指针的接口,所谓迭代器是一种概念上的抽象:那些 ...

- Python数据结构与算法--List和Dictionaries

Lists 当实现 list 的数据结构的时候Python 的设计者有很多的选择. 每一个选择都有可能影响着 list 操作执行的快慢. 当然他们也试图优化一些不常见的操作. 但是当权衡的时候,它们还 ...

- 【原/转】opencv的级联分类器训练与分类全程记录

众所周知,opencv下有自带的供人脸识别以及行人检测的分类器,也就是说已经有现成的xml文件供你用.如果我们不做人脸识别或者行人检测,而是想做点其他的目标检测该怎么做呢?答案自然是自己训练一个特定的 ...