低功耗设计技术--Multi VDD--Level shifter

本文转自:自己的微信公众号《集成电路设计及EDA教程》

前面的推文中我们分别介绍了低功耗设计中的Multi-VDD技术以及门控电源技术。在实际的低功耗设计中,门控电源技术中也常常结合Multi-VDD技术一起使用。

在使用了Multi-VDD技术之后,设计中会形成多个Power Domain(PD):

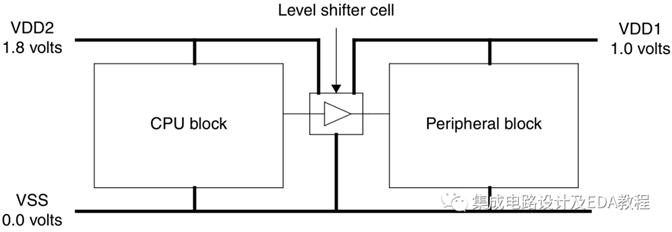

不同Power Domain之间如果需要数据的Talk,那么在中间需要插入Level Shifter(电平转换单元):

本推文我们来讲解一下第二个特殊的Cell -- Level Shifter。

Level shifter Cell

Level Shifters主要是多供电电压(MSV)的设计中,在2个不同电压域之间有数据交互的情况下,需要将某个电压域输出的电平转换成另一个电压域可以识别的逻辑电平,因此需要用到电平转换的器件,这就是Level Shifter。这种Cell在我们使用的IO中也广泛存在,用于将外部的电压与Core电压之间进行转换。

根据电平转换的方向,Level Shifter可以分为三种:

HL -> 高电平转低电平

LH -> 低电平转高电平

HL_LH -> 双向转换均可

另外,如果设计中还采用了前面推文中讲的Power Gating技术,在不通电压域之间进行通信的情况下,除了需要添加Level Shifter之外还需要用到另外一种Cell -> Isolation Cell。因为电源关断之后,其驱动的电路就出现了输入浮空的情况,它的输入会处于高阻态,会用泄放电流将上面的电荷缓慢泄放掉,再次期间,其状态是不能确定的(如下图所示)。因此,为了解决这个问题,我们需要在电源关闭电路的输出端添加一个隔离单元(Isolation Cell)将输出钳位到一个确定的状态。

一般来说Isolation Cell的输出部分有较大的电容负载,也就是说Isolation Cell的延时将会比较大,对时序有一定的影响,是需要注意的。

关于Isolation Cell的详细内容下篇推文单独讲。

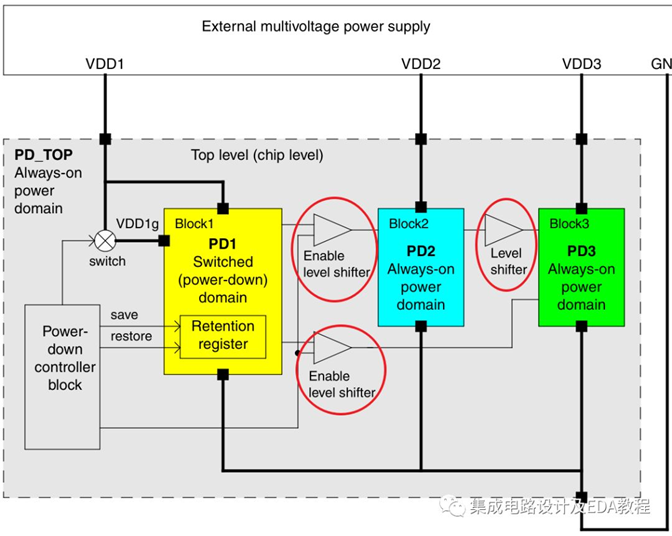

如果设计中含有Multi-VDD且有的Power Domain可以被关断,多个Domain之间还有数据交互,那么既需要用到Level Shifter也需要Isolation Cell,这种情况也非常常见。因此一般Foundary都会那种带有Isolation功能的Level shifter,兼两种功能。

下图就是这种情况,PD1是可被关断的,它与PD2以及PD3之间用的Level Shifter就是带有Isolation功能的Level Shifter。而PD2是Always On的,所以它送到PD3的数据只需要用普通的Level Shifter即可。

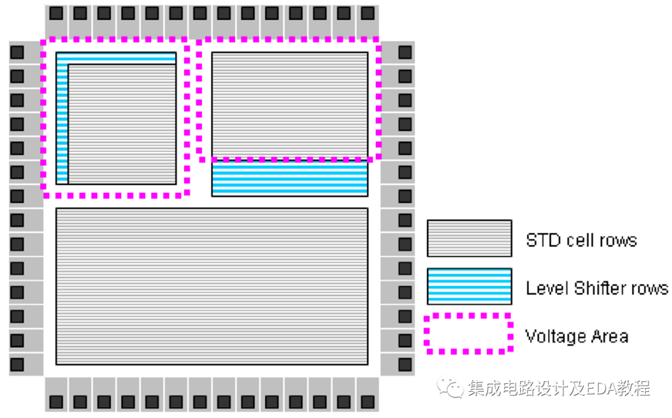

Level Shifter的物理布局

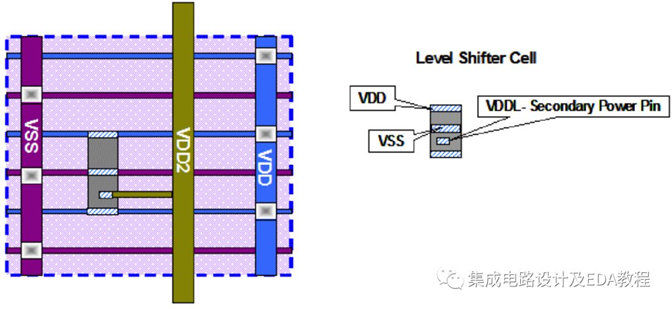

Level shifter是 Always-on Cell,一般有多个电源地Pin。它们的结构比较复杂,一般要比普通的Cell高度要高,它们的作用非常关键,我们需要保证它们的电源地连接是正确的。

考虑到以上因素,很多设计会采用下面的方案来摆放Level Shifter,将它们放置在特定区域内,Level Shifter的电源地Rail以及PG Pin的连接也更加规范有条理:

如下图所示为Dual Height的Level shifter Cell在版图中的摆放及其PG Pin的连接:

上面这种PG的连接特别的不方便,可能会占用较多的Routing Resources引起DRC。

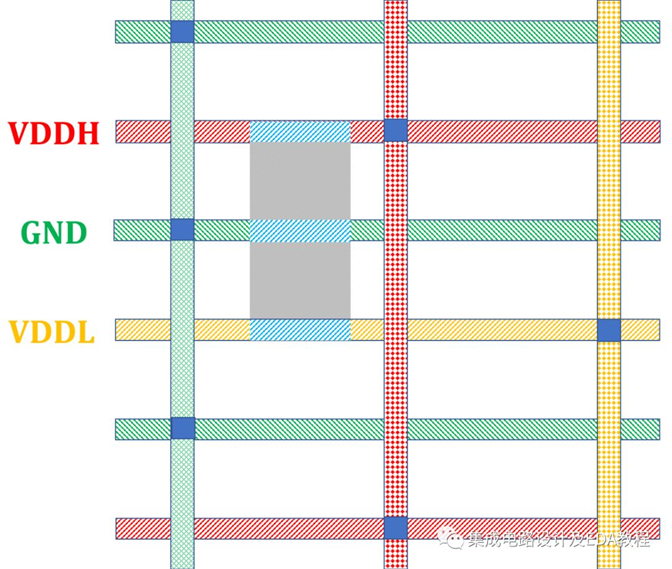

除此之外,还可以采用下面的双Power Rail的方式,Level shifter横跨两个Rail的高度,两个不同的VDD,一个GND。

下面描述的是Level Shifter的Liberty格式:

|

cell(level_shifter) { is_level_shifter : true ; #定义为true,则该Cell被认为是lever shifter cell level_shifter_type : HL | LH | HL_LH ; #定义电平转换方向,HL表示高电平转低电平,LH表示低电平转高电平,HL_LH表示都可以用 input_voltage_range (<float>, <float>); #输入电压范围,指该Cell输入连接的电路,电压工作范围,EDA工具会根据Operating Condition的选择,检查该Cell是否满足电路需要,可以在功能pin中进行定义,如果在cell主体定义,则必须与output_voltage_range同时存在 output_voltage_range (<float>, <float>);#输出电压范围,指该Cell输出连接的电路,电压工作范围,EDA工具会根据Operating Condition的选择,检查该Cell是否满足电路需要,可以在功能pin中进行定义,如果在cell主体定义,则必须与input_voltage_range同时存在 … pg_pin(<pg_pin_name_P>) { pg_type : primary_power; std_cell_main_rail : true; #该primary_power连接在Cell设计中的主rail … } pg_pin(<pg_pin_name_G>) { pg_type : primary_ground; … } pin (data) { direction : input; input_signal_level : “<voltage_rail_name>”; #输入信号电压环名 input_voltage_range ( <float> , <float>); level_shifter_data_pin : true ; #数据功能Pin … }/* End pin group */ pin (enable) { direction : input; input_voltage_range ( <float> , <float>); level_shifter_enable_pin : true ; #使能Pin,如果level shifter还作为isolation cell的时候,使能信号会在电源关闭时停止level shifter功能,仅仅作为isolation cell存在 … }/* End pin group */ pin (output) { direction : output; output_voltage_range ( <float> , <float>); power_down_function : (!pg_pin_name_P + pg_pin_name_G); … }/* End pin group */ … }/* End Cell group */ #power_down_function 属性用来识别出何时output pin处于电源被关断的状态。 The power_down_function string attribute is used to identify the condition when an output pin is switched off by pg_pin and to specify the Boolean condition under which the cell’s output pin is switched off (when the cell is in "off" mode due to the external power pin states) |

参考文献:

孙轶群 ,国民技术股份有限公司,数字集成电路低功耗物理实现技术与UPF

Synopsys Low-Power Flow User Guide

低功耗设计技术--Multi VDD--Level shifter的更多相关文章

- (数字IC)低功耗设计入门(三)——系统与架构级

前面讲解了使用EDA工具(主要是power compiler)进行功耗分析的流程,这里我们将介绍在数字IC中进行低功耗设计的方法,同时也结合EDA工具(主要是Design Compiler)如何实现. ...

- (数字IC)低功耗设计入门(六)——门级电路低功耗设计优化

三.门级电路低功耗设计优化 (1)门级电路的功耗优化综述 门级电路的功耗优化(Gate Level Power Optimization,简称GLPO)是从已经映射的门级网表开始,对设计进行功耗的优化 ...

- Retimer、Redriver(Level Shifter)

重定时器Retimer和驱动器Redriver9(Level Shifter) 在高速串行通道的信号传输中,需要使用Redriver 和Retimer来保证信号传输的质量. Redriver,可以重新 ...

- MCU低功耗设计(三)产品

关键词: 低功耗设计, 无线通信产品, LoRa长距离, Contiki系统, 能耗实时跟踪 引言: 能耗对电池供电的产品来说是一个重大问题.一旦电能耗尽设备将"罢工".在< ...

- 高性能的EMI滤波器及其小型化设计技术

1 EMI滤波器的常见问题及发展趋势首先介绍了影响EMI滤波器性能/体积的因素及EMI滤波器的常见问题:低频传导发射高.高频传导/辐射发射高.体积大,从而分析出EMI滤波器的发展趋势为高性能和小体积, ...

- (数字IC)低功耗设计入门(一)

低功耗设计这个专题整理了好久,有一个月了,有图有证据: 然而最近一直有些烦心事.郁闷事,拖延了一下,虽然现在还是有点烦,但是还是先发表了吧.下面我们就来聊聊低功耗设计吧,由于文章比较长,因此我就不一次 ...

- (数字IC)低功耗设计入门(四)——RTL级低功耗设计

二.RTL级低功耗设计 前面介绍了系统级的低功耗设计,换句话说就是在系统级降低功耗可以考虑的方面.系统级的低功耗设计,主要是由系统级设计.具有丰富经验的人员实现,虽然还轮不到我们设计,我们了解一下还是 ...

- (数字IC)低功耗设计入门(五)——RTL级低功耗设计(续)

二.RTL级低功耗设计(续) 前面一篇博文我记录了操作数隔离等低功耗设计,这里就主要介绍一下使用门控时钟进行低功耗设计. (4)门控时钟 门控时钟在我的第一篇博客中有简单的描述,这里就进行比较详细的描 ...

- (数字IC)低功耗设计入门(七)——门级电路低功耗设计优化(续)

前面讲解了门级功耗的优化方法,包括静动态和总体的功耗.现在来记录一下门级层次(有点书也说是在系统级)常用的一种低功耗方法--电源门控. ①电源门控概述与原理 电源门控是指芯片中某个区域的供电电源被关掉 ...

随机推荐

- 【题解】[HNOI2015]菜肴制作(贪心+topo序)

[题解][HNOI2015]菜肴制作(贪心+topo序) 题意:请你构造一个排列\(p[i]\)使得对于数组\(arc[i]=p[i]\)的字典序最小,并且对于给定的有序数对\((u,v)\)保证你给 ...

- [01]java基础回顾

00 Java语言 由美国SUN公司发明于1995年,是目前业界应用最广泛.使用人数最多的语言,连续多年排名世界第一,可以称之为“计算机语言界的英语”. Java广泛应用于企业级软件开发. ...

- 「USACO15FEB」Censoring (Silver) 审查(银) 解题报告

题面 就是让你--在字符串A中,如果字符串B是A的子串,那么就删除在A中第一个出现的B,然后拼接在一起,一直重复上述步骤直到B不再是A的子串 |A|\(\le 10^6\) 思路: KMP+栈 1.由 ...

- JAVA8学习——Stream底层的实现三(学习过程)

Stream的深入(三) 心得:之前学习流,深入了流的底层.但是学的这些东西在平时日常开发的过程中,是根本不会用到的.只是为了更好帮助自己去理解流的底层设施.用起来也更自信,能够确定用的东西非常正确. ...

- 《图解机器学习-杉山将著》读书笔记---CH3

CH3 最小二乘学习法 重点提炼 提出最小二乘学习法的缘故: 最小二乘学习法公式 对不同模型进行最小二乘法学习,得到最小二乘公式中的参数theta: 1.线性模型 代入3.1公式,对参数求偏导,偏 ...

- Spring多数据源动态切换

title: Spring多数据源动态切换 date: 2019-11-27 categories: Java Spring tags: 数据源 typora-root-url: ...... --- ...

- 转型IT学什么语言好,学编程语言为何要重视代码规范?

造价转IT需要注意什么,先学什么比较好?属于零基础,2019毕业,三本学校,男.自己的想法是先以副业来学习,在合适的时候转入it行业.1.以副业来学的话应该先学习什么比较好?2.如果要直接找工作的话先 ...

- Rust入坑指南:海纳百川

今天来聊Rust中两个重要的概念:泛型和trait.很多编程语言都支持泛型,Rust也不例外,相信大家对泛型也都比较熟悉,它可以表示任意一种数据类型.trait同样不是Rust所特有的特性,它借鉴于H ...

- MQ队列及常见操作

一. 创建MQ队列管理器 1.1准备工作 到所安装websphere mq的机子上,进入/opt/mm/bin目录下,查询相关mq的情况,通过命令行./dspmq. 创建mq队列管理器的的时候要用mq ...

- UIBPlayer (视频播放)demo分享

本文出自APICloud官方论坛 UIBPlayer 封装了百度云播放器 SDK.本模块带有UI方案,打开后为一个具有完整功能的播放器界面.百度云播放器突破 Android.iOS 平台对视频格式的限 ...