report_delay_calculation/check_timing/report_annotated_parasitics/report_analysis_coverge

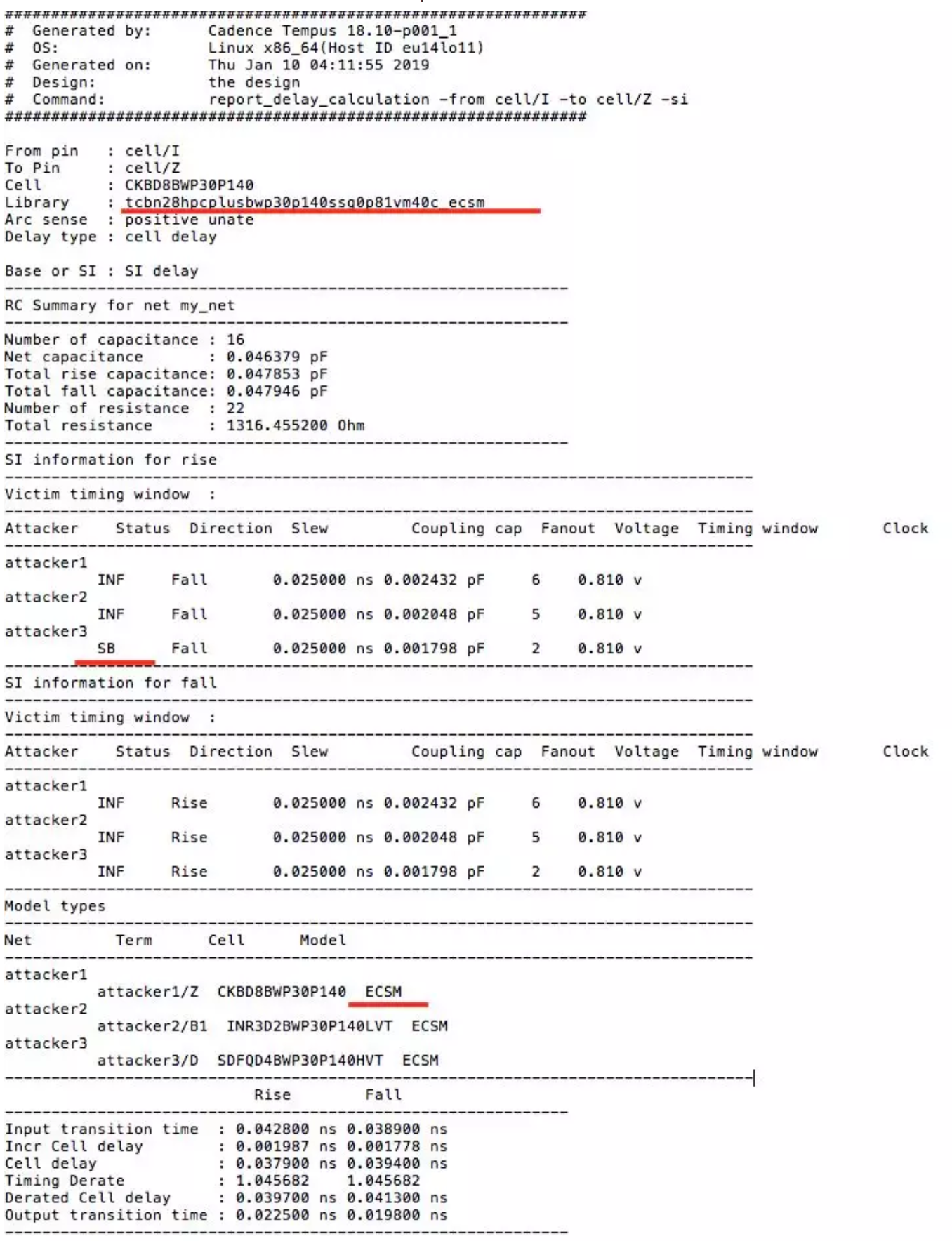

如何debug 一颗cell 或一段net 的delay, 常用的办法是用report_delay_calculation 报这颗cell 或这段net, 会得到形式如下的report, 从该report 中可以得到:

表头需要特别关注的是command, 确定report 的对象及加的option;

From/To pin: cell 的input pin 和 output pin;

Cell: 该cell 对应的lib cell;

Library: 该cell 来自哪个lib, 需要特别关注一下,确定用的lib 正确,避免低级错误;

Arc sense: Arc sense 分三种positive unate, negetive unate, non unate; 输出信号同输入信号跳变方向相同的称为positive unate 如buffer 的timing arc; 输出信号同输入信号跳变方向相反的称为negetive unate 如inverter 的timing arc; 输出信号的跳变方向由另一个输入信号的值决定称为non unate 如xor 的timing arc;

Delay type: 标示是cell delay 还是net delay;

Base or SI: 因为加了option -si, 所以当前是SI delay;

RC summary for net: 从这一块可以得到电容电阻个数、net 电容值、总上升电容值、总下降电容值、总电阻值。这部分信息在debug 不同工具间的correlation 时非常有用。

SI information: 从这一块可以得到所有的attacker 信息,及每个attcker 的status, direction, slew, coupling cap, fanout, voltage, timing window, clock. 另外还可以得到attacker 的model type 要特别注意用的是什么model, 是NLDM, CCS, ECSM, 示例中是ECSM, 这一点同样在debug 不同工具间的correlation 时至关重要。

delay information: 从这一块可以分别得到rise/fall 的输入transition, incr cell delay (由cross talk 造成的delay), cell delay, timing derate, derated cell delay, output transition.

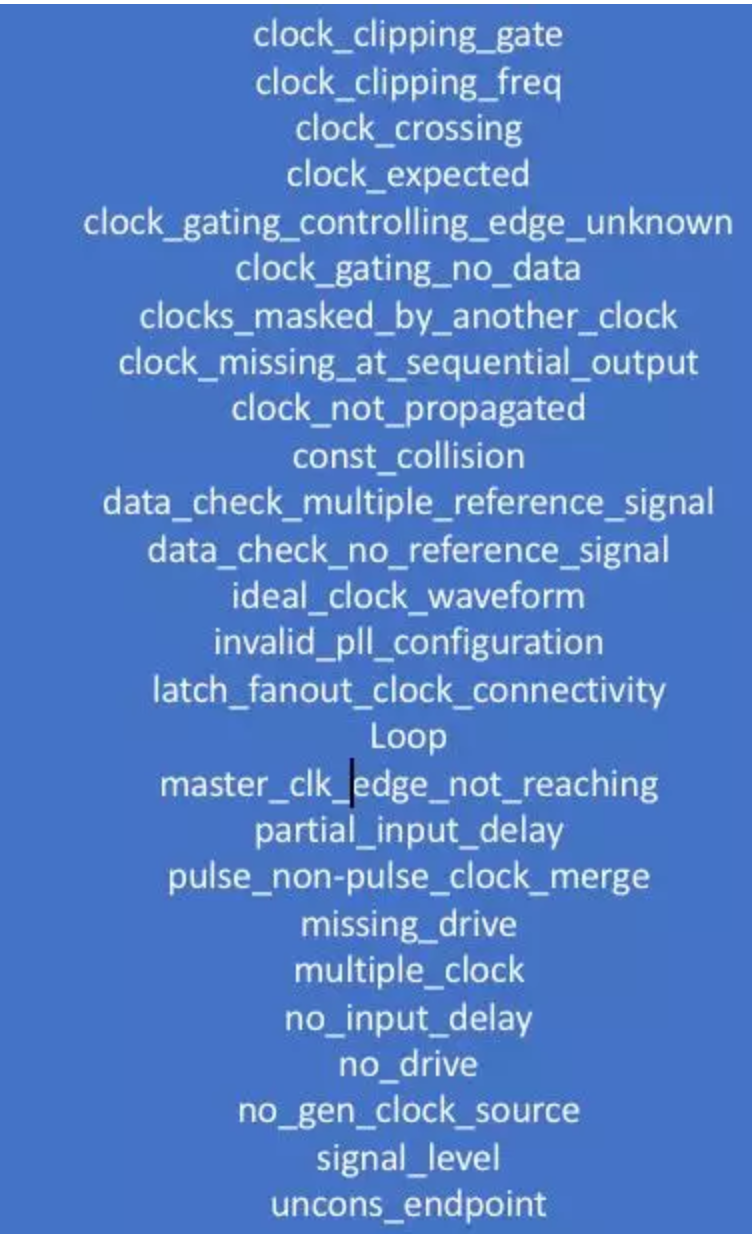

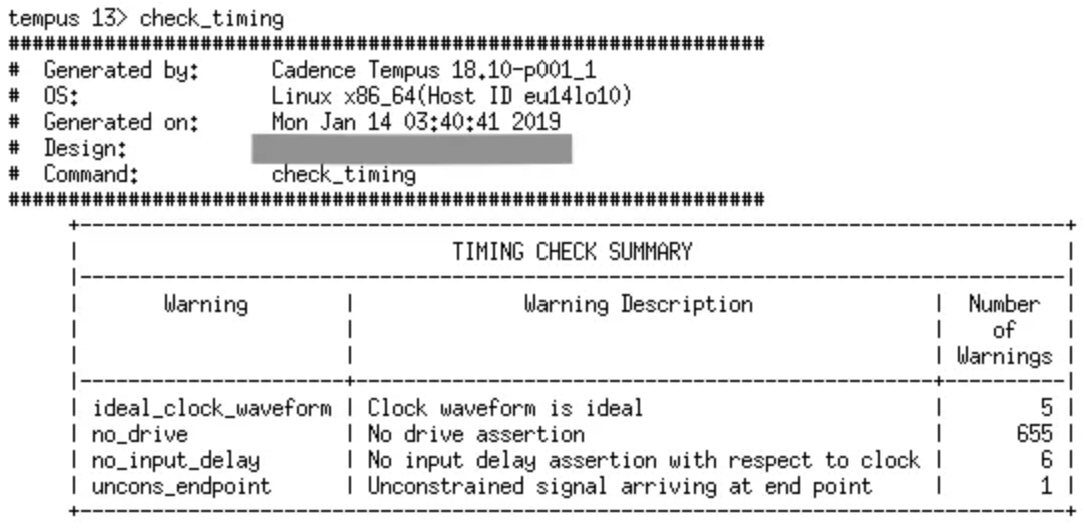

check_timing

用于check SDC 的quality, 会check 以下列出的内容,可以概括为:少了什么、多了什么、冲突了什么、错了什么;SDC 可以看作是STA 的『法规』,所以对制定者要高要求,STA 工具并不能check 出SDC 中所有的问题,有一些问题必须由设计者负责,如multi-cycle 设多少,写SDC 时是否手一抖把不该设false path 的地方设了false path, 这些人为大坑是STA 工具没办法check 到的。复杂SDC 的quality 通常需要用CDC 工具去做check, 除了SDC 本身还需要check 设计中是否放了正确的同步电路等。

需要对check_timing 报出的warning 做细致check, 把需要修的都修掉,可以忽略的都要有明确的原因。

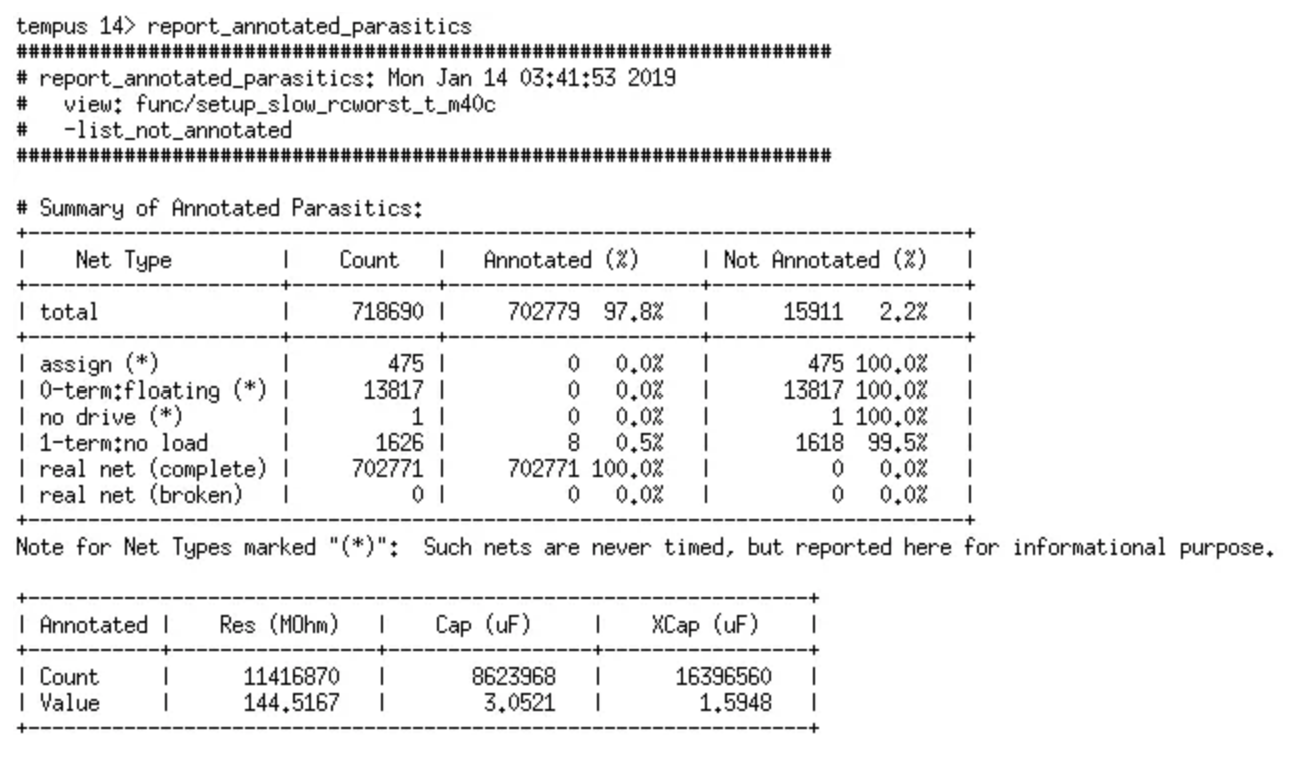

report_annotated_parasitics

用于check RC的反标情况,要保证所有的real net 都可以被正确反标上,如果有未反标的net, 需要去找抽RC 的坑友确认。首先确认数据是否匹配,再确认是否做了该做的change_name 动作,再确认除了real net 之外的其他warning, 为什么有assign 为什么有dangling net, 最好让坑友一齐处理掉,看着清爽。

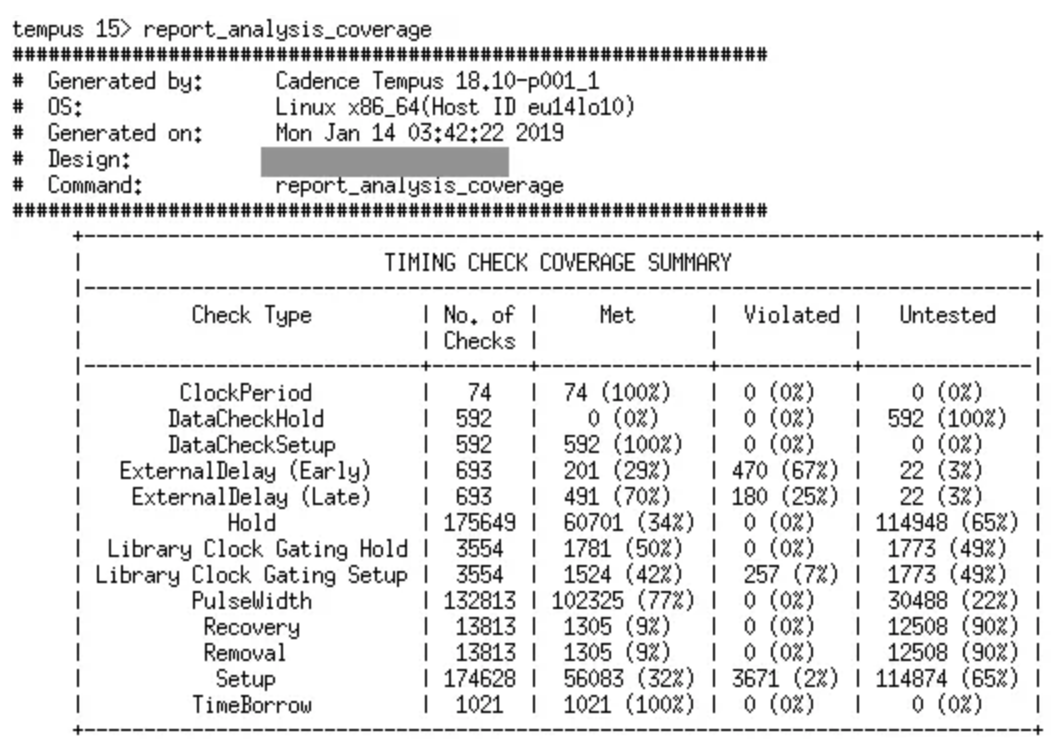

report_analysis_coverge

check STA coverge: check 设计中有多少需要check 的东西,在当前约束下,总共有多少被check 到了,多少没有被check 到,check 到的有哪些满足了需求有哪些没有满足。这个report 很重要,如果是初次分析最好把每一项的详细信息报出来,列一张表,对没有被check 到的部分进行分类,并对每一类归因。

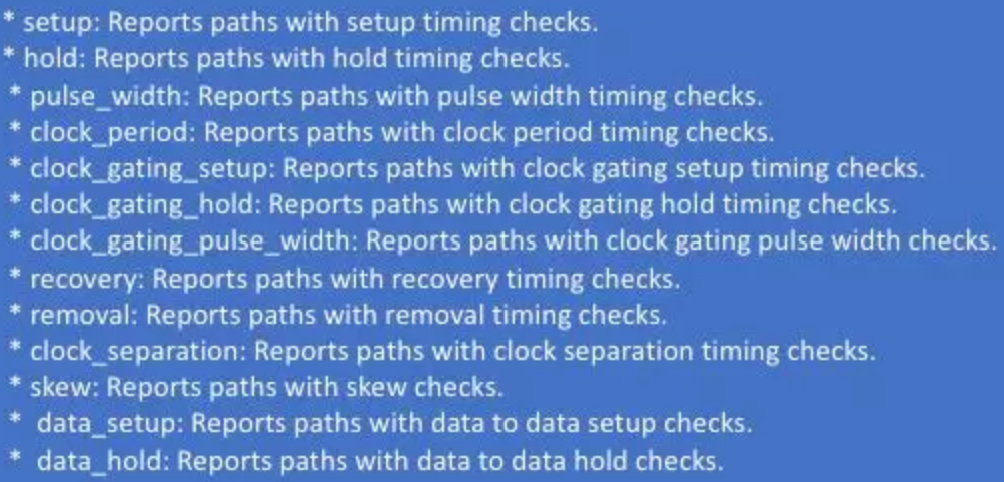

Tempus 中分成以下几类check , 不同工具大同小异。

report_delay_calculation/check_timing/report_annotated_parasitics/report_analysis_coverge的更多相关文章

- Prime Time使用

PrimeTime一般用作sign off的timing check,也可用在DC之后的netlist的timing analysis 一般的使用流程: 1) Read design data,--- ...

- Timing path

Timing path:从register clock/input port开始,经过一些combinational logic,终止在register data/output port. PT以pa ...

- Tcl与Design Compiler (六)——基本的时序路径约束

本文属于原创手打(有参考文献),如果有错,欢迎留言更正:此外,转载请标明出处 http://www.cnblogs.com/IClearner/ ,作者:IC_learner 时序约束可以很复杂,这 ...

- Tcl与Design Compiler (八)——DC的逻辑综合与优化

本文属于原创手打(有参考文献),如果有错,欢迎留言更正:此外,转载请标明出处 http://www.cnblogs.com/IClearner/ ,作者:IC_learner 对进行时序路径.工作环 ...

- Tcl与Design Compiler (十二)——综合后处理

本文如果有错,欢迎留言更正:此外,转载请标明出处 http://www.cnblogs.com/IClearner/ ,作者:IC_learner 概述 前面也讲了一些综合后的需要进行的一些工作,这 ...

- Tcl与Design Compiler (十三)——Design Compliler中常用到的命令(示例)总结

本文如果有错,欢迎留言更正:此外,转载请标明出处 http://www.cnblogs.com/IClearner/ ,作者:IC_learner 本文将描述在Design Compliler中常用 ...

- Tcl与Design Compiler (五)——综合库(时序库)和DC的设计对象

本文如果有错,欢迎留言更正:此外,转载请标明出处 http://www.cnblogs.com/IClearner/ ,作者:IC_learner 前面一直说到综合库/工艺库这些东西,现在就来讲讲讲 ...

- Vivado Design Suite用户指南之约束的使用第二部分(约束方法论)

Constraints Methodology(约束方法论) 关于约束方法论 设计约束定义了编译流程必须满足的要求,以使设计在板上起作用. 并非所有步骤都使用所有约束在编译流程中. 例如,物理约束仅在 ...

- standard cell timing model

standard cell timing model 主要包括两方面的信息: Cell Delay calculation Output Transition calculation 首先,cel ...

随机推荐

- 从客户端中检测到有潜在危险的request.QueryString

1. 修改 web.config文件 1.1 <pages validateRequest="false"></pages> (如果存在这个节点 直接加属性 ...

- Ubuntu 安装交叉编译器出错问题

安装教程网上有很多,可参考:Ubuntu14.04(64位)下gcc-linaro-arm-linux-gnueabihf交叉编译环境搭建 但是我的问题一直是路径搭好了,就是找不到文件:反复查找,花了 ...

- java注册界面及mysql连接

题目要求 完成注册界面及添加功能 1登录账号:要求由6到12位字母.数字.下划线组成,只有字母可以开头:(1分) 2登录密码:要求显示“• ”或“*”表示输入位数,密码要求八位以上字母.数字组成.(1 ...

- 边捆绑: Content Importance Based Edge Bundling for Graph Visualization

Problem 当图所要表达的信息较多时, 图中可能会充满交叉的线[1-2], 甚至整个显示空间都被点.线所覆盖, 这时想通过观察来获取图中的重要信息将会变得非常困难, 这种现象称为图的视觉混乱. K ...

- laravel Type error: Argument 2 passed to Illuminate\Routing\UrlGenerator::__construct() must be an instance of Illuminate\Http\Request

第一种情况: 传递给 UrlGenerator 的第二个参数是 Request 实例 你传进去的是null, 可以检查 config文件夹下的配置文件是否有用到 url() 函数的,如果有,将 url ...

- python 百万级别类实例实现节省内存

# 案例: ''' 某网络游戏中,定义了玩家类Player(id,name,status) 每当有一个玩家,就会在服务器创建一个Player实例 当在线人数过多时,将产生大量实例(百万级别),消耗内存 ...

- jsp中 EL表达式 ${}

原文位置:https://zhidao.baidu.com/question/711232806155434565.html jsp标签中的 ${表达式}用来输出或者计算一个表达式的内容,比如${3+ ...

- VMware上Linux虚拟机和Windows共享文件夹

参考文章:https://blog.csdn.net/qq_19004627/article/details/78689641 操作环境:主机:Windows10,VMware Workstation ...

- laravel实现excel表的导入导出功能

1.这是个我去公司之后曾经折磨我很久很久的功能查阅了很多资料但是功夫不负有心人在本人的不懈努力下还是实现了这个功能 (ps看不懂我下面说讲述的可以参考这个laravel学院的官方文档 https:// ...

- wap网站开发小记(转载)

一:网页的一些标记 1:声明 <!DOCTYPE html PUBLIC "-//WAPFORUM//DTD XHTML Mobile 1.0//EN" "http ...