AArch32/AArch64系统级内存模型(三)

1. 内存系统架构

1.1 系统级存储系统体系结构的形式

Armv8的a -profile体系结构包括一个虚拟内存系统体系结构(Virtual Memory System Architecture - VMSA),参见----。

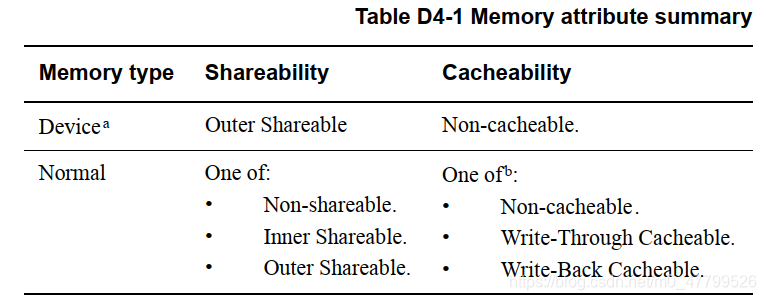

1.2 系统级可见 内存属性

| 类型 | 说明 |

|---|---|

| Normal | 这通常用于大容量内存操作,包括读/写和只读操作。系统中大部分内存都是这种类型 |

| Device | 对该种类型的内存进行读写可能具有连带效应(side-effects,指对一个内存位置的读写操作会影响其它内存位置)或者从该种内存中的一个位置装载的值可能随着装载的次数而变化。通常内存映射外设(指使用访问内存的方法来访问的外设)会采用这种内存类型 |

|

(1) 上表中Shareability是与一致性有关的内存属性, 用来指示一个内存位置对于一些处理器是否是可共享的。共享意味着需要硬件保证一个内存位置中的内容对一定范围内可访问该位置的多个处理器是一致。参见:Cache的相关知识(一) - 9. 共享域

(2) cacheability是指cache的回写策略。参见:Cache的相关知识(一) - 8.2 cache的回写策略

2. 对混合字节序的支持

如果在AArch32异常级别上实现了混合字节序支持,则字节序由PSTATE.E控制。 对于异常返回AArch32状态,将从SPSR_ELx.E复制PSTATE.E。 如果目标异常级别仅支持小端访问,则SPSR_ELx.E为RES0。 如果目标异常级别仅支持大端访问,则SPSR_ELx.E为RES1。

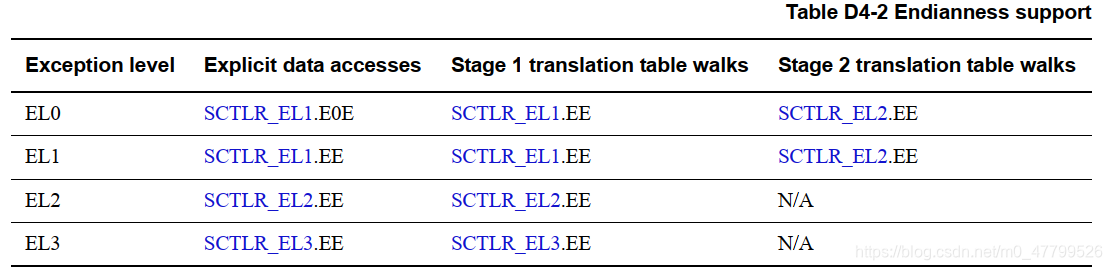

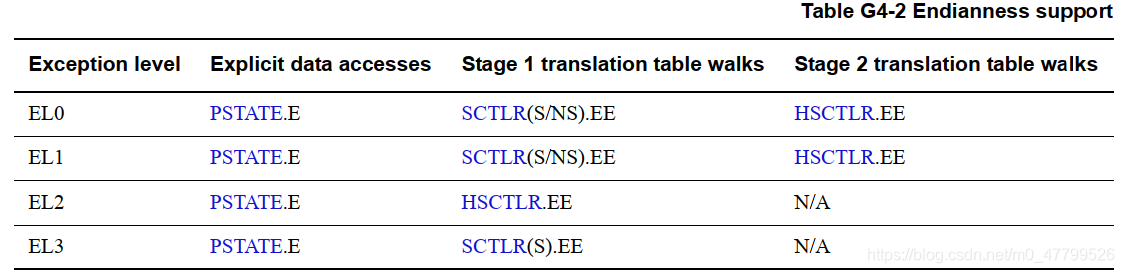

1. AArch64 显式数据访问和转换表遍历的endianness

2. AArch32 显式数据访问和转换表遍历的endianness

注意:

(1) 如果使用AArch32为异常级别实现了混合字节序支持,则字节序由PSTATE.E控制。 当异常从AArch64状态返回到AArch32状态,将从SPSR_ELx.E复制PSTATE.E。

(2) 如果目标异常级别仅支持小端访问,则SPSR_ELx.E为RES0。 如果目标异常级别仅支持大端访问,则SPSR_ELx.E为RES1。 PSTATE.E在AArch64状态下被忽略。

3. 对缓存的支持

3.1 缓存标识

Armv8缓存标识由一组寄存器组成,这些寄存器描述了缓存操作指令将如何影响在PE上的应用的缓存。包括

| 类型 | AArch64 | AArch32 |

|---|---|---|

| 影响整个缓存 | 例如:IC IALLU(Instruction Cache Invalidate All to PoU) | 例如:ICIALLUIS(Instruction Cache Invalidate All to PoU, Inner Shareable) |

| VA操作 | 例如: IC IVAU (Instruction Cache line Invalidate by VA to PoU) | 例如:ICIALLUIS (Instruction Cache line Invalidate by VA to PoU) |

| way(路)/set(组)操作 | 例如: DC ISW (Data or unified Cache line Invalidate by Set/Way) | 例如:ICIALLUIS (Data Cache line Invalidate by Set/Way) |

缓存标识寄存器有:

| 寄存器类型 | AArch64寄存器名称 | AArch32寄存器名称 | 说明 |

|---|---|---|---|

| Cache Type Register) | CTR_EL0 | CTR | 该寄存器定义了 (1) 受指令缓存操作指令影响的任何指令缓存的最小行长度; (2) 受数据缓存操作指令的影响的任何数据或统一性缓存的最小行长度; (3) 一级指令缓存的缓存索引和标记策略。 |

| Cache Level ID Register | CLIDR_EL1 | CLIDR | 该寄存器定义了 (1) 缓存类型; (2) Level of Unification Inner Shareable (LoUIS), Level of Coherence (LoC) and the Level of Unification (LoU) ; (3) 一个可选的ICB字段,用于指示内部缓存可缓存内存区域与外部缓存可缓存区域之间的边界 |

| Cache Size Selection Register | CSSELR_EL1 | CSSELR | 该寄存器定义了 (1) 选择当前缓存的缓存级别(Level 1 ~ Level 7); |

| Cache Size Identification Register | CCSIDR_EL1 | 当应用FEAT_CCIDX时: CCSIDR/ CCSIDR2 当未应用FEAT_CCIDX时: CCSIDR |

该寄存器主要提供有关当前选定缓存的体系结构的信息,比如NumSets, Associativity, and LineSize; |

3.2 Cacheability, cache allocation hints, and cache transient hints

可缓存性 仅适用于normall类型的内存,并为内部和外部缓存位置单独定义。所有device类型的设备内存总是被视为不可缓存的。内存属性Cacheability表示一个内存位置是否可以被分配到缓存中。

内存属性包括一个可缓存属性,参见:8.2 cache的回写策略

3.3 启用和禁用内存访问的缓存

在Armv8中,可缓存性控制字段可以强制所有具有Normal内存类型的内存位置被视为不可缓存,而不管它们的可缓存性属性是什么。每一阶段的地址转换都有独立的控制:

- 数据访问。这些控件也适用于对 translation tables 的访问。

- 指令访问。

3.3.1在AArch64状态下,可缓存性控制字段及其效果如下

| translation regime | Non-secure/secure | 寄存器 | 说明 |

|---|---|---|---|

| EL1&0 | - | SCTLR_EL1.C == 0 | (1) 访问的内存数据在所有stage1转换都是 Non-cacheable (2) 对stage1转换表的访问是 Non-cacheable |

| EL1&0 | - | SCTLR_EL1.I == 0 | (1) 访问内存时的指令在所有stage1转换都是 Non-cacheable |

| EL1&0 | - | HCR_EL2.CD == 1 | (1) 访问的内存数据在stage2转换都是 Non-cacheable (2) 对stage2转换表的访问是 Non-cacheable |

| EL1&0 | - | HCR_EL2.ID == 1 | (1) 访问内存时的指令在所有stage2转换都是 Non-cacheable |

| EL1&0 | - | HCR_EL2.DC == 1 | (1) 所有 stage1转换和对stage1转换表的所有访问都被视为对 Non-shareable Inner Write-Back Cacheable Read-Allocate Write-Allocate, Outer Write-Back Cacheable Read-Allocate Write-Allocate memory的内存进行访问,无论 SCTLR_EL1.{I, C}的值如何,这适用于数据和指令访问的转换 |

| EL1&0 | - | SCTLR_EL1.M == 0 | 禁用了stage1 的translations ,并且HCR_EL2.DC的值为0 (1) 如果 SCTLR_EL1.I的值为0,从stage1访问内存的指令是 Outer Shareable, Inner Non-cacheable, Outer Non-cacheable; (2) 如果 SCTLR_EL1.I的值为1,从stage1访问内存的指令是 Outer Shareable, Inner Write-Through cacheable, Outer Write-Through cacheable; |

| EL2 | - | SCTLR_EL2.C == 0 | (1) 访问的内存数据都是 Non-cacheable (2) 对转换表的访问是 Non-cacheable |

| EL2 | - | SCTLR_EL2.I == 0 | (1) 访问内存时的指令都是 Non-cacheable |

| EL2&0 | - | SCTLR_EL2.C == 0 | (1) 访问的内存数据都是 Non-cacheable (2) 对转换表的访问是 Non-cacheable |

| EL2&0 | - | SCTLR_EL2.I == 0 | (1) 访问内存时的指令都是 Non-cacheable |

| EL3 | - | SCTLR_EL3.C == 0 | (1) 访问的内存数据都是 Non-cacheable (2) 对EL2转换表的访问是 Non-cacheable |

| EL3 | - | SCTLR_EL3.I == 0 | (1) 访问内存时的指令都是 Non-cacheable |

| !(EL1&0) | - | SCTLR_ELx.M == 0 | 禁用了stage1 的translations ,并且HCR_EL2.DC的值为0 (1) 如果 SCTLR_ELx.I的值为0,从stage1访问内存的指令是 Outer Shareable, Inner Non-cacheable, Outer Non-cacheable; (2) 如果 SCTLR_ELx.I的值为1,从stage1访问内存的指令是 Outer Shareable, Inner Write-Through cacheable, Outer Write-Through cacheable; |

3.3.2在AArch32状态下,可缓存性控制字段及其效果如下

| translation regime | Non-secure/secure | 寄存器 | 说明 |

|---|---|---|---|

| PL1&0 | Non-secure | SCTLR.C == 0 | (1) 访问的内存数据在stage1转换都是 Non-cacheable (2) 对stage1转换表的访问是 Non-cacheable |

| PL1&0 | Non-secure | SCTLR.I == 0 | (1) 访问内存时的指令在所有stage1转换都是 Non-cacheable |

| PL1&0 | Non-secure | HCR2.CD == 1 | (1) 访问的内存数据在stage2转换都是 Non-cacheable (2) 对stage2转换表的访问是 Non-cacheable |

| PL1&0 | Non-secure | HCR2.ID == 1 | (1) 访问内存时的指令在stage2转换都是 Non-cacheable |

| PL1&0 | Non-secure | HCR.DC == 1 | (1) 所有stage1阶段转换和对 EL1&0 stage1转换表的所有访问都被视为对Non-shareable Inner Write-Back Cacheable Read-Allocate Write-Allocate, Outer Write-Back Cacheable Read-Allocate Write-Allocate的内存进行访问,无论SCTLR.C的值如何,这适用于数据和指令访问的转换 |

| PL1&0 | Non-secure | SCTLR.M == 0 | 禁用了stage1 的translations ,则如果EL2使用AArch32并且HCR.DC的值为0,或者如果EL2使用AArch64并且HCR_EL2.DC的值为0,则: (1) 如果SCTLR.I的值为0,从stage1访问内存的指令是 Outer Shareable, Inner Non-cacheable, Outer Non-cacheable; (2) 如果SCTLR.I的值为1,从stage1访问内存的指令是 Outer Shareable, Inner Write-Through cacheable, Outer Write-Through cacheable; |

| PL1&0 | secure | SCTLR.C == 0 | (1) 访问的内存数据在stage1转换都是 Non-cacheable (2) 对stage1转换表的访问是 Non-cacheable |

| PL1&0 | secure | SCTLR.I == 0 | (1) 访问内存时的指令都是 Non-cacheable |

| PL1&0 | secure | SCTLR.M == 0 | 禁用了stage1 的translations ,则如果EL2使用AArch32并且HCR.DC的值为0,或者如果EL2使用AArch64并且HCR_EL2.DC的值为0,则: (1) 如果SCTLR.I的值为0,从stage1访问内存的指令是 Outer Shareable, Inner Non-cacheable, Outer Non-cacheable; (2) 如果SCTLR.I的值为1,从stage1访问内存的指令是 Outer Shareable, Inner Write-Through cacheable, Outer Write-Through cacheable; |

| EL2 | - | HSCTLR.C == 0 | (1) 对内存的数据访问都是 Non-cacheable (2) 对EL2转换表的访问是 Non-cacheable |

| EL2 | - | HSCTLR.I == 0 | (1) 访问内存时的指令都是 Non-cacheable |

| EL2 | - | HSCTLR.M == 0 | 禁用了stage1 的translations ,则如果EL2使用AArch32并且HCR.DC的值为0,或者如果EL2使用AArch64并且HCR_EL2.DC的值为0,则: (1) 如果 HSCTLR.I 的值为0,从stage1访问内存的指令是 Outer Shareable, Inner Non-cacheable, Outer Non-cacheable; (2) 如果 HSCTLR.I 的值为1,从stage1访问内存的指令是 Outer Shareable, Inner Write-Through cacheable, Outer Write-Through cacheable; |

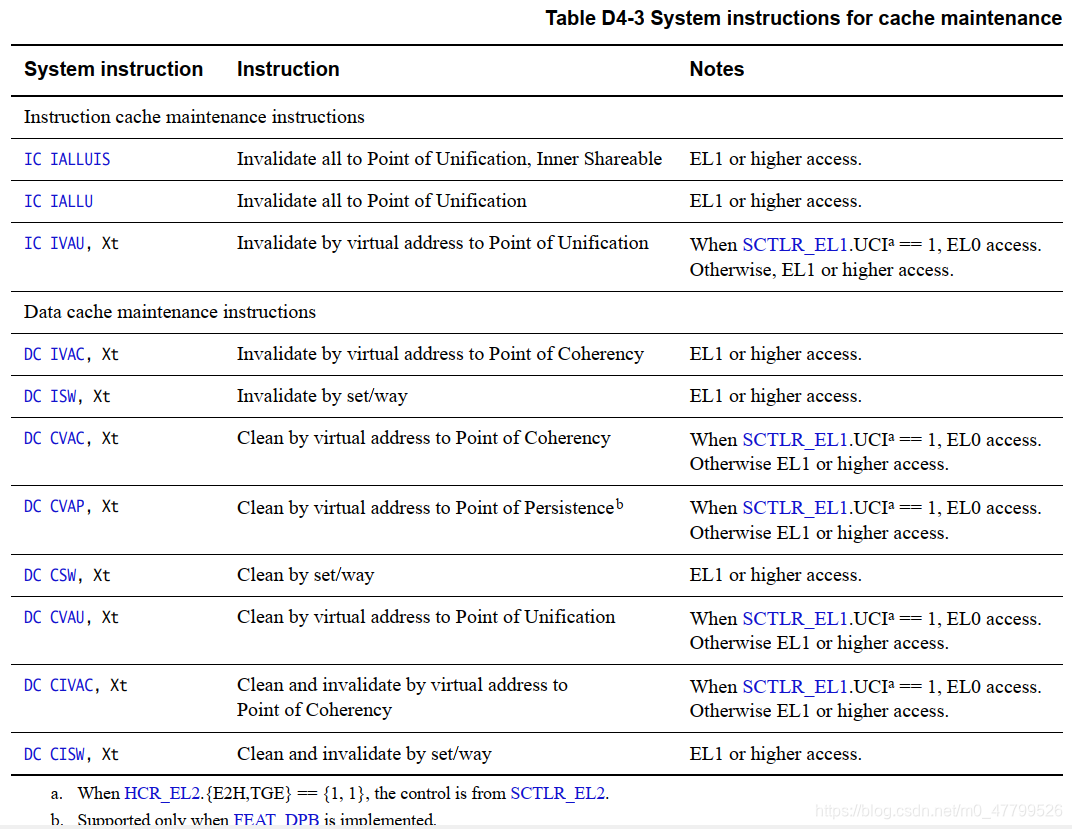

3.4 cache maintenance

1. Cache maintenance 指令对特定的内存位置起作用,指令作用的范围如下:

- 某个虚拟地址,称为VA操作。

- 特定的高速缓存行或者组和路,称为 set/way操作。

2. 按set/way操作Cache maintenance 指令的术语

| 术语 | 解释 |

|---|---|

| Level | 层次结构中的缓存级别,在Arm架构中,越低的缓存级别越靠近PE,armv8目前支持(Level 1 ~ Level 7) |

| set(组) | 缓存的每一层都被分割成若干组。每一组是缓存层中的一组位置,可以为其分配一个地址。 在Arm架构中,组从0开始编号 |

| way(路) | 将cache平均分成多层,每一层称为一路。 在Arm架构中,路从0开始编号 |

3. Cache的管理的操作指令术语

| 术语 | 解释 |

|---|---|

| Clean | 整个高速缓存或者某个高速缓存行。相应的高速缓存行会被标记为脏,数据会写回到下一级高速缓存中或者主存储器中。 |

| Invalidate | 整个高速缓存或者某个高速缓存行。高速缓存上的数据会被丢弃 |

| Clean and Invalidate | 与执行clean指令后紧接着执行invalidate指令的行为相同。这两条指令在同一个位置执行 |

| 清零(Zero)操作 | 在某些情况下,对高速缓存进行清零操作起到一个预取和加速的功效,比如当程序需要使用一大块临时内存,在初始化阶段对这个内存进行清零操作,这时高速缓存控制器会主动把这些零数据写入高速缓存行中。若程序主动使用高速缓存的清零操作,那么将大大减少系统内部总线的带宽。 |

4. PoU和PoC

参见:Cache的相关知识(一) -10. PoU和PoC的区别

5. A64/A32 Cache maintenance instructions

(1) A64 Cache maintenance instructions

(2) AArch32 cache and branch predictor maintenance instructions

参考:

(1) 《Arm Architecture Reference Manual Armv8, for Armv8-A architecture profile - The AArch64 System Level Memory Model D4.4 Cache support》。

AArch32/AArch64系统级内存模型(三)的更多相关文章

- ARMV8 datasheet学习笔记4:AArch64系统级体系结构之编程模型(1)-EL/ET/ST

1.前言 ARMV8系统级编程模型主要包括异常级别.运行状态.安全状态.同步异常.异步异常.DEBUG 本文主要对系统级编程模型做一个概要介绍 2. 异常级别 2.1 Exception level概 ...

- ARMV8 datasheet学习笔记4:AArch64系统级体系结构之编程模型(4)- 其它

1. 前言 2.可配置的指令使能/禁用控制和trap控制 指令使能/禁用 当指令被禁用,则这条指令就会变成未定义 指令Trap控制 控制某条或某些指令在运行时进入陷阱,进入陷阱的指令会产生trap异常 ...

- ARMV8 datasheet学习笔记4:AArch64系统级体系结构之存储模型

1.前言 关于存储系统体系架构,可以概述如下: 存储系统体系结构的形式 VMSA 存储属性 2. 存储系统体系结构 2.1. 地址空间 指令地址空间溢出 指令地址计算((address_of ...

- JVM内存模型 三

本文章节: 1.JMM简介 2.堆和栈 3.本机内存 4.防止内存泄漏 1.JMM简介 i.内存模型概述 Java平台自动集成了线程以及多处理器技术,这种集成程度比Java以前诞生的计算机语言要厉 ...

- ARMV8 datasheet学习笔记4:AArch64系统级体系结构之Generic timer

1.前言 2.generate timer 2.1 概述 提供了一个系统计数器,用来实时测量流逝的时间: 提供了一个虚拟计数器,用来测量某个虚拟机上流逝的虚拟时间: 定时器,每隔一段时间会触发事件,支 ...

- ARMV8 datasheet学习笔记4:AArch64系统级体系结构之编程模型(3)- 异常

1.前言 本文介绍异常相关内容,包括异常类型,异常进入,异常返回,异常层次结构,异常的路由等 2. RESET ARMV8体系结构支持两种类型的RESET Cold reset:Reset PE所有 ...

- ARMV8 datasheet学习笔记4:AArch64系统级体系结构之编程模型(2)- 寄存器

1. 前言 2. 指令运行与异常处理寄存器 ARM体系结构的寄存器分为两类: (1)系统控制和状态报告寄存器 (2)指令处理寄存器,如累加.异常处理 本部分将主要介绍如上第(2)部分的寄存器,分为AA ...

- ARMV8 datasheet学习笔记4:AArch64系统级体系结构之VMSA

1. 前言 2. VMSA概述 2.1 ARMv8 VMSA naming VMSAv8 整个转换机中,地址转换有一个或两个stage VMSAv8-32 由运行AArch32的异常级别来管理 VMS ...

- Java虚拟机之JVM系统和内存模型

1.类加载子系统 负责从文件系统或者网络中加载Class信息,加载的信息存放在一块称之为方法区的内存空间里. 2.方法区 存放类信息.常量信息.常量池信息.包括字符串字面量和数字常量等,方法区的大小决 ...

- ARMV8 datasheet学习笔记4:AArch64系统级体系结构之Self-hosted debug

1. 前言 2. 关于self-hosted debug Debugger调试器 是操作系统或系统软件的一部分,它会处理debug exception或修改debug system register, ...

随机推荐

- Docker_构建_运行总结

样例: 构建镜像 build-image-fim-backend.sh echo "开始构建 fim-backend 镜像..." cp -rp ../target/fim-bac ...

- win10算hash值,md5,sha256等,无需额外下载工具

# windows_cmd certutil -hashfile .\文件名 SHA256 可选哈希算法:md2/md4/md5/sha1/sha256/sha384/sha512

- Java套接字实现应用程序对数据库的访问

最近在完成软件体系结构上机实验时,遇到一个有点点小难度的选做题,题目信息如下: 利用套接字技术实现应用程序中对数据库的访问.应用程序只是利用套接字连接向服务器发送一个查询的条件,而服务器负责对数据库的 ...

- Python实验报告——第2章 Python语言基础

实验报告 [实验目的] 1.熟悉在线编程平台. 2.掌握基本的 python 程序编写.编译与运行程序的方法. [实验条件] 1.PC机或者远程编程环境 [实验内容] 1.完成第二章实例01-07,实 ...

- 第2篇----Istio架构概述篇

Istio的工作机制 Istio的工作机制和架构,分为控制面和数据面两部分.控制面主要包括Pilot.Mixer.Citadel等服务组件:数据面由伴随每个应用程序部署的代理程序Envoy组成,执行针 ...

- Java基础之变量

Java基础之变量 目录 Java基础之变量 1.变量概述 1.1 为什么需要变量 1.2 简单理解 1.3 变量使用注意事项 1.4 程序中+号的使用 1.5 Java数据类型 1.6 整数类型 1 ...

- frp服务利用云主机实现Windows远程连接

frp服务利用云主机实现Windows远程连接 1.下载所需要的安装包 https://github.com/fatedier/frp/releases 下载 frp_0.44.0_linux_amd ...

- 媒介查询兼容各种端口的响应式范围取值(移动端、PC端、ipad、移动端侧屏)

!!!(chrome作者亲测)!!!数据仅供参考 /*ipad*/@media screen and (min-width:760px) and (max-width:1000px) /*移动端*/@ ...

- display:block 和display:inline-block的区别和用法

1).块状元素:(div,p,form,ul,ol,li) ,独占一行,默认情况width为100% 2).行内块状元素:(span,img,a),不会独占一行,相邻的元素一直排在同一行,排满了才会换 ...

- docker搭建个人云盘可道云kodbox

1.拉取kodbox镜像 (文章最后有自己编写yml文件可直接搭建) docker pull tznb/kodbox:1.15 2. 创建并启动kodbox docker run -d -it --n ...