FPGA设计千兆以太网MAC(2)——以太网协议及设计规划

上篇该系列博文中通过MDIO接口实现了PHY芯片的状态检测,验证其已处于1000M 全双工工作模式。在设计MAC逻辑之前,要先清楚MAC与PHY之间的接口以及以太网协议细节,这样才能保证网络的兼容性。本文内容多来自Xilinx官方文档pg051 tri-mode-eth-mac.

1.GMII接口

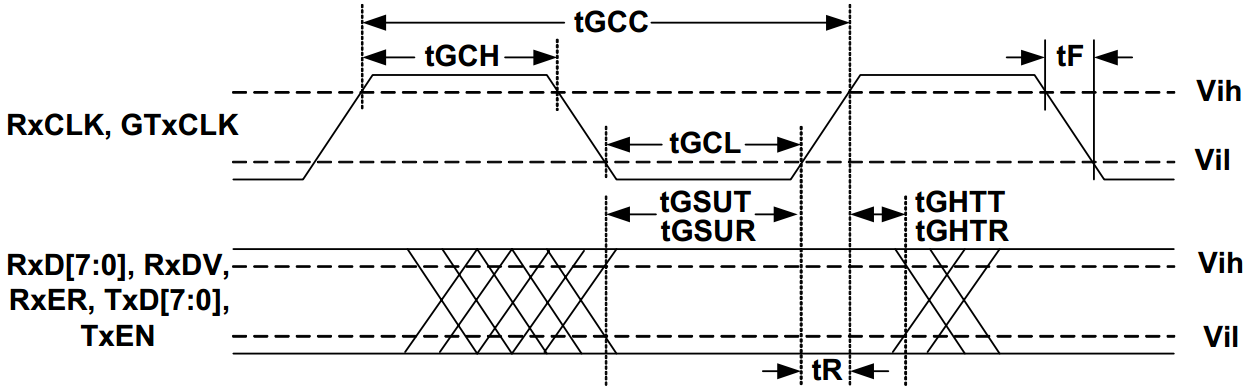

此处使用较简单的GMII接口,接口列表及说明如下:

TX方向时钟tx_mac_aclk由FPGA给出,RX方向时钟gmii_rx_clk由PHY芯片经过内部CDR模块从接收数据中恢复出来,时钟频率均为125MHz。TX和RX方向基本均由三个信号组成:d en/dv er。查看开发板上使用的以太网PHY芯片RTL8211EG-VB datasheet中AC Characteristics:

数据在时钟上升沿采样,因此TX端可在时钟下降沿更新数据,RX端时钟上升沿接收数据即可。

2.以太网协议规范

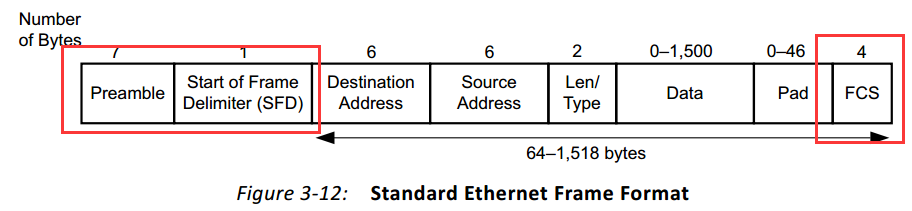

MAC层的功能就是“成帧解帧”,接下来查看以太网数据帧结构和规则。

前导码、帧头符以及FCS在TX方向被MAC添加,在RX方向被剔除。接收端MAC逻辑会将SFD作为接收帧起始时刻。

关于长度/类型字段之前有所提及,Ethernet II帧长度/类型域解释为上层协议类型(字段值大于等于1536,即十六进制的0x0600),而IEEE802.3同样位置是长度字段(字段值小于等于1500,即十六进制的0x05DC)。若为EthernetII帧,接收端MAC不做处理。若为IEEE802.3帧,MAC则检测帧长度是否与该字段匹配,并在必要时去除pad域。

Pad域用来确保前导码和SFD之后的部分长度在64byte以上,也就是保证pad+data≥46byte。当data≥46byte时,不需要pad域。

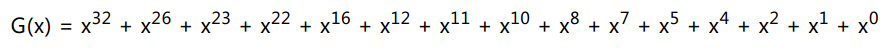

FCS采用CRC32,多项式为:

接收端MAC会检测每个帧的FCS值,如果接收FCS错误,则MAC指示给上层用户接收到一个错误帧。

IEEE 802.3-2008规定,以太网帧间隔为96-bit时间以上。对于千兆网来说,t = Tbit*96 = (1/1000*1000*1000)*96s = 96ns。

3.流量控制高级话题

当收发两端的时钟频率出现细微偏差,持续一段时间后会导致频率较慢的一方缓存溢出。此时较慢一方需要告诉另一方暂停一段时间发送数据包以减轻自身缓存压力。“告诉”这一动作通过发送指定控制帧完成。

其中mac control parameters代表对方暂停的时间单位个数,在千兆网中若该数据为1则表示对方需暂停发送数据包512ns。当一方缓存即将溢出,则发送暂停帧。若此时正在发送数据帧,则等待当前帧发送完成。接收方收到pause帧后,依次检测目的地址及类型域,若目的地址为多播地址(01-80-c2-00-00-01)且符合pause帧操作码,则提取控制参数数值并通过拉低发送侧rdy信号来暂停发送。

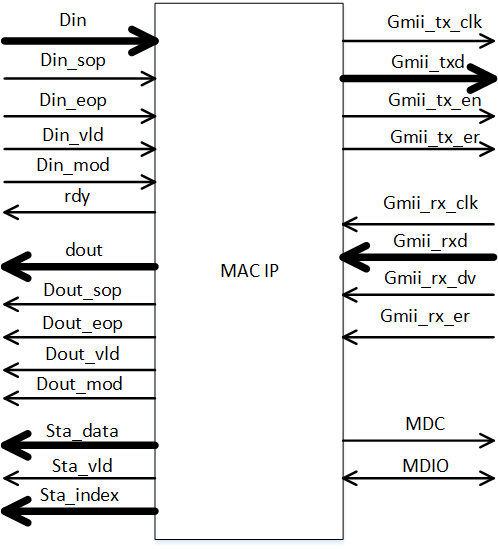

4.系统设计

先定义MAC接口:用户侧包括发送数据通道,接收数据通道以及事件统计通道。PHY芯片侧同样有发送通道 接收通道和MDIO管理通道。用户侧数据位宽32bit,PHY芯片侧位宽8bit。

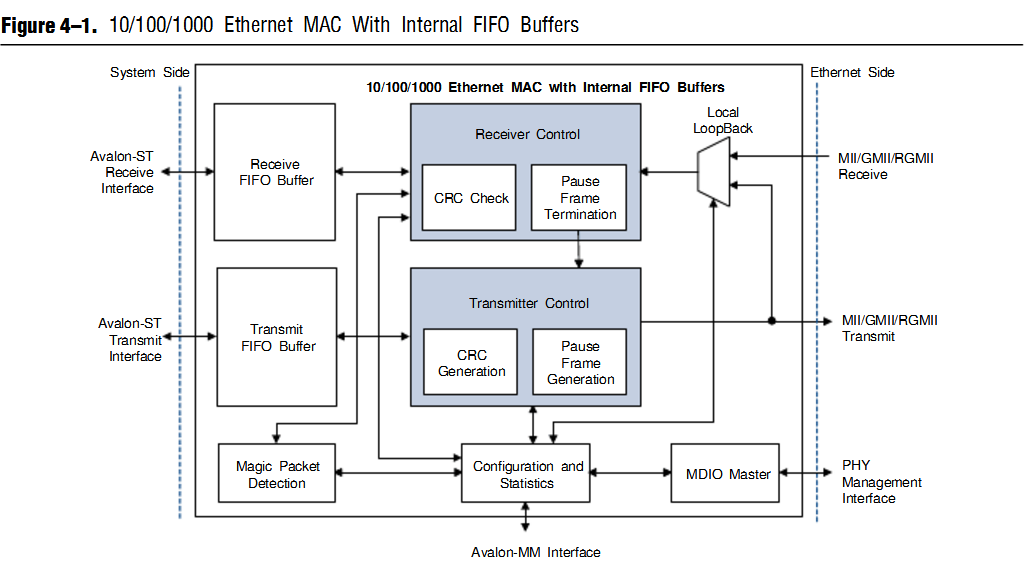

MAC内部设计结构可以参照Altera的以太网MAC IP核,可见内部主要由发送和接收处理逻辑、缓存部分、配置与统计以及MDIO控制模块五部分组成。

模块划分和接口定义完成后,开始写RTL代码。后续以发送方向为例,完成代码设计、行为仿真、时序约束及STA、板级调试。

FPGA设计千兆以太网MAC(2)——以太网协议及设计规划的更多相关文章

- 【重新发布,代码开源】FPGA设计千兆以太网MAC(1)——通过MDIO接口配置与检测PHY芯片

原创博客,转载请注明出处:[重新发布,代码开源]FPGA设计千兆以太网MAC(1)——通过MDIO接口配置与检测PHY芯片 - 没落骑士 - 博客园 https://www.cnblogs.com/m ...

- FPGA设计千兆以太网MAC(3)——数据缓存及位宽转换模块设计与验证

本文设计思想采用明德扬至简设计法.上一篇博文中定制了自定义MAC IP的结构,在用户侧需要位宽转换及数据缓存.本文以TX方向为例,设计并验证发送缓存模块.这里定义该模块可缓存4个最大长度数据包,用户根 ...

- 【转】简谈基于FPGA的千兆以太网

原文地址: http://blog.chinaaet.com/luhui/p/5100052903 大家好,又到了学习时间了,学习使人快乐.今天我们来简单的聊一聊以太网,以太网在FPGA学习中属于比较 ...

- 【小梅哥FPGA进阶学习之旅】基于Altera FPGA 的DDR2+千兆以太网电路设计

DDR2电路设计 在高速大数据的应用中,高速大容量缓存是必不可少的硬件.当前在FPGA系统中使用较为广泛的高速大容量存储器有经典速度较低的单数据速率的SDRAM存储器,以及速度较高的双速率DDR.DD ...

- 千兆以太网TCP协议的FPGA实现

转自https://blog.csdn.net/zhipao6108/article/details/82386355 千兆以太网TCP协议的FPGA实现 Lzx 2017/4/20 写在前面,这应该 ...

- 【转】基于TMS320C6455的千兆以太网设计

基于TI公司最新DSP芯片TMS320C6455.设计并实现了以太网通信软硬件接口.采用TMS320C6455片内以太网接口模块EMAC/MDIO,结合片外AR8031 PHY芯片,在嵌入式操作系统D ...

- AC6102 开发板千兆以太网UDP传输实验2

AC6102 开发板千兆以太网UDP传输实验 在芯航线AC6102开发板上,设计了一路GMII接口的千兆以太网电路,通过该以太网电路,用户可以将FPGA采集或运算得到的数据传递给其他设备如PC或服务器 ...

- AC6102 开发板千兆以太网UDP传输实验

AC6102 开发板千兆以太网UDP传输实验 在芯航线AC6102开发板上,设计了一路GMII接口的千兆以太网电路,通过该以太网电路,用户可以将FPGA采集或运算得到的数据传递给其他设备如PC或服务器 ...

- 关于千兆以太网芯片及VLAN浅析

MARVEL出产的高端千兆以太网交换芯片,对每个端口支持不同的交换模式. 包括4种模式: Secure模式:所带VLAN tag必须存在于VTU表中,且入端口必须是该VLAN成员,否则丢弃报文. Ch ...

随机推荐

- easyui表格自动换行

表格内容自动换行可以通过设计表格属性 nowrap:false来实现,默认值为true: 但是easyui并未提供,表头自动换行的解决方案,因为一般我们的数据表格列名都是固定的,想换行的话可以通过& ...

- ERP小金刚Pro专业大比拼: Dynamics,NetSuite和Odoo

前言 在过去的15年中,新技术推动了大大小企业的重新思考他们的流程管理涉及不断变化的业务所创造的新动态景观.实施ERP是许多企业为帮助组织而采取的措施并优化他们开展业务的方式.然而,市场上目前有许多商 ...

- iOS 好文源码收藏

bireme 大佬的 iOS 保持界面流畅的技巧 https://blog.ibireme.com/2015/11/12/smooth_user_interfaces_for_ios/ 深入理解Run ...

- July 07th. 2018, Week 27th. Saturday

Soon is not as good as now. 别谈未来,现在就行动. From Seth Godin. I always told myself that I should finish w ...

- July 05th. 2018, Week 27th. Thursday

Pleasure in the job puts perfection in the work. 乐于工作才能有完美表现. From Aristole. Do you want promotion? ...

- CF592D Super M

嘟嘟嘟 首先这题虽然不是很难,但是黄题是不是有点过分了--好歹算个蓝题啊. 手玩样例得知,这哥们儿瞬移到的城市\(A\)一定是这些被攻击的城市构成的树的一个叶子,然后他经过的最后一个城市\(B\)和\ ...

- 还在用NuGet吗?大哥FuGet了解一下

前言 你可能不知道是,NuGet已经发布10年了,从 Visual Studio 2010 第一次官方集成NuGet以来,这10年间有聚集了超过 14万 的包,这些包有超过 150万 的版本提供,大约 ...

- v-cloak的用法和注意事项

v-cloak是前端框架vue.js中的一个方法,作用是为了防止在页面加载时先出现变量名闪烁的情况,造成不好的用户体验, 例如:{{ v.name}} (闪一下)=> 张三 用法:html中:& ...

- MySQL学习(一)日志与索引 --- 2019年1月

1.MySQL的架构 1).连接器 先根据Ip和端口号,用户名和密码,连接MySQL数据库,连接后如果没有下一步动作,连接就处于空闲状态,此时有一个连接超时时间的设置 wait_timeout默认8小 ...

- Linux~学习笔记目录索引

回到占占推荐博客索引 本篇文章是对自己学习Linux及在它的环境下部署工具的一个总结,以方便自己查阅,也给他人一个帮助,本文章同时会不断的更新,欢迎大家订阅! 本目录包括的内容会包括linux基础命令 ...