为什么现在使用多周期CPU,而单周期CPU被弃用?

最初设计的CPU结构简单,内部不复杂。之所以制造它是为了让机器自动跑程序,算数。

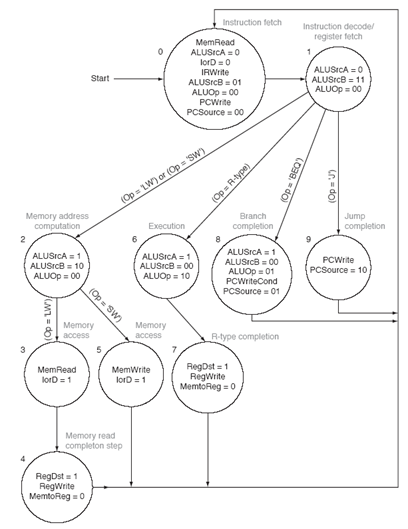

早期CPU都是单周期的,人们没考虑那么多,性能啥的。就让CPU每个时钟周期跑一个指令,这些时钟周期等长。这样下来,有的指令跑完耗时长,有的指令跑完耗时短, 而CPU是走完一条指令再处理下一条的,给每个指令的时钟周期都是相同的,那么木桶原理,时钟周期肯定就是耗时最长的指令所需的时间。后来人们意识到了计算机的巨大威力,便开始专心制造更强的电子计算机。这时,为了提升CPU的速度,优化CPU的结构,有人设计了一套多周期CPU结构。对指令集的所有指令作分析,可以发现它们处理过程有相同的地方,那这下好了,我把所有的指令切成几段基本操作(换句话说,所有的指令都可以看成是几个基本操作的序列组成),例如:指令1可以看成{opA——>opC——>opV},指令2可以看成{opA——>opK——>opV——>opT}。然后让时钟周期适配op,而不是单条指令。每个指令需要多个周期(周期值较小)。这里的多周期CPU依然是逐条执行每个指令。下图为一个多周期CPU的控制器状态自动机。

举例对比上面所述单周期CPU和多周期CPU的耗时:

CPU的指令集Ins中有多条指令,指令4耗时最长,执行一次它需要800ps。

单周期CPU的时钟周期最少设为800ps。此时假如我们要执行指令1,2,3,4,5,6,那么总共耗时6x800ps=4800ps。

多周期CPU,分别可以把指令123456分解为3个op,2个op,4个op,8个op,3个op,5个op。每个op延时为100ps。那么假如我们要执行指令1,2,3,4,5,6,则总共耗时为(3+2+4+8+3+5)x100ps=2500ps。

这样一对比多周期CPU相较于单周期CPU的优势是不是很明显啦。

在这之后,有人发现了上面所说的多周期CPU还可以改进优化提速,他把流水线的思想拿到了CPU设计上,允许指令并行执行,这样一来速度又得到了提升。现在的CPU基本都是使用流水线技术设计的CPU。

为什么现在使用多周期CPU,而单周期CPU被弃用?的更多相关文章

- verilog实现的16位CPU单周期设计

verilog实现的16位CPU单周期设计 这个工程完成了16位CPU的单周期设计,模块化设计,包含对于关键指令的仿真与设计,有包含必要的分析说明. 单周期CPU结构图 单周期CPU设计真值表与结构图 ...

- 单周期CPU设计的理论基础

写在前面:本博客内容为本人老师原创,严禁任何形式的转载!本博客只允许放在博客园(.cnblogs.com),如果您在其他网站看到这篇博文,请通过下面这个唯一的合法链接转到原文! 本博客全网唯一合法UR ...

- 单周期CPU设计

终于有点时间了,恰好多周期的设计也已经完成,其实只想写写多周期的,无奈单周期补上才好,哈哈哈~ —————+—————黄金分割线—————+————— 首先要理解什么叫单周期CPU(与后面多周期CPU ...

- 单周期cpu设计代码解读

目录 写在前面 单周期cpu设计代码讲解 概念回顾 Verilog代码讲解 写在前面 欢迎转载,转载请说明出处. 单周期cpu设计代码讲解 概念回顾 一.电子计算机的部件 分为:中央处理器(cpu). ...

- P4-verilog实现mips单周期CPU

最近对学习的掌控可能出现了问题,左支右绌,p2挂了,p2.p3.p4.p5每周在计组花的连续时间少了很多,学习到的东西也少了很多,流水线都还没真正开始写,和别人比落后了一大截,随笔自然就荒废了,我得尽 ...

- 单周期CPU

一个时钟周期执行一条指令的过程理解(单周期CPU): https://blog.csdn.net/a201577F0546/article/details/84726912 单周期CPU指的是一条指令 ...

- 使用logisim搭建单周期CPU与添加指令

使用logisim搭建单周期CPU与添加指令 搭建 总设计 借用高老板的图,我们只需要分别做出PC.NPC.IM.RF.EXT.ALU.DM.Controller模块即可,再按图连线,最后进行控制信号 ...

- 使用Verilog搭建一个单周期CPU

使用Verilog搭建一个单周期CPU 搭建篇 总体结构 其实跟使用logisim搭建CPU基本一致,甚至更简单,因为完全可以照着logisim的电路图来写,各个模块和模块间的连接在logisim中非 ...

- Verilog单周期CPU(未完待续)

单周期CPU:指令周期=CPU周期 Top模块作为数据通路 运算器中有ALU,通路寄存器(R1.R2.R3.R4),数据缓冲寄存器(鉴于书上的运算器只有R0)........... 此为ALU和通用寄 ...

随机推荐

- 使用ASP.NET Core 3.x 构建 RESTful API - 2. 什么是RESTful API

1. 使用ASP.NET Core 3.x 构建 RESTful API - 1.准备工作 什么是REST REST一词最早是在2000年,由Roy Fielding在他的博士论文<Archit ...

- P2114 [NOI2014]起床困难综合症

#include<iostream> #include<cstdio> using namespace std; ; ]; long long n,m; long long t ...

- Java实现不遍历数组求和

package com.jts.t1; /** * 不遍历数组求和 * 方法省略异常检查 */ public class Demo1 { public static void main(String[ ...

- Rxjava2源码解析

1:用法: Observable<Integer> observable = Observable.create(new ObservableOnSubscribe<Integer& ...

- spark基于yarn的两种提交模式

一.spark的三种提交模式 1.第一种,Spark内核架构,即standalone模式,基于Spark自己的Master-Worker集群. 2.第二种,基于YARN的yarn-cluster模式. ...

- 用安全密钥验证ssh

1.需要打开两台虚拟机,并保证两台虚拟机可以ping通: 本地主机IP:192.168.8.120 远程主机IP:192.168.8.100 2.在本地主机生成密钥对,输入命令“ssh-keygen” ...

- ubuntu 16.04安装并启动openssh

对于没有图形界面的linux系统,一般都会用到远程连接控制,,因此新安装的linux系统,在配好网络后,首先要安装的就是远程连接工具,ssh是常用的方法. ps -ef |grep ssh //查看 ...

- Ubuntu 16.04源码编译boost库 编写CMakeLists.txt | compile boost 1.66.0 from source on ubuntu 16.04

本文首发于个人博客https://kezunlin.me/post/d5d4a460/,欢迎阅读! compile boost 1.66.0 from source on ubuntu 16.04 G ...

- Oracle数据库 获取CLOB字段存储的xml格式字符串指定节点的值

参照: Oracle存储过程中使用游标来批量解析CLOB字段里面的xml字符串 背景:在写存储过程时,需要获取表单提交的信息.表单信息是以xml格式的字符串存储在colb类型的字段dataxml中,如 ...

- myBaits持久性框架

动态 SQL 博客交流群:1018996617 动态 SQL MyBatis 的强大特性之一便是它的动态 SQL.如果你有使用 JDBC 或其他类似框架的经验,你就能体会到根据不同条件拼接 SQL ...