解锁4K,Xilinx MPSoC ARM + FPGA高清视频采集与显示方案!

当下,随着数字化多媒体技术以令人惊叹的速度不断演进,高清视频处理成为众多领域关注的焦点。今天为大家分享4K HDMI 高清视频方案,基于Xilinx UltraScale+ MPSoC XCZU7EV高性能平台。

方案介绍

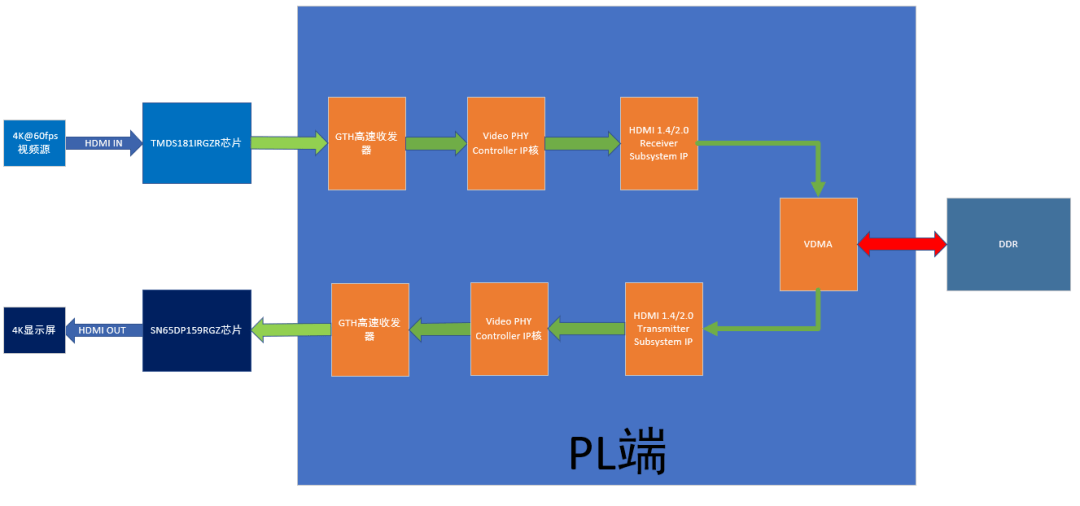

4K@60fps视频源经过HDMI IN接口传输至TMDS181IRGZR芯片进行信号转换,转换后的高速串行信号通过GTH高速收发器输入至PL端,利用Xilinx官方的IP核执行信号的解串操作(串转并),并解码出视频流数据,随后通过VDMA IP缓存至DDR中,利用Xilinx官方的IP对视频流数据进行重新编码,并通过IP核执行串化操作(并转串)。最终,经过GTH高速收发器和SN65DP159RGZ芯片的转换后,视频信号通过HDMI OUT接口被输出至4K显示屏。

方案优势

(一)多通道支持

处理器集成了20个GTH高速串行收发器,支持最高达5路的4K HDMI 视频输入,极大地满足了多屏幕、高分辨率视频处理的复杂应用需求,为用户构建多视频源处理系统提供了坚实基础。

(二)低延时特性

只需通过逻辑资源实现,避免了额外的硬件延迟,确保了视频流的实时传输和处理,真正实现了视频数据的实时同步交互,适用于实时性要求较高的应用场景。

(三)高集成度设计

本方案具备高集成度,简化了电路设计,将众多视频处理功能模块高度整合。不仅降低了系统复杂性,还有效控制了成本,为用户在系统构建和成本控制方面提供了双重优势。

SOM-TLZU核心板优势

SOM-TLZU核心板典型应用领域

4K HDMI 高清视频开发案例

为了简化描述,本文仅摘录部分方案功能描述与测试结果。

开发环境

本文主要介绍基于Xilinx UltraScale+ MPSoC XCZU7EV的4K HDMI 高清视频开发案例,适用开发环境如下。

Windows开发环境:Windows 7 64bit、Windows 10 64bit

Linux开发环境:Ubuntu18.04.4 64bit

开发工具包:Xilinx Unified 2022.2

硬件平台:创龙科技TLZU-EVM评估板

案例说明

通过HDMI IN接口采集4K@60fps视频采集,并通过HDMI OUT接口将采集到的视频进行输出。

案例演示

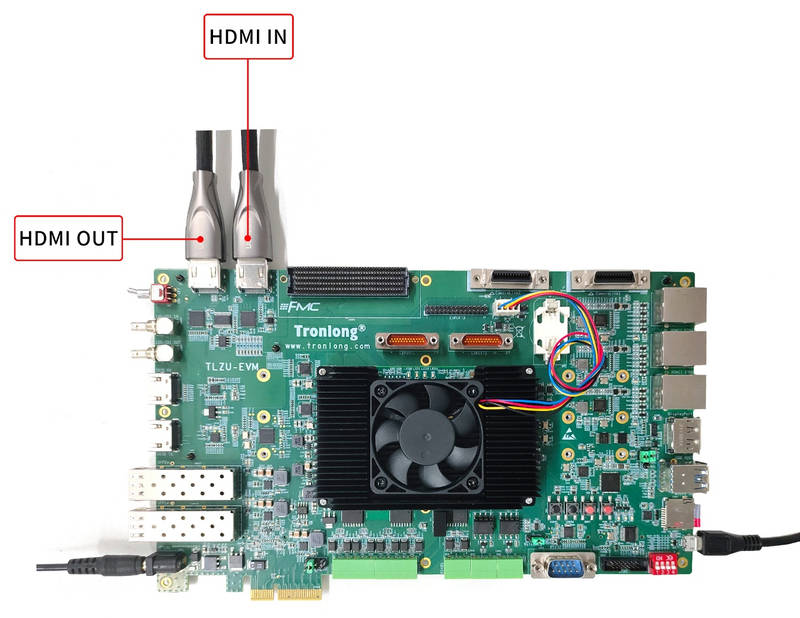

首先,将小米盒子作为视频源设备、4K显示屏作为输出显示设备连接至评估板,具体硬件连接方式如下所示:

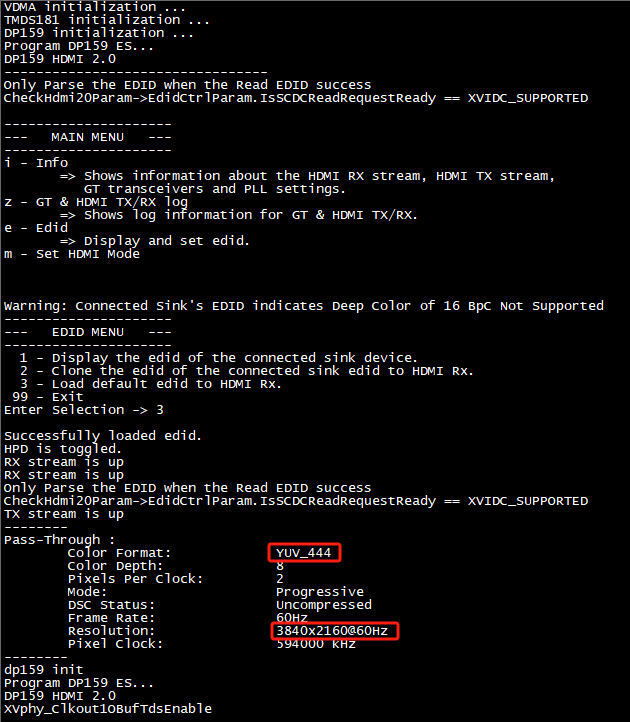

硬件连接后,加载PS端裸机程序、PL端程序。完成后即可看到调试串口终端打印如下信息。

参考产品资料操作,重启4K显示屏后,调试串口终端打印如下信息。YUV_444:表示输出图像格式;3840x2160@60Hz:表示输出图像分辨率与帧率。

此时,我们可以看到4K显示屏上显示出正常的图像,画面清晰、色彩鲜艳、无卡顿现象,完美呈现出4K高清视频的魅力。

若您希望深入了解更多XCZU7EV相关的精彩案例演示,可以通过公众号(Tronlong创龙科技)获取详细资料,快来一起试试吧!

解锁4K,Xilinx MPSoC ARM + FPGA高清视频采集与显示方案!的更多相关文章

- Xilinx zynq-7000系列FPGA移植Linux操作系统详细教程

Xilinx zynq-7000系列FPGA移植Linux操作系统详细教程 一:前言 最近手上压了一块米联客的Miz7035,一块xilinx zynq-7000系列的开发板,想着正好学习一下linu ...

- PCIE_DMA实例五:基于XILINX XDMA的PCIE高速采集卡

PCIE_DMA实例五:基于XILINX XDMA的PCIE高速采集卡 一:前言 这一年关于PCIE高速采集卡的业务量激增,究其原因,发现百度"xilinx pcie dma",出 ...

- 【新产品发布】【iCore2 ARM / FPGA 双核心板】

iCore2是一款包含ARM / FPGA两大利器的双核心板.ARM方面,采用意法半导体高性能的32位Cortex-M3内核STM32F103VE微处理器,主频达72MHz,并包含丰富外设接口.FPG ...

- Xilinx 7 series FPGA multiboot技术的使用

Xilinx 7 series FPGA multiboot技术的使用 当升级程序有错误的时候,系统会启动golden bitstream 注意:需要在源工程与升级工程中添加如下约束语句 生成组合mc ...

- Xilinx 7系列FPGA部分重配置【2】

在之前的“Xilinx 7系列FPGA部分重配置[1]”中已经较为详细地记录了分别在工程模式(Project Mode)和非工程模式(Non-Project Mode)下.使用7系列的Xilinx F ...

- 发现Xilinx Virtex 5 FPGA中单个DSP乘法器只支持17位无符号乘法

发现Xilinx Virtex 5 FPGA中,单个DSP乘法器只支持17位无符号乘法.如果令18位乘数相乘,结果会与正确的乘积不同.

- 基于PCIe的多路视频采集与显示子系统

基于PCIe的多路视频采集与显示子系统 1 概述 视频采集与显示子系统可以实时采集多路视频信号,并存储到视频采集队列中,借助高效的硬实时视频帧出入队列管理和PCIe C2H DMA引擎, ...

- 基于Camera Link和PCIe DMA的多通道视频采集和显示系统

基于Camera Link和PCIe DMA的多通道视频采集和显示系统 在主机端PCIe驱动的控制和调度下,视频采集与显示系统可以同时完成对多个Camera Link接口视频采集以及Camera Li ...

- dsp下基于双循环缓冲队列的视频采集和显示记录

对最近在设计的视频采集和显示缓冲机制做一个记录,以便以后使用. 视频采集和显示缓冲机制,其实是参考了Linux下v4L2的驱动机制,其采用输入多缓冲frame,输出多缓冲的切换机制.简单的就是ping ...

- QT5.4.1在ARM开发板上不能显示汉字

在linux下正常的程序,移植到ARM上,中文不能显示.网上好多介绍,一头雾水.查看其中话题是关于中文显示的(http://www.qtcn.org/bbs/simple/?t55852.html). ...

随机推荐

- 墨天轮访谈 | 叶金荣:GreatSQL开源社区——做中国广受欢迎的开源数据库

分享嘉宾:叶金荣 万里数据库开源生态负责人 整理:墨天轮社区 导读 大家好,我是来自万里数据库的叶金荣,GreatSQL开源社区的愿景是做中国广受欢迎的开源数据库,这也是我今天分享的主题. Great ...

- ORM底层逻辑

1 数据库必然是只认识Sql语句 2 ORM的底层必然是ADO.NET 3 ORM也可以说是ADO的一种封装 ORM: 1 通过实体生成Sql语句-大量的反射 2 对应映射关系

- C#查漏补缺----Exception处理实现,无脑抛异常不可取

前言 环境:.NET 8.0 系统:Windows11 参考资料:CLR via C#, .Net Core底层入门 https://andreabergia.com/blog/2023/05/err ...

- Plain-Det:同时支持多数据集训练的新目标检测 | ECCV'24

近期在大规模基础模型上的进展引发了对训练高效大型视觉模型的广泛关注.一个普遍的共识是必须聚合大量高质量的带注释数据.然而,鉴于计算机视觉中密集任务(如目标检测和分割)标注的固有挑战,实际的策略是结合并 ...

- 《使用Gin框架构建分布式应用》阅读笔记:p108-p126

<用Gin框架构建分布式应用>学习第8天,p108-p126总结,总计18页. 一.技术总结 1.Redis eviction policy (1)什么是 eviction policy? ...

- .NET使用OllamaSharp实现大模型推理对话的简单演示

前提条件:请确保你本地已经安装了ollama以及有关本地离线模型.或者已有远程模型环境等.如果没有,请自行部署.如果需要帮助,可以文末获取联系方式咨询.由于部署离线大模型过于简单,在线资料也很多, ...

- 【VMware VCF】使用 Offline Bundle Transfer Utility(OBTU)配置 VCF 脱机库。

VMware Cloud Foundation 环境中,软件包仓库的来源支持两种方式,分别是 Online Depot 和 Offline Depot.第一种方式,是在 VCF 环境能够连接互联网的情 ...

- nextjs 实战开发1 Mercury 二级域名分发系统| 曲速引擎 Warp Drive

开发目标 开发一个免费的二级域名分发系统 创建项目 root@ubuntu:~/dev-nextjs/mercury_frontend# pnpm create next-app@latest .版本 ...

- FPGA时序约束基础

一.时序约束的目的 由于实际信号在FPGA内部期间传输时,由于触发器等逻辑期间并非理想期间,因此不可避免地存在传输延时,这种延迟在高速工作频率.高逻辑级数时会造成后级触发器地建立时间和保持时间不满足, ...

- Docker制作私有镜像仓库

构建私有仓库 启动Docker Registry,使用Docker官方提供的Registry镜像就可以搭建本地私有镜像仓库,具体指令如下. docker run -d -p 5000:5000 --r ...