backend flow

在PD之后,netlist中会多出很多DCAP元件(去耦电容,减少IR-Drop)或者filter cell(保证芯片均匀度要求)

还有一些antenna cell也就是一些diode用来泻流,防止天线效应(生产中裸露的metal,收集电荷,击穿栅极)

版图一般由两层组成:base layer和metal layer。

base layer由p-substrate和n-well组成。

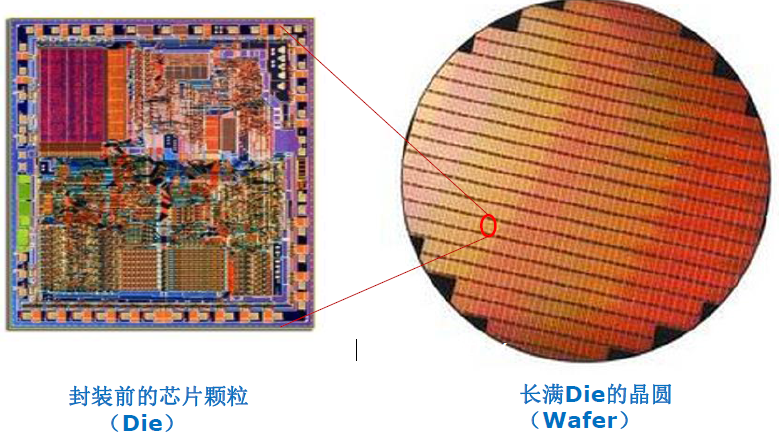

封装前的芯片叫做die,长满die的晶圆叫做wafer

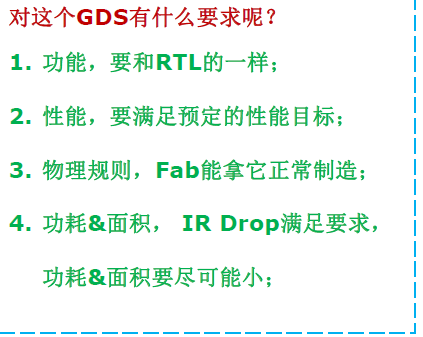

GDS相对于RTL的要求:

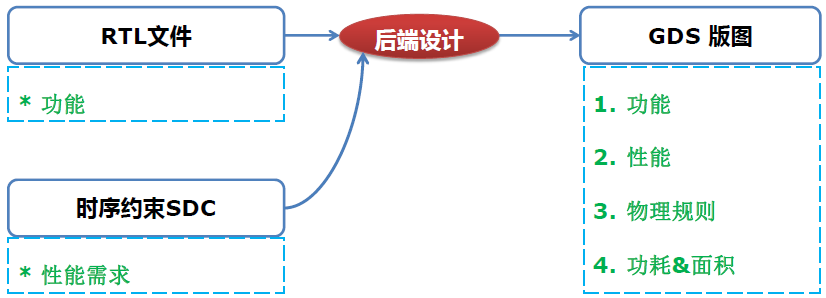

RTL+SDC经过synthsis和physical design得到GDS

synthesis = transition + optimization + mapping

其中transition将RTL转变为GTECH格式,

后在sdc的约束下进行optimizaiton和mapping到target lib,主要约束包括(timing,power,area)

在logic synthesis过程中,主要进行setup time的约束,hold time在CTS之后加buffer来修复。

常用的工具有synopsys的design compiler(DC)和cadence的RTL Compiler(RC)。

在进行ECO的过程中,需要对RTL和netlist进行formal check

其中netlist包括pre_netlist(经过transiiton),dft_netlist(插入dft),pg_netlist(插入power switch)

常用的工具有:synopsys的formality(fm)和cadence的conformal(lec)

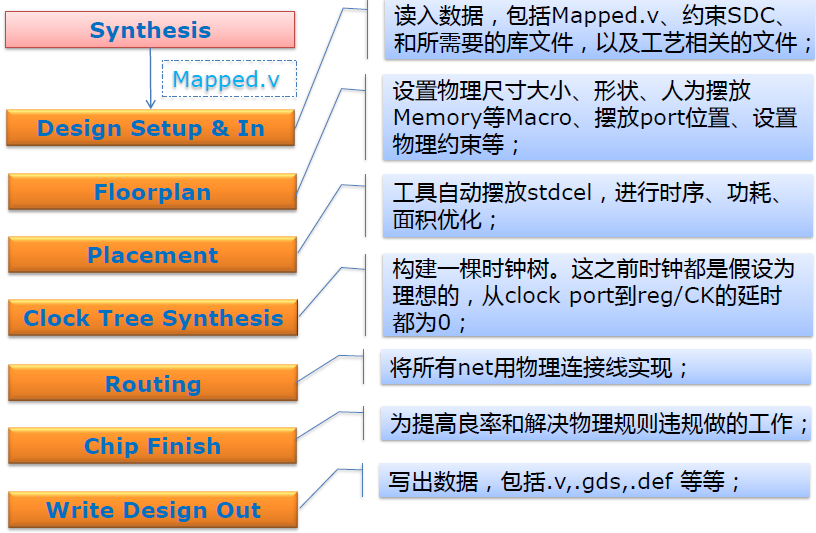

从Netlist到GDS的物理实现:

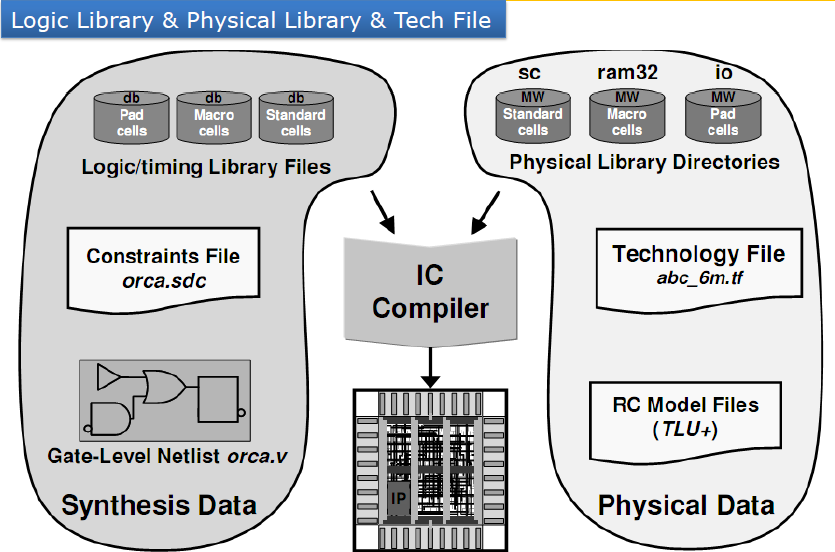

物理实现需要的三种文件:

logic library(以db格式存储),physical library(以milkyway格式保存),tech file

Signoff STA,最终的时序,要求使用最精确的RC寄生参数和STA算法。

RC参数可以用synopsys的StarRC工具提取,cadence的QRC工具提取。

STA工具可以用synopsys的PrimeTime,cadence的ETS工具

physical verification

DRC:Design Rule Check,(Antenna Rule File)

LVS:Layout vs Schematic;

Power Signoff:IR Drop

Static IR drop

Dynamic IR drop

常用的工具有:cadence的EPS和synopsys的PrimeRail

数字后端流程

1. 数据准备。

对于 CDN 的 Silicon Ensemble而言后端设计所需的数据主要有是Foundry厂提供的标准单元、宏单元和I/O Pad的库文件,它包括物理库、时序库及网表库,分别以.lef、.tlf和.v的形式给出。前端的芯片设计经过综合后生成的门级网表,具有时序约束和时钟定义的脚本文件和由此产生的.gcf约束文件以及定义电源Pad的DEF(Design Exchange Format)文件。(对synopsys 的Astro 而言,经过综合后生成的门级网表,时序约束文件 SDC 是一样的,Pad的定义文件--tdf , .tf 文件 --technology file, Foundry厂提供的标准单元、宏单元和I/O Pad的库文件就与FRAM, CELL view, LM view 形式给出(Milkway 参考库 and DB, LIB file)

2. 布局规划。

主要是标准单元、I/O Pad和宏单元的布局。I/O Pad预先给出了位置,而宏单元则根据时序要求进行摆放,标准单元则是给出了一定的区域由工具自动摆放。布局规划后,芯片的大小,Core的面积,Row的形式、电源及地线的Ring和Strip都确定下来了。如果必要在自动放置标准单元和宏单元之后,你可以先做一次PNA(power network analysis)--IR drop and EM .

3. Placement -自动放置标准单元。

布局规划后,宏单元、I/O Pad的位置和放置标准单元的区域都已确定,这些信息SE(Silicon Ensemble)会通过DEF文件传递给PC(Physical Compiler),PC根据由综合给出的.DB文件获得网表和时序约束信息进行自动放置标准单元,同时进行时序检查和单元放置优化。如果你用的是PC +Astro那你可用write_milkway, read_milkway 传递数据。

4.时钟树生成(CTS Clock tree synthesis) 。

芯片中的时钟网络要驱动电路中所有的时序单元,所以时钟源端门单元带载很多,其负载延时很大并且不平衡,需要插入缓冲器减小负载和平衡延时。时钟网络及其上的缓冲器构成了时钟树。一般要反复几次才可以做出一个比较理想的时钟树。---Clock skew.

5. STA 静态时序分析和后仿真。

时钟树插入后,每个单元的位置都确定下来了,工具可以提出Global Route形式的连线寄生参数,此时对延时参数的提取就比较准确了。SE把.V和.SDF文件传递给PrimeTime做静态时序分析。确认没有时序违规后,将这来两个文件传递给前端人员做后仿真。对Astro 而言,在detail routing 之后,

用starRC XT 参数提取,生成的E.V和.SDF文件传递给PrimeTime做静态时序分析,那将会更准确。

6. ECO(Engineering Change Order)。

针对静态时序分析和后仿真中出现的问题,对电路和单元布局进行小范围的改动.

7. Filler的插入(pad fliier, cell filler)。

Filler指的是标准单元库和I/O Pad库中定义的与逻辑无关的填充物,用来填充标准单元和标准单元之间,I/O Pad和I/O Pad之间的间隙,它主要是把扩散层连接起来,满足DRC规则和设计需要。

8. 布线(Routing)。

Global route-- Track assign --Detail routing--Routing optimization 布线是指在满足工艺规则和布线层数限制、线宽、线间距限制和各线网可靠绝缘的电性能约束的条件下,根据电路的连接关系将各单元和I/O Pad用互连线连接起来,这些是在时序驱动(Timing driven ) 的条件下进行的,保证关键时序路径上的连线长度能够最小。--Timing report clear

9. Dummy Metal的增加。

Foundry厂都有对金属密度的规定,使其金属密度不要低于一定的值,以防在芯片制造过程中的刻蚀阶段对连线的金属层过度刻蚀从而降低电路的性能。加入Dummy Metal是为了增加金属的密度。

10. DRC和LVS。

DRC是对芯片版图中的各层物理图形进行设计规则检查(spacing ,width),它也包括天线效应的检查,以确保芯片正常流片。LVS主要是将版图和电路网表进行比较,来保证流片出来的版图电路和实际需要的电路一致。DRC和LVS的检查--EDA工具 Synopsy hercules/ mentor calibre/ CDN Dracula进行的.Astro also include LVS/DRC check commands.

11. Tape out。

在所有检查和验证都正确无误的情况下把最后的版图GDSⅡ文件传递给Foundry厂进行掩膜制造。

backend flow的更多相关文章

- Flask基础全套

Flask简介 Flask是主流PythonWeb三大框架之一,其特点是短小精悍以及功能强大从而获得众多Pythoner的追捧,相比于Django它更加简单更易上手,Flask拥有非常强大的三方库,提 ...

- 排查 docker flow proxy 的 503 问题

这是今天我们在开发环境下 docker swarm 集群上遇到的问题,在这篇博文中记录一下排查过程. 先登录到应用容器内检查一下其中运行的站点是否能正常访问: # docker exec -it 02 ...

- Git 在团队中的最佳实践--如何正确使用Git Flow

我们已经从SVN 切换到Git很多年了,现在几乎所有的项目都在使用Github管理, 本篇文章讲一下为什么使用Git, 以及如何在团队中正确使用. Git的优点 Git的优点很多,但是这里只列出我认为 ...

- [LeetCode] Pacific Atlantic Water Flow 太平洋大西洋水流

Given an m x n matrix of non-negative integers representing the height of each unit cell in a contin ...

- BZOJ 4390: [Usaco2015 dec]Max Flow

4390: [Usaco2015 dec]Max Flow Time Limit: 10 Sec Memory Limit: 128 MBSubmit: 177 Solved: 113[Submi ...

- ArcGIS制作放射状流向地图(Radial Flow Map)

流向地图火了,因为Facebook的那张著名的友邻图,抑或因为<数据可视化之美>中介绍飞行模式的航线图,总之,流向地图以它特殊的可视化形式,直观地展示事物之间的联系,尤其在展示网络流向.贸 ...

- SSIS Data Flow优化

一,数据流设计优化 数据流有两个特性:流和在内存缓冲区中处理数据,根据数据流的这两个特性,对数据流进行优化. 1,流,同时对数据进行提取,转换和加载操作 流,就是在source提取数据时,转换组件处理 ...

- Data Flow的Error Output

一,在Data Flow Task中,对于Error Row的处理通过Error Output Tab配置的. 1,操作失败的类型:Error(Conversion) 和 Truncation. 2, ...

- SSIS Data Flow 的 Execution Tree 和 Data Pipeline

一,Execution Tree 执行树是数据流组件(转换和适配器)基于同步关系所建立的逻辑分组,每一个分组都是一个执行树的开始和结束,也可以将执行树理解为一个缓冲区的开始和结束,即缓冲区的整个生命周 ...

随机推荐

- UITableView & UITableViewController

内容概要: 本文先讲解了UITableView概述,然后主要从应用方面讲解了UITableViewController(包括add.delete.move单元cell的操作,以及UITableView ...

- Selenium2学习-034-WebUI自动化实战实例-032-获取页面 body 大小

获取 body 元素大小的方法,非常简单,直接上码,敬请参阅! /** * Get body size * * @author Aaron.ffp * @version V1.0.0: autoSel ...

- JS-006-表格元素操作

直接上菜咯... 以下为 HTML 表格源码: <html> <head> <meta http-equiv="Content-Type" conte ...

- 包含Blob字段的表无法Export/Import

最近一直用MySQL-Front的导出导出工具完成数据库的备份,确实比较方便快捷. 后来增加了一张表,其中有blob字段,上传几个文件后,发现导出不好用了,进度条长期处于停滞状态. 想想也是,要把bl ...

- NSNumber,NSValue和NSData

我们在编码中,很多时候需要将C里面原生的数据封装成对象,这样可以用NSDictionary或者NSArray来存取访问.尤其是一些做适配的情况下,这种封装是不可避免的.Objective-C提供了不少 ...

- 配置本地yum源

配置本地yum源 一. 远程挂载ISO文件 mount /dev/sr0 /mnt/cdrom (本地挂载mount -t iso9660 -o loop xx.iso /media) 二. 配置 ...

- 微信域名weixin.com天价成交!是腾讯吗?

据业内人士爆料,“微信”双拼域名weixin.com已于今天交易了,成交价格8位数.如此大手笔,神秘买家会是腾讯吗? 通过查询该域名的whois信息,最近一次的更新时间显示为今年4月13日,注册邮箱信 ...

- MySQL管理之道:性能调优、高可用与监控内置脚本

MySQL管理之道:性能调优.高可用与监控内置脚本 随书附送脚本 keepalive配置文件和脚本开源工具pssh批量管理服务器(python) 下载地址 http://files.cnblogs.c ...

- 建字段_添加数据_生成json.php

<?php header("Content-Type:text/html;charset=utf8"); class db{ static $localhost = &quo ...

- nginx源码分析—内存池结构ngx_pool_t及内存管理

Content 0. 序 1. 内存池结构 1.1 ngx_pool_t结构 1.2 其他相关结构 1.3 ngx_pool_t的逻辑结构 2. 内存池操作 2.1 创建内存池 2.2 销毁内存池 2 ...