Vivado ILA观察信号和调试过程

先简单介绍一下ILA(Integrated Logic Analyzer)生成方法。这里有两种办法完成Debug Core的配置和实现。

方法一、mark_debug综合选项+Set Up Debug设定ILA参数。

1、在信号(reg或者wire)声明处加mark_debug选项,方法如下:

// spi_mosi信号标记为需要ILA观测的信号

(* MARK_DEBUG = “TRUE” *) wire spi_mosi;

mark_debug用法的详细说明请看Xilinx文档UG901_Synthesis

2、综合,进行Run Synthesis

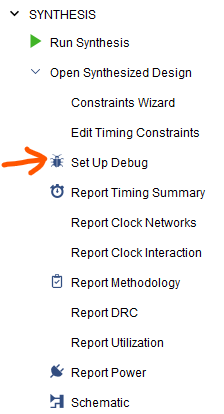

3、Open Synthesized Design,打开Set Up Debug,如图:

4、为ILA Debug Core添加需要观测的信号,结果如图:

每一个信号都要指定一个采样时钟域(Clock Domain)。

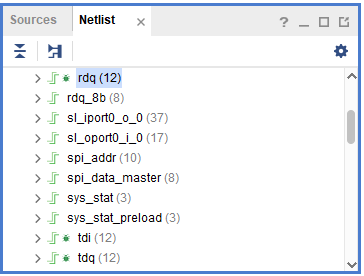

关于添加方法,还可以在Netlist窗口拖动信号到这个列表内。

注意到Netlist中有些信号名称前面有了绿色的小蜘蛛(小星星) ,正是Verilog程序中进行mark_debug的信号:

5、在Set Up Debug中设定信号采样收集的深度(Sample of data depth),输入流水级别数(Input pipe stages),Capture control和Advanced trigger选项。

6、完成ILA配置,保存Debug Setup,Run Implementation

说明:

完成了Debug Setup以后重新进行Implementation,XDC文件中被附加上了配置debug Core的XDC语句,例如:

# 下面这句创建一个新的调试核,名称u_ila_0

create_debug_core u_ila_0 ila

set_property ALL_PROBE_SAME_MU true [get_debug_cores u_ila_0]

set_property ALL_PROBE_SAME_MU_CNT 4 [get_debug_cores u_ila_0]

set_property C_ADV_TRIGGER true [get_debug_cores u_ila_0]

set_property C_DATA_DEPTH 8192 [get_debug_cores u_ila_0]

set_property C_EN_STRG_QUAL true [get_debug_cores u_ila_0]

set_property C_INPUT_PIPE_STAGES 3 [get_debug_cores u_ila_0]

set_property C_TRIGIN_EN false [get_debug_cores u_ila_0]

set_property C_TRIGOUT_EN false [get_debug_cores u_ila_0]

# 下面这句为u_ila_0调试核设定端口clk的宽度为1

set_property port_width 1 [get_debug_ports u_ila_0/clk]

# 下面这句为u_ila_0调试核设定采样时钟信号(clk)为sys_sam_clk

connect_debug_port u_ila_0/clk [get_nets [list sys_pll_01/inst/sys_sam_clk]]

set_property PROBE_TYPE DATA_AND_TRIGGER [get_debug_ports u_ila_0/probe0]

set_property port_width 21 [get_debug_ports u_ila_0/probe0]

# 下面这句为u_ila_0调试核连接待观测信号corr_i_quant

connect_debug_port u_ila_0/probe0 [get_nets [list {corr_i_quant[0]} {corr_i_quant[1]} {corr_i_quant[2]} {corr_i_quant[3]} {corr_i_quant[4]} {corr_i_quant[5]} {corr_i_quant[6]} {corr_i_quant[7]} {corr_i_quant[8]} {corr_i_quant[9]} {corr_i_quant[10]} {corr_i_quant[11]} {corr_i_quant[12]} {corr_i_quant[13]} {corr_i_quant[14]} {corr_i_quant[15]} {corr_i_quant[16]} {corr_i_quant[17]} {corr_i_quant[18]} {corr_i_quant[19]} {corr_i_quant[20]}]]

create_debug_port u_ila_0 probe

set_property PROBE_TYPE DATA_AND_TRIGGER [get_debug_ports u_ila_0/probe1]

set_property port_width 12 [get_debug_ports u_ila_0/probe1]

connect_debug_port u_ila_0/probe1 [get_nets [list {rdq[0]} {rdq[1]} {rdq[2]} {rdq[3]} {rdq[4]} {rdq[5]} {rdq[6]} {rdq[7]} {rdq[8]} {rdq[9]} {rdq[10]} {rdq[11]}]]

create_debug_port u_ila_0 probe

set_property PROBE_TYPE DATA_AND_TRIGGER [get_debug_ports u_ila_0/probe2]

set_property port_width 12 [get_debug_ports u_ila_0/probe2]

connect_debug_port u_ila_0/probe2 [get_nets [list {rdi[0]} {rdi[1]} {rdi[2]} {rdi[3]} {rdi[4]} {rdi[5]} {rdi[6]} {rdi[7]} {rdi[8]} {rdi[9]} {rdi[10]} {rdi[11]}]]

create_debug_port u_ila_0 probe

set_property PROBE_TYPE DATA_AND_TRIGGER [get_debug_ports u_ila_0/probe3]

set_property port_width 12 [get_debug_ports u_ila_0/probe3]

connect_debug_port u_ila_0/probe3 [get_nets [list {tdi[0]} {tdi[1]} {tdi[2]} {tdi[3]} {tdi[4]} {tdi[5]} {tdi[6]} {tdi[7]} {tdi[8]} {tdi[9]} {tdi[10]} {tdi[11]}]]

create_debug_port u_ila_0 probe

set_property PROBE_TYPE DATA_AND_TRIGGER [get_debug_ports u_ila_0/probe4]

set_property port_width 12 [get_debug_ports u_ila_0/probe4]

connect_debug_port u_ila_0/probe4 [get_nets [list {tdq[0]} {tdq[1]} {tdq[2]} {tdq[3]} {tdq[4]} {tdq[5]} {tdq[6]} {tdq[7]} {tdq[8]} {tdq[9]} {tdq[10]} {tdq[11]}]]

create_debug_port u_ila_0 probe

set_property PROBE_TYPE DATA_AND_TRIGGER [get_debug_ports u_ila_0/probe5]

set_property port_width 1 [get_debug_ports u_ila_0/probe5]

connect_debug_port u_ila_0/probe5 [get_nets [list bb_sam_clk_5]]

create_debug_port u_ila_0 probe

set_property PROBE_TYPE DATA_AND_TRIGGER [get_debug_ports u_ila_0/probe6]

set_property port_width 1 [get_debug_ports u_ila_0/probe6]

connect_debug_port u_ila_0/probe6 [get_nets [list AD_SPI_MOSI_OBUF]]

create_debug_port u_ila_0 probe

set_property PROBE_TYPE DATA_AND_TRIGGER [get_debug_ports u_ila_0/probe7]

set_property port_width 1 [get_debug_ports u_ila_0/probe7]

connect_debug_port u_ila_0/probe7 [get_nets [list AD_SPI_CLK_OBUF]]

create_debug_port u_ila_0 probe

set_property PROBE_TYPE DATA_AND_TRIGGER [get_debug_ports u_ila_0/probe8]

set_property port_width 1 [get_debug_ports u_ila_0/probe8]

connect_debug_port u_ila_0/probe8 [get_nets [list AD_SPI_EN_B_OBUF]]

create_debug_port u_ila_0 probe

set_property PROBE_TYPE DATA_AND_TRIGGER [get_debug_ports u_ila_0/probe9]

set_property port_width 1 [get_debug_ports u_ila_0/probe9]

connect_debug_port u_ila_0/probe9 [get_nets [list AD_SPI_MISO_IBUF]]

set_property C_CLK_INPUT_FREQ_HZ 300000000 [get_debug_cores dbg_hub]

set_property C_ENABLE_CLK_DIVIDER false [get_debug_cores dbg_hub]

set_property C_USER_SCAN_CHAIN 1 [get_debug_cores dbg_hub]

connect_debug_port dbg_hub/clk [get_nets sys_ref_clk_BUFG]

方法二、HDL文件中例化ILA IP Core。

在IP Catalog中添加ILA核,基本的参数有:需要观测的信号个数(Number of Probes),采集深度(Sample data depth)和各个信号探头(Probe)的位宽。

调试时需要在Debug Probes 里面增加信号到波形窗口中!

Vivado ILA观察信号和调试过程的更多相关文章

- 关于火狐浏览器在开发调试过程中,出现javascript:void(0)的状态

关于火狐浏览器在开发调试过程中,出现javascript:void(0)的状态 由于火狐浏览器没有安装 Adobe Flash Player 19 NPAPI这个插件 安装好了之后就可以直接运行了

- S3C6410裸奔之旅——RVDS2.2编译、仿真、调试过程 LED流水灯---转的

S3C6410裸奔之旅——RVDS2.2编译.仿真.调试过程 LED流水灯 (2012-10-13 23:56:30) 转载▼ 标签: s3c6410裸奔 ok6410 rvds2.2 rvds2.2 ...

- MYSQL存储过程调试过程

mysql不像oracle有plsqldevelper工具用来调试存储过程,所以有几种简单的方式追踪执行过程: 1.用一张临时表,记录调试过程: 2.直接在存储过程中,增加select xxx,在控 ...

- stm32--FatFs调试过程(SPIFlash)

移植方法参见我的另一篇博客:<stm32--FatFs移植(SPIFlash)>. 本文仅记录在初次移植完成后,遇到的问题,和解决的过程. 调试记录: 问题1:f_open返回3,即磁盘没 ...

- Android APP 调试过程中遇到的问题。

调试过过程中APP安装完启动后有的时候会异常退出,报这个错误.有的时候可以直接启动.查找不到原因.网上说把commit方法替换成commitAllowingStateLoss() 也无效. Andro ...

- 调试过程中发现按f5无法走进jdk源码

debug 模式 ,在fis=new FileInputStream(file); 行打断点 调试过程中发现按f5无法走进jdk源码 package com.lzl.spring.test; impo ...

- 0xe7f001f0!?NDK调试过程,无故抛出SIGSEGV。

arm调试过程,如果抛一个SIGSEGV,地址在 0xe7f001f0 附近,原因居然是因为我在调试.当我使用n指令跳到下一行代码时,往往变成了continue指令一样地执行.还不确定地抛出SIGSE ...

- VS·调试过程中某个操作导致调试突然退出之解决方案

阅文时长 | 0.11分钟 字数统计 | 232字符 主要内容 | 1.引言&背景 2.声明与参考资料 『VS·调试过程中某个操作导致调试突然退出之解决方案』 编写人 | SCscHero 编 ...

- Vivado与SDK的联合调试方法-使用ILA

首先介绍一下我的硬件平台:使用的开发板为米联客出的MIZ702,这个开发板与ZedBoard是兼容的. Vivado硬件调试有几种手段:ILA(集成逻辑分析器Integrated Logic Anal ...

随机推荐

- Python下opencv使用笔记(十一)(详解hough变换检测直线与圆)

http://blog.csdn.net/on2way/article/details/47028969 http://blog.csdn.net/mokeding/article/details/1 ...

- sql server alter column identity

上网找 alter column identity 语句,将表中的一个字段调整成自动新增.发现没有. 跟踪了一下sql server 执行这一动作的语句,发现是新建了新表,将字段修改成自动新增,然后将 ...

- 了解Web的相关知识

一.WWW基础 WWW(world wide web, 万维网)是Internet上基于客户端/服务器体系结构的分布式多平台的超文本超媒体信息服务系统.它利用超文本(hypertext).超媒体(hy ...

- Spring Boot笔记一

Spring Boot 入门 Spring Boot 简介 > 简化Spring应用开发的一个框架:> 整个Spring技术栈的一个大整合:> J2EE开发的一站式解决方案: 微服务 ...

- 牛顿迭代法--求任意数的开n次方

牛顿迭代法是求开n次方近似解的一种方法,本文参考. 引言 假如\(x^n = m\),我们需要求x的近似值. 我们设\(f(x) = x^n - m\), 那么也就是求该函数f(x)=0时与x轴的交点 ...

- C# Stream篇(—) -- Stream基类-----转载

C# Stream篇(—) -- Stream基类 写在前头: Stream系列文章共收录7篇,本着备忘和归纳的目的本着备忘和归纳的目的,全部收录于本分类中. 下面是有原文连接,望各位看官还是到原作者 ...

- LeetCode 876. Middle of the Linked List(获得链表中心结点)

题意:获得链表中心结点.当有两个中心结点时,返回第二个. 分析:快慢指针. /** * Definition for singly-linked list. * struct ListNode { * ...

- Redis 事务在 SpringBoot 中的应用 (io.lettuce.core.RedisCommandExecutionException: ERR EXEC without MULTI)

我们在 SpringBoot 中使用 Redis 时,会引入如下的 redis starter <dependency> <groupId>org.springframewor ...

- JS 瀑布流效果

JS瀑布流效果 <!DOCTYPE html> <html> <head> <meta charset="utf-8" /> < ...

- java 实现用户自由选择字段实现导出EXCEL表格

package com.thinkgem.jeesite.common.utils.excel; import java.io.File; import java.io.OutputStream; i ...