每天进步一点点------Modelsim添加Xilinx仿真库的详细步骤

Modelsim,可以选型SE和XE两个版本。Modelsim XE可以直接被ISE调用,而Modelsim SE需要手动添加仿真库。但SE版和OEM版在功能和性能方面有较大差别,比如对于大家都关心的仿真速度问题,以Xilinx公司提供的OEM版本ModelSim XE为例,对于代码少于40000行的设计,ModelSim SE 比ModelSim XE要快10倍;对于代码超过40000行的设计,ModelSim SE要比ModelSim XE快近40倍。所以我还是选择了Modelsim SE,为此google了一下,找到了一个手动添加仿真库的方法,并轻松完成配置。详细步骤如下,有需要的兄弟们可以参考一下。

为modelsim生成3个库。

首先,介绍一下这三个库。

Simprim_ver:用于布局布线后的仿真。

Unisim_ver :如果要做综合后的仿真,还要编译这个库。

Xilinxcorelib_ver:如果设计中调用了CoreGen产生的核,则还需要编译这个库。

我们要为modelsim生成的是标准库。所谓的标准库就是modelsim运行后,会自动加载的库。不过这方面我还不是很肯定。因为我在后仿真时,还是要为仿真指定库的路径,不然modelsim找不到。

第一步:在modelsim环境下,新建工程,工程的路径与你想把库存储的路径一致。

第二步:新建库,库名起作simprim_ver。我们首先就是要建的就是这个库。

第三步:在modelsim的命令栏上,打下如下命令:

vlog -work simprim_ver d:/Xilinx/verilog/src/simprims/*.v

其中的d:/Xilinx是我的Xilinx的安装路径,你把这个改成你的就行了。以下凡是要根据自己系统环境改变的内容,我都会用绿色标出,并加一个下划线。编译完之后,你会发现你的工程文件夹下出现了一个simprim文件夹,里面又有很多个文件夹。这些就是我们要的库了。

第四步:按照上面的方法,编译另外两个库。所需要键入的命令分别如下:

vlog -work unisim_ver d:/Xilinx/verilog/src/unisims/*.v

vlog -work xilinxcorelib_ver d:/Xilinx/verilog/src/XilinxCoreLib/*.v

如果你想要编译的是VHDL的库,你需要建立的库分别是simprim,unisim和xilinxcorelib。这三个库所需要的modelsim指令分别如下:

vcom –work simprim d:Xilinx/VHDL/src/simprims/simprim_Vcomponents.vhd

vcom –work simprim d:Xilinx/VHDL/src/simprims/simprim_Vpackage.vhd

vcom –work simprim d:Xilinx/VHDL/src/simprims/simprim_VITAL.vhd

vcom –work unisim d:Xilinx/VHDL/src/unisims/unisim_VCOMP.vhd

vcom –work unisim d:Xilinx/VHDL/src/unisims/unisim_VPKG.vhd

vcom –work unisim d:Xilinx/VHDL/src/unisims/unisim_VITAL.vhd

vcom –work unisim d:Xilinx/VHDL/src/unisims/unisim_VCFG4K.vhd

vcom –work xilinxcorelib d:Xilinx/VHDL/src/ XilinxCoreLib/*.vhd

关于VHDL方面,我没有实践过,如果有误的话,改一下应该问题也不大。

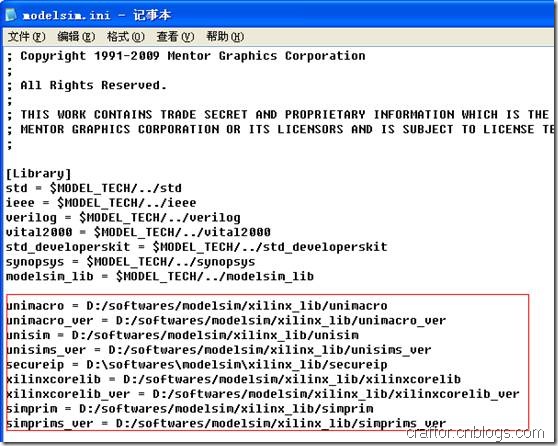

第五步:把库建好后,接下来的事情就是使它成为modelsim的标准库。这只要修改modelsim安装目录下的modelsim.ini文件就可以了。修改后的内容如下:

[Library]

std = $MODEL_TECH/../std

ieee = $MODEL_TECH/../ieee

verilog = $MODEL_TECH/../verilog

vital2000 = $MODEL_TECH/../vital2000

std_developerskit = $MODEL_TECH/../std_developerskit

synopsys = $MODEL_TECH/../synopsys

modelsim_lib = $MODEL_TECH/../modelsim_lib

simprim_ver = G:/EDA/Xilinx/simprim_ver(库的路径,以下同)

unisim_ver = G:/EDA/Xilinx/unisim_ver

xilinxcorelib_ver = G:/EDA/Xilinx/xilinxcorelib_ver

注意的是,这个文件是只读属性。修改之前要把这个属性去掉。

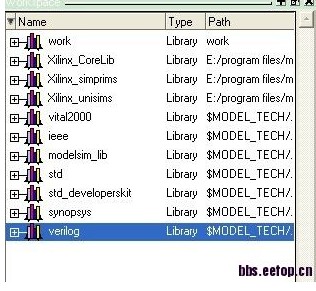

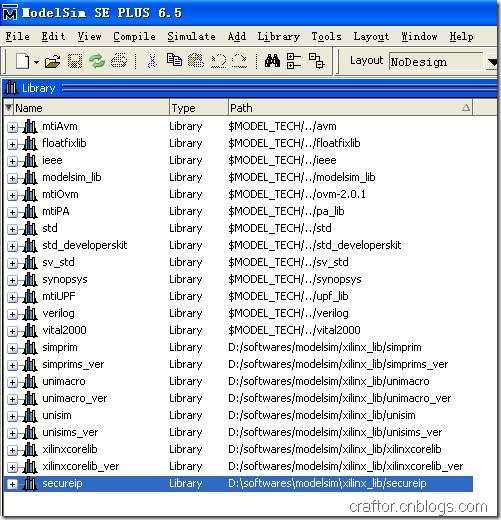

第六步:关掉工程,重启modelsim。查看这3个库是否在library框里面。

如果你看到了,那么恭喜!

至此,就可以用ISE直接调用Modelsim做仿真了。

用modelsim 仿真 Xilinx 的ram 模块时报了下面的错误

# ** Error: (vsim-3033) ram_ip.v(120): Instantiation of 'BLK_MEM_GEN_V2_7' failed. The design unit was not found.

我也把Xilinx的XilinxCoreLib simprims unisims三个库编译到modelsim的目录下了

哪位大大帮帮我

今天看有一个教程,发现在编

译的时候选择start stimulation,之后再

之后再libiary中把corelib的库在添加进来

就好了

在ModelSim中添加Xilinx仿真库

说明:

l ModelSim一定要安装在不带空格的目录下,即不要安装在“Program Files”目录下。如作者是安装在D:\softwares\Modelsim目录下。

l ISE软件也最好安装在不带空格的目录下。

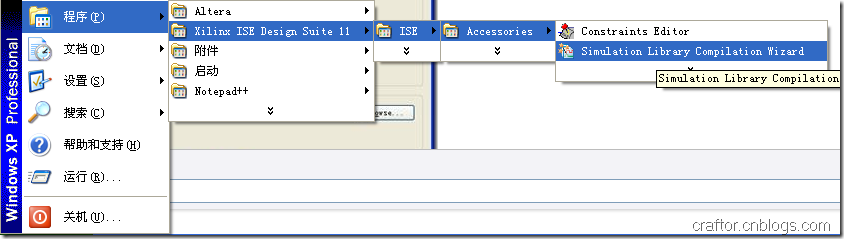

1、找到开始菜单->程序->Xilinx ISE Design Suite 11 -> ISE -> Accessories -> Simulation Library Compilation Wizard.

2、选定ModelSim的版本,以及指定ModelSim的安装路径。

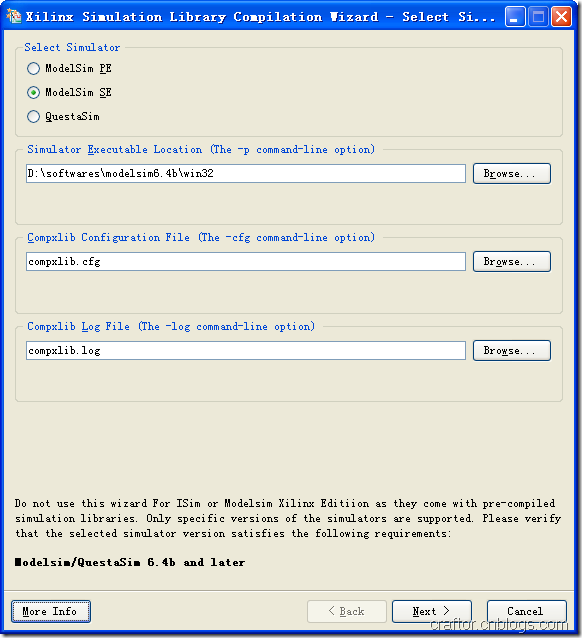

3、选择Both VHDL and Verilog。

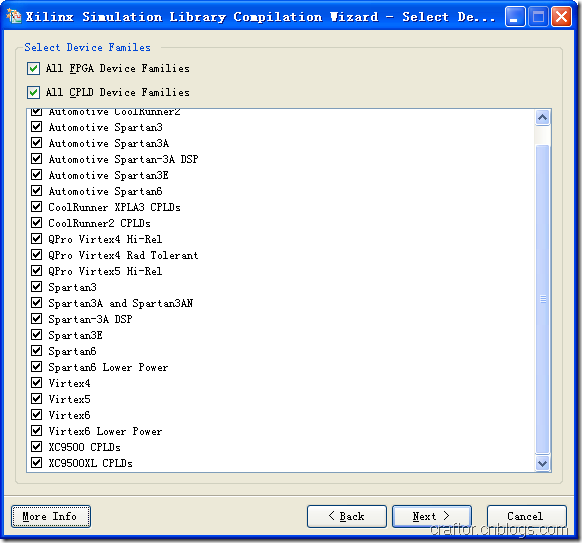

4、选择支持哪些系列的芯片,看自己需要增减。

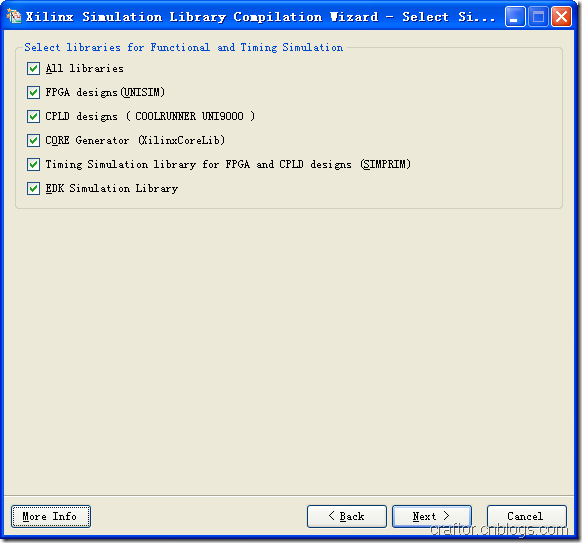

5、默认选全上即可。

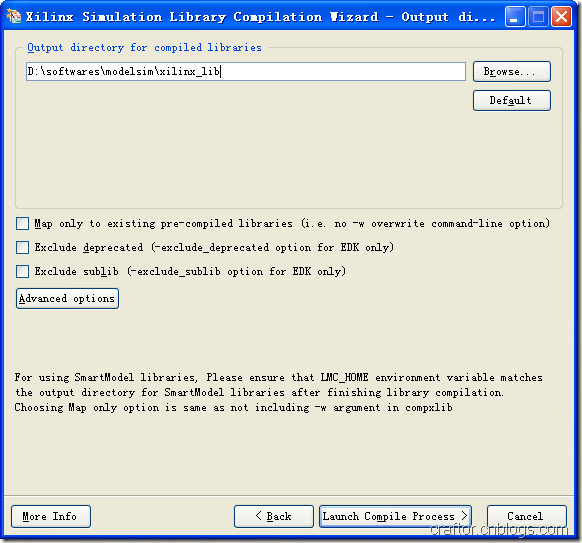

6、指定编译完后的库存放位置,这里作者在modelsim安装目录下新建了xilinx_lib的文件夹,并指定到这里。(注意不要指向带空格的路径)

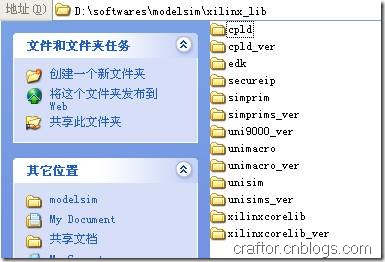

7、运行 Lauch Compile Process,即开始编译库文件,需要几十分钟。编译完成后应该在xilinx_lib目录下多出如下文件夹:

8、右键打开modelsim目录下的modelsim.ini文件,先将其“只读”属性去掉。然后用记事本打开。在[Library]下面添加如下代码,即之前编译好的Xilinx库的路径。

unimacro = D:/softwares/modelsim/xilinx_lib/unimacro

unimacro_ver = D:/softwares/modelsim/xilinx_lib/unimacro_ver

unisim = D:/softwares/modelsim/xilinx_lib/unisim

unisims_ver = D:/softwares/modelsim/xilinx_lib/unisims_ver

secureip = D:\softwares\modelsim\xilinx_lib/secureip

xilinxcorelib = D:/softwares/modelsim/xilinx_lib/xilinxcorelib

xilinxcorelib_ver = D:/softwares/modelsim/xilinx_lib/xilinxcorelib_ver

simprim = D:/softwares/modelsim/xilinx_lib/simprim

simprims_ver = D:/softwares/modelsim/xilinx_lib/simprims_ver

9、再次打开ModelSim,即可以看到Xilinx的库已经默认出现在了库列表里。以后仿真Xilinx的IP核时,就不用每次都添加库了。

每天进步一点点------Modelsim添加Xilinx仿真库的详细步骤的更多相关文章

- 在ModelSim中添加Xilinx仿真库

在ModelSim中添加Xilinx仿真库 说明: l ModelSim一定要安装在不带空格的目录下,即不要安装在“Program Files”目录下.如作者是安装在D:\softwares\Mode ...

- modelsim编译Xilinx器件库的另一种方法(节省时间)

以前在用modelsim对Xilinx进行器件库编译时,我用的比较多的是直接在ISE中编译器件库,感觉很方便简单,就是编译时间有点长.自从前段时间,在自己电脑装MathType,360杀毒软件将它视为 ...

- Modelsim编译Xilinx器件库的另一种方法

由 xooo 于 星期五, 09/18/2015 - 15:35 发表 以前在用modelsim对Xilinx进行器件库编译时,我用的比较多的是直接在ISE中编译器件库,感觉很方便简单,就是编译时间有 ...

- xilinx仿真库的作用(原创)

① secureip库:硬核(HARD IP)仿真(功能仿真和时序仿真)模型(hard IP simulation model),比如PowerPC.PCIE.SRIO.DDR等.Simulation ...

- linux下ftp(vsftpd)添加用户及设置权限详细步骤

1.环境:ftp为vsftp.被限制用户名为test.被限制路径为/home/test2.建用户:在root用户下:useradd test //增加用户test,并制定test用户的主目录为/hom ...

- 用Modelsim SE 直接仿真 Altera(Intel PSG) IP核 需要注意的问题

如果我们直接用Modelsim SE仿真 Altera IP核,首先会进入Quartus II目录下找到IP核对应的仿真库源文件,然后在Modelsim SE中进行编译,添加到Modelsim SE的 ...

- 87.在ModelSim中添加Xilinx ISE仿真库

在ModelSim中添加Xilinx ISE仿真库 说明: l ModelSim一定要安装在不带空格的目录下,即不要安装在“Program Files”目录下.如作者是安装在D:\softwares\ ...

- 如何用ModelSim对Xilinx ISE产生的网表进行仿真

图: 在对设计的芯片进行测试时,经常要用到FPGA,可是里面的仿真工具却不如Modelsim那么好用,且在规模比较大时,ISE在仿真时,软件经常会报告内存限制的问题,此时一般会切换到Modelsim软 ...

- Xilinx ISE如何调用Modelsim进行联合仿真

图: 在对设计的芯片进行测试时,经常要用到FPGA,可是里面的仿真工具却不如Modelsim那么好用,且在规模比较大时,ISE在仿真时,软件经常会报告内存限制的问题,此时一般会切换到Modelsim软 ...

随机推荐

- javascript 浅复制 和 深复制

如何区分深拷贝与浅拷贝,简单点来说,就是假设 B复制了A,当修改A时,看B是否会发生变化,如果B也跟着变了,说明这是浅拷贝, 如果B没变,那就是深拷贝 实现思路 1 json 深度拷贝 2 遍历递归 ...

- elasticsearch kibana 安装 配置

二.Elasticsearch 配置信息 2.1 因为 Elasticsearch 可以执行脚本文件,为了安全性,默认不允许通过 root 用户启动服务.我们需要新创建用户名和用户组启动服务 2. ...

- Linux安装virtualenvwrapper

1.pip install virtualenvwrapper 2.export WORKON_HOME=/home/virtualenv //配置虚拟环境变量,以后直接mkvirtualenv 虚 ...

- CCS过渡和动画

过渡 过渡能让使用过渡的元素在样式发生变化时(例如鼠标划过,单击按钮,点击图片时,颜色,尺寸,位置等样式发生变化),定义变化过程中的动画,让变化不再是瞬间产生. 过渡样式使用transition定义, ...

- 修饰符 public、 private 和 protected和区别

TypeScript 可以使用三种访问修饰符(Access Modifiers),分别是 public.private 和 protected. public 修饰的属性或方法是公有的,可以在任何地方 ...

- C++ 常用编程--Swap函数有几种写法?

C++ 常用编程--Swap函数有几种写法? 在说C++模板的方法前,我们先想想C语言里面是怎么做交换的. 举个例子,要将两个int数值交换,是不是想到下面的代码: void swap(int& ...

- C——简单计算器(HDU1237)

题目: 读入一个只包含 +, -, *, / 的非负整数计算表达式,计算该表达式的值. Input测试输入包含若干测试用例,每个测试用例占一行,每行不超过200个字符,整数和运算符之间用一个空格分隔 ...

- Hibernate框架预览以及基础介绍

前言 从本节我们开始进入到对于Hibernate框架的学习,当前Hibernate框架还未正式发布6.0稳定版本,所以这里我们以5.4.12Final版本进行讲解. Hibernate框架 Hiber ...

- K8S 容器挂载Windows 文件共享目录,访问出现Permission denied的解决办法

K8S Pod,Docker 容器挂载Windows主机目录,访问相应的文件出现Premission denied的权限访问问题 Windows远程共享目录为//192.168.61.115/huas ...

- Vue整合d3.v5.js制作--柱状图(rect)

先上效果图: 图中柱状图变成纯蓝色是鼠标滑动过的颜色(颜色可改,本人配色能力十分的强,建议直接用默认设置即可 ( ᖛ ̫ ᖛ )ʃ)) 1.环境说明 Vue版本:"vue": &q ...