国产gowin开发板GW1NR-9K的PSRAM使用说明

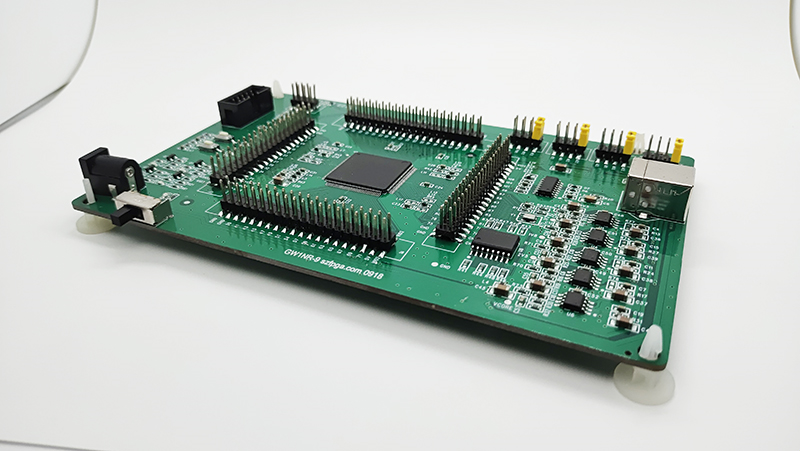

开发板子采用GW1NNR-LV9LQ144PC6/I5 FPGA器件。具有低功耗,瞬时启动,高安全性,低成本,方便扩展等特点。本开发板价格价格便宜,板子扩张性容易,帮助用户比较快速进入国产FPGA学习能力。

开发板集成多个GPIO接口和多个LVDS接口,电压可以从3.3,2.5,1.8,1.2V选择。用户可以选择不同电压适配不同的IO口。其中每个VCCIO也是独立供电,可以很简单改装成其他的不同bank不同电压要求。

芯片资源GW1NNR-LV9LQFP144的资源有8640的LUT4,并且还有26个18K SRAM快,2个PLL锁相环,内部自带PSRAM 64M空间,

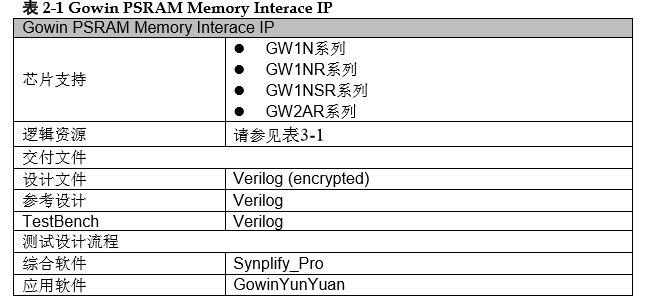

Gowin PSRAM Memory Interface IP是一个通用的PSRAM内存接口IP, 符合PSRAM标准协议。该IP包含PSRAM内存控制逻辑(Memory Controller Logic)与对应的物理层接口(Physical Interface,PHY)设计。Gowin PSRAM Memory Interace IP 为用户提供一个通用的命令接口,使其与 PSRAM 内存 芯片进行互连,完成用户的访存需求。

- 能与标准的 PSRAM 器件接口;

- 支持存储器数据路径宽度为 8、16、24、32、40、48、56 和 64 位;

- 支持 x8 数据宽度的内存芯片;

- 可编程突发长度 16、32、64、128;

- 时钟比例为 1:2

- 支持初始延时为 6;

- 支持固定延时模式;

- 支持电源关闭选项;

- 可配置的驱动强度;

- 可配置的自刷新区域;

- 可配置的刷新速率;

- 单通道双通道两种操作模式 IP 可选。

Gowin PSRAM Memory Interace IP 可支持的数据速率与效率为:

- 最高工作数据速率 333Mbps;

- 突发长度 128,带宽效率为 74%;

- 突发长度 64,带宽效率为 59%;

- 突发长度 32,带宽效率为 42%;

- 突发长度 16,带宽效率为 26%

Gowin PSRAM Memory Interace IP 基本结构如图 4-1 所示,主要包含 Memory Controller Logic、Physical Interface 等模块。。 图 4-1 中的 User Design 是 FPGA 中需要与外部 PSRAM SDRAM 芯片 所连接的用户设计。 图 4-1

Memory Controller Logic 是 Gowin PSRAM Interace IP 的逻辑模块,位 于 User Design 与 PHY 之间。Memory Controller Logic 接收来自用户接口 的命令、地址与数据,并按照一定逻辑顺序进行存储。 用户发送的写、读等命令和地址在 Memory Controller Logic 中进行排序 重组,组合成满足 PSRAM 协议的数据格式。同时,写数据时 Memory Controller Logic 会对数据进行重组和缓存,以满足命令和数据之间的初始延 时值,读数据时,Memory Controller Logic 会对读回的数据进行采样和重组, 恢复成正确数据。 PSRAM Memory Controller 主要由以下几个模块组成:CMD 单元、 WR_Data 单元、RD_Data 单元等,主要结构如图 4-2 所示。

PSRAM 必须经过读校准操作才能进行正常的写、读操作。因此上电后 PHY 会对 PSRAM 进行初始化读校准操作,初始化完成后返回初始化完成标 志 init_calib,单通道 PSRAM IP 会将两颗 psram 颗粒同时初始化,而双通 道 IP 则是两颗 psram 颗粒各自初始化,并将两个初始化完成信号分别送出 给用户使用。

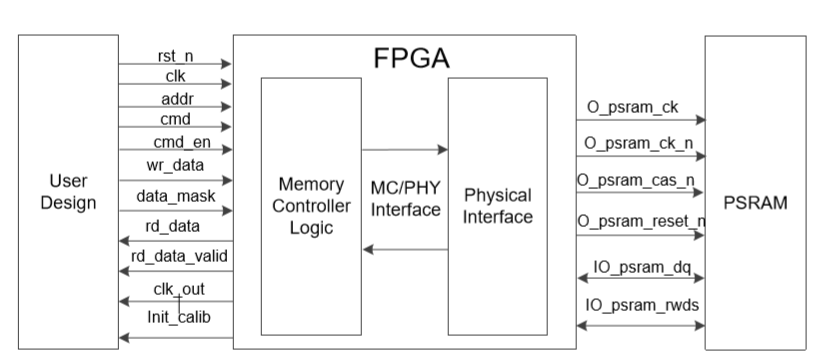

用户可通过 addr、cmd、cmd_en 等用户接口发送操作命令与地址。

addr 为地址数据端口; 连续地址写操作时,相邻两次操作地址自加突发长度/2,连续地址读操作 相同;

cmd 为命令数据端口;

cmd_en 为地址与命令使能信号,高电平有效;

双通道 PSRAM IP 和单通道 PSRAM IP 的操作方式一致,但是双通道

PSRAM IP 两个通道的命令和地址是独立的,需要分别给出控制信号。 在应用中,用户接口的地址总线与物理内存的 ROW、Upper Column、 Lower Column 之间存在一定的映射关系,在本设计中,按照 ROW-Upper Column-Lower Column 的顺序进行依次排列,其寻址方案如图 4-5 所示。用 户在应用中,只需按照需要给出地址,不需要关心映射关系。

用户在使用 PSRAM 时,读写命令间隔需根据颗粒 tRWR 值进行计算, 以 166M 时钟,颗粒使用 W955D8MBY 为例,tRWR 最小值为 36ns,即读 写命令间隔需要大于 6 个时钟周期,在实际使用读写切换中,建议用户在写 数据全部写入后再进行读取操作,在读数据全部读出后,再进行写操作; 在用户端实际使用时两个命令(写-读/读-写/写-写/读-读)间隔需满足最 小间隔周期(图 4-8 中 Tcmd 周期数),即突发长度为 16 时,命令间隔最小 为 15 个时钟周期;突发长度为 32 时,命令间隔最小为 19 个时钟周期;突 发长度为 64 时,命令间隔最小为 27 个时钟周期;突发长度为 128 时,命令 间隔最小为 43 个时钟周期。

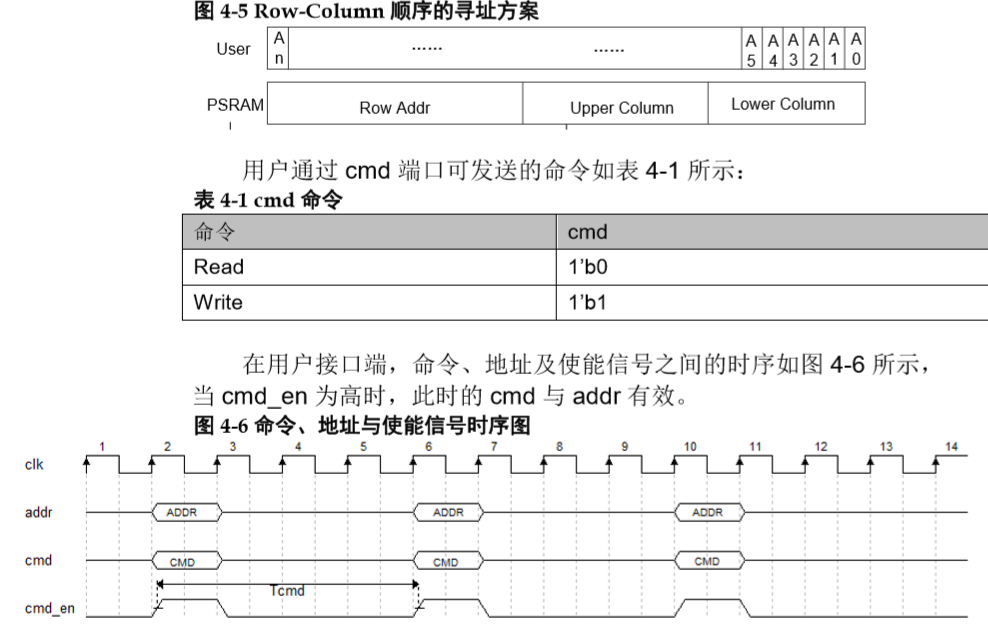

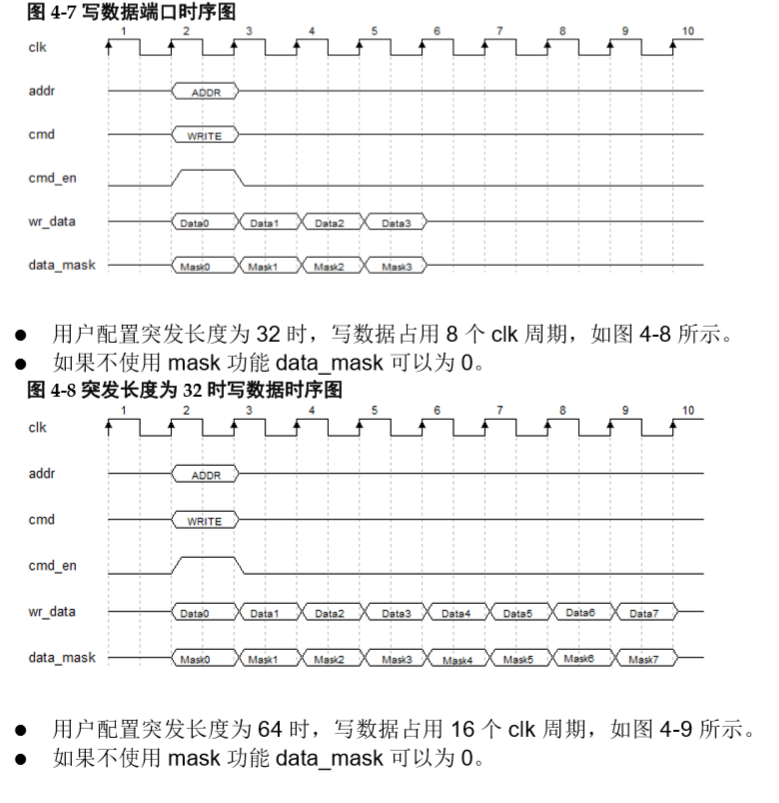

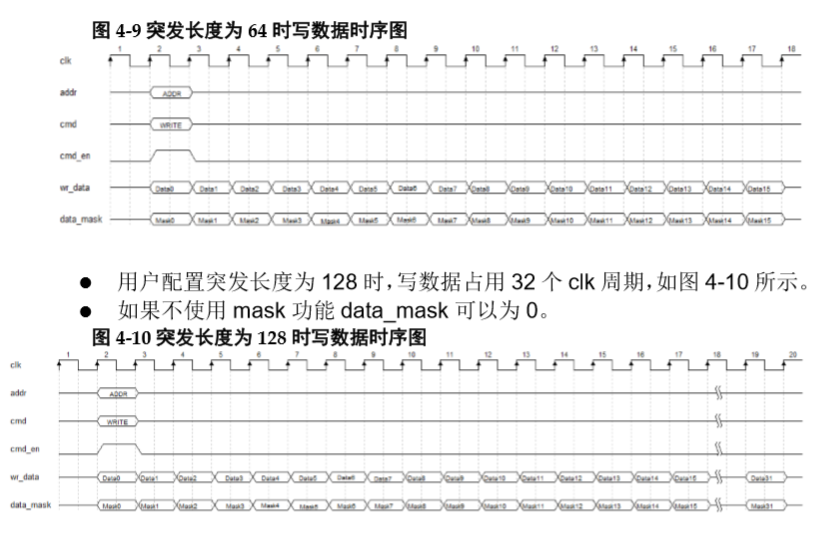

写数据

用户可通过用户接口 wr_data、data_mask 等端口将写数据发送给 Gowin PSRAM Memory Interface IP,写数据经过处理后会发送给 PSRAM 颗粒。

wr_data 为写数据端口;

data_mask 为写遮掩端口;

写数据通道与命令通道之间存在多种时序情况,下图以突发长度为 16 为 例;

双通道 PSRAM IP 与单通道 PSRAM IP 写操作模式一致,但是双通道 PSRAM IP 两个通道的数据端口是独立的,需要分别给出写数据;

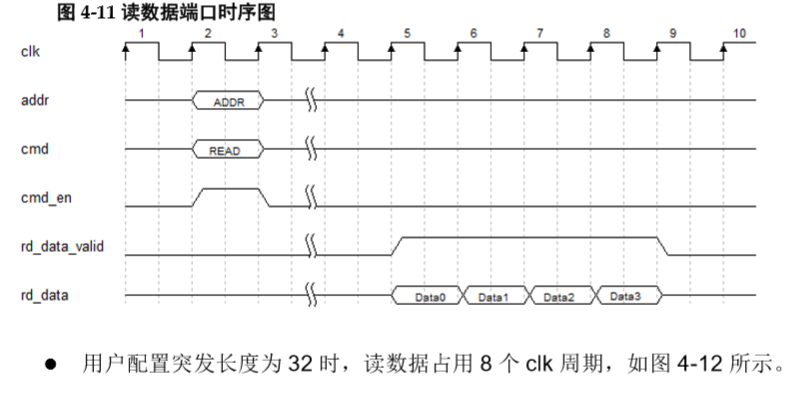

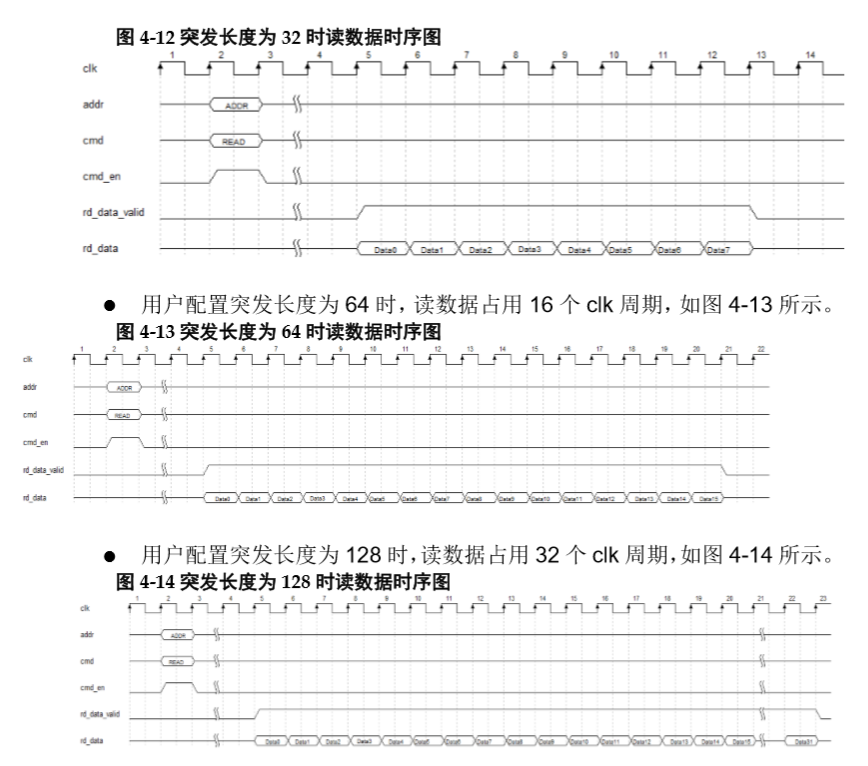

读数据

用户可通过用户接口rd_data、rd_data_valid读取PSRAM返回的数据。

端口 rd_data 为返回的读数据端口;

端口信号 rd_data_valid 为读数据有效端口,当其为高电平时,指示此时 返回的 rd_data 有效;

读数据通道与命令通道之间存在多种时序情况,下图以突发长度为 16 为 例;

双通道 PSRAM IP 与单通道 PSRAM IP 读操作模式一致,但是双通道 PSRAM IP 两个通道的数据端口是独立的,需要分别接收 rd_data_valid 信号和 rd_data 数据

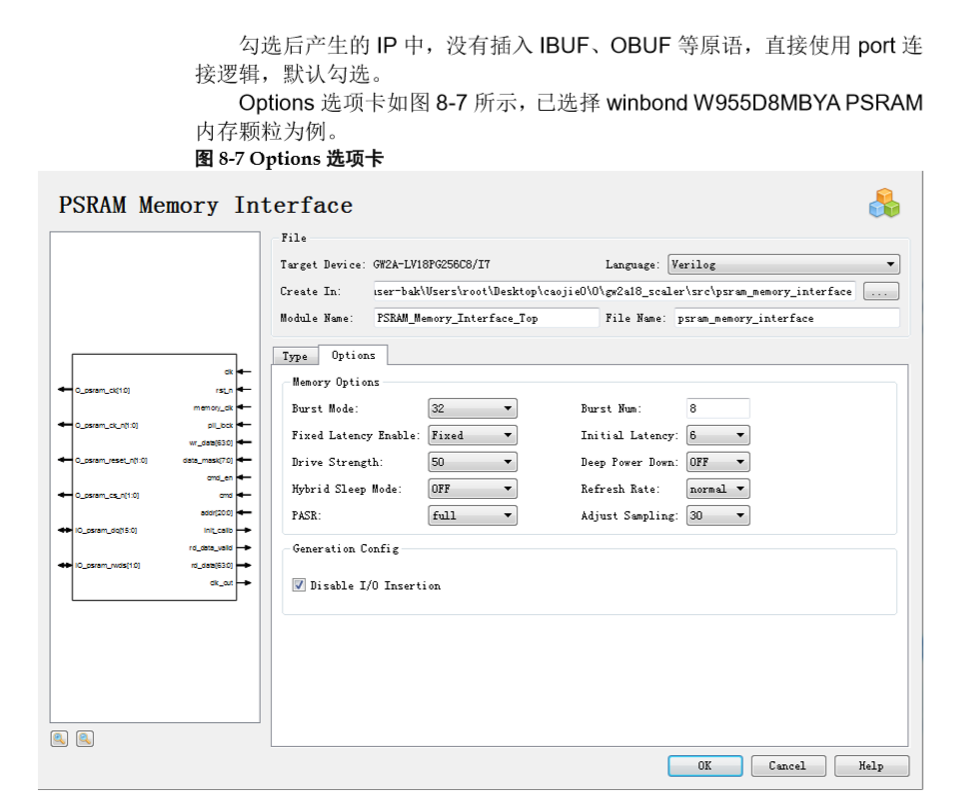

配置选项默认。

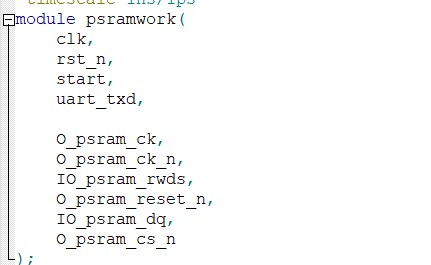

代码要记得顶层必须输出基本的IO口。

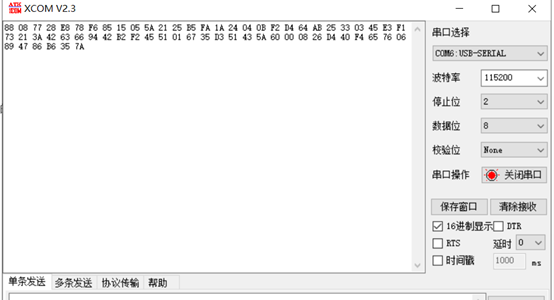

用上面的开发板子,执行测试。

按键KEY1的时候,写入psram的数据,并且都psram的数据,输出到串口上面。

十六进制显示,2个停止位,115200波特率,数据位8位,没有校验位。

国产gowin开发板GW1NR-9K的PSRAM使用说明的更多相关文章

- AC6102开发板USB3.0测试和使用说明

AC6102开发板USB3.0测试和使用说明 概述 AC6102上集成了一颗Cypress 推出的高性能USB3.0传输芯片CYUSB3014,Cypress称之为EZ-USBFX3.该芯片性能强劲, ...

- 华大单片机开发板HC32L13X上手入门

HC32L136开发板(如下图所示)分为板载调试模块(左半部分)和MCU开发电路(右半部分).二者中间通过邮票孔相连,如果将板子从中间掰开,板载调试模块就可以当一个CMSIS-DAP的仿真器来使用.此 ...

- 华大单片机开发板HC32F030上手入门

HC32F030开发板(如下图所示)分为板载调试模块(左半部分)和MCU开发电路(右半部分).二者中间通过邮票孔相连,如果将板子从中间掰开,板载调试模块就可以当一个CMSIS-DAP的仿真器来使用.此 ...

- ESP-EYE V2.1 开发板 WINDOWS 10 开发入门

准备工作 1 × ESP-EYE V2.1 开发板 1 × Micro USB B 电缆 1 × PC(Windows10) 简介 ESP-EYE 是一款面向人脸识别和语音识别市场的开发板,搭载 ES ...

- 转载:百为STM32开发板教程之十二——NAND FLASH

http://bbs.21ic.com/icview-586200-1-1.html 百为STM32开发板教程之十二——NAND FLASH 参考资料:百为stm32开发板光盘V3\百为stm32开发 ...

- 转载:百为STM32开发板教程之十一——NOR FLASH

转载:http://bbs.21ic.com/icview-586199-1-1.html 百为STM32开发板教程之十一——NOR FLASH 参考文档:百为stm32开发板光盘\st官方参考资料\ ...

- 东芝开发板驱动OLED模块显示LOGO图片

前言 在之前的两篇评测文章: 使用系统定时器SysTick实现精确延时微秒和毫秒函数 东芝MCU实现位带操作 介绍了系统SysTick实现精确延时,GPIO的输入输出使用,并实现了位带方式操作GPIO ...

- 东芝半导体最新ARM开发板——TT_M3HQ开箱评测

前言 最近从面包板社区申请到一块东芝最新ARM Cortex-M3内核的开发板--TT_M3HQ,其实开发板收到好几天了,这几天一直在构思怎么来写这第一篇评测文章,看大家在社区也都发了第一篇评测,我也 ...

- 织女星开发板RISC-V内核实现微秒级精确延时

前言 收到VEGA织女星开发板也有一段时间了,好久没玩了,想驱动个OLED屏,但是首先要实现IIC协议,而实现IIC协议,最基本的就是需要一个精确的延时函数,所以研究了一下如何来写一个精确的延时函数. ...

- 真正的RISC-V开发板——VEGA织女星开发板开箱评测

前言 由于最近ARM公司要求员工"停止所有与华为及其子公司正在生效的合约.支持及未决约定",即暂停与华为的相关合作,大家纷纷把注意力投向了另一个的处理器架构RISC-V,它是基于精 ...

随机推荐

- nest.sh 脚本 发布服务

每次发布后端nest 直接执行一个脚本即可 给脚本赋值权限 chomd 777 nest.sh nest.sh 脚本 #!/bin/bash cd /root/gateway-study git pu ...

- Prettier 和 ESLint 冲突解决方案 eslint-config-prettier eslint-plugin-prettier

划重点 eslint-config-prettier 禁用 eslint 冲突配置 eslint-plugin-prettier Prettier先格式化 (默认是先eslint格式化,再Pretti ...

- python 读取txt并绘制波形图实例解析

一 用python绘图有很多方法,笔者找到了一种最简单的方法,使用非常便利,这里分享一下: import numpy as np import matplotlib.pyplot as plt a = ...

- python的GUI工具dearpygui入门指南

一 概念 1.dearpygui 它是一个易于使用的.动态的.GPU加速的.跨平台的.适用于Python的图形用户界面工具包(GUI). 2.特性 GPU 渲染 简单的内置异步功能支持 完整的主题和样 ...

- Java/Kotlin 密码复杂规则校验

原文地址: Java/Kotlin 密码复杂度校验 | Stars-One的杂货小窝 每次有那个密码复杂校验,不会写正则表达式,每次都去搜,但有时候校验的条件又是奇奇怪怪的,百度都搜不到 找到了个代码 ...

- 使用docker-compose管理freeswitch容器

概述 之前的文章我们介绍过如何将freeswitch做成docker镜像,也使用命令行模式正常启动了fs的docker容器. 但是当我们需要同时管理多个docker容器的时候,还是使用docker-c ...

- STM32 启动代码分析

PS:要转载请注明出处,本人版权所有. PS: 这个只是基于<我自己>的理解, 如果和你的原则及想法相冲突,请谅解,勿喷. 前置说明 本文作为本人csdn blog的主站的备份.(Bl ...

- Serverless学习笔记

Serverless 闲言碎语 前段时间看了一些Serverless的文章,恰好最近又听了一门Serverless的应用实践课程,就把笔记拿出来和大家分享一下,如表述有误还请各位斧正 大家关心的问题 ...

- Python简单程序设计(计算程序设计(公式)篇)

如题: 解题方式如下:

- js中订阅发布模式bus

export default { list: {}, // 事件中心集中地 /** * 发布订阅 * @param {string} name 事件名 * @param [...args] */ $e ...