verilog 代码分析与仿真

verilog 代码分析与仿真

注意:使用vivado 自带的仿真工具, reg和wire等信号需要赋予初始值

边沿检测

module signal_test(

input wire cmos_pclk_i,

input wire cmos_vsync_i

);

// 上升沿捕获

reg [:] vsync_d;

wire vsync_start;

wire vsync_end;

always @(posedge cmos_pclk_i)

begin

vsync_d <= {vsync_d[], cmos_vsync_i};

end

assign vsync_start = vsync_d[] && (!vsync_d[]);

assign vsync_end = (!vsync_d[]) && vsync_d[];

endmodule

/*

add_force {/signal_test/cmos_pclk_i} -radix hex {1 0ns} {0 50000ps} -repeat_every 100000ps

add_force {/signal_test/cmos_vsync_i} -radix hex {1 0ns} {0 300ns} {1 700ns}

*/

仿真结果:

时钟二分频的巧用

//在一定区域内,将时钟cmos_pclk_i 进行二分频

reg byte_flag = ;

always@(posedge cmos_pclk_i)

begin

if(rst)

byte_flag <= ; else if(cmos_href_i) //控制信号,固定区域

byte_flag <= ~byte_flag; else

byte_flag <= ;

end //将byte_flag 延时一拍,从仿真图中才可以看出此处的用意

reg byte_flag_r0 = ;

always@(posedge cmos_pclk_i)

begin

if(rst)

byte_flag_r0 <= ; else

byte_flag_r0 <= byte_flag;

end

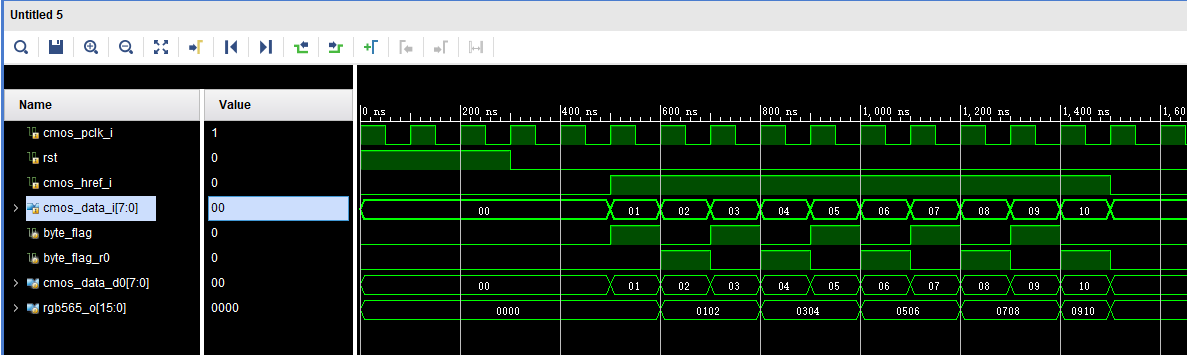

仿真结果:

数据采集与数据融合

注意rgb565信号的生成

//接收摄像头的数据,当href为高电平时,采集数据,当为低电平时,用0填充

reg [:] cmos_data_d0 = ;

always@(posedge cmos_pclk_i)

begin

if(rst)

cmos_data_d0 <= 'd0; else if(cmos_href_i)

cmos_data_d0 <= cmos_data_i; //MSB -> LSB else if(~cmos_href_i)

cmos_data_d0 <= 'd0;

end reg [:] rgb565_o = ;

always@(posedge cmos_pclk_i)

begin

if(rst)

rgb565_o <= 'd0; //当href为高电平,byte_flag 为高时候,对rgb565数据进行拼装

else if(cmos_href_i & byte_flag)

rgb565_o <= {cmos_data_d0,cmos_data_i}; //MSB -> LSB else if(~cmos_href_i)

rgb565_o <= 'd0;

end

仿真结果:

成功的将两个数融合在一起,一个是寄存器里面保存的数据,一个是实时的输入数据。

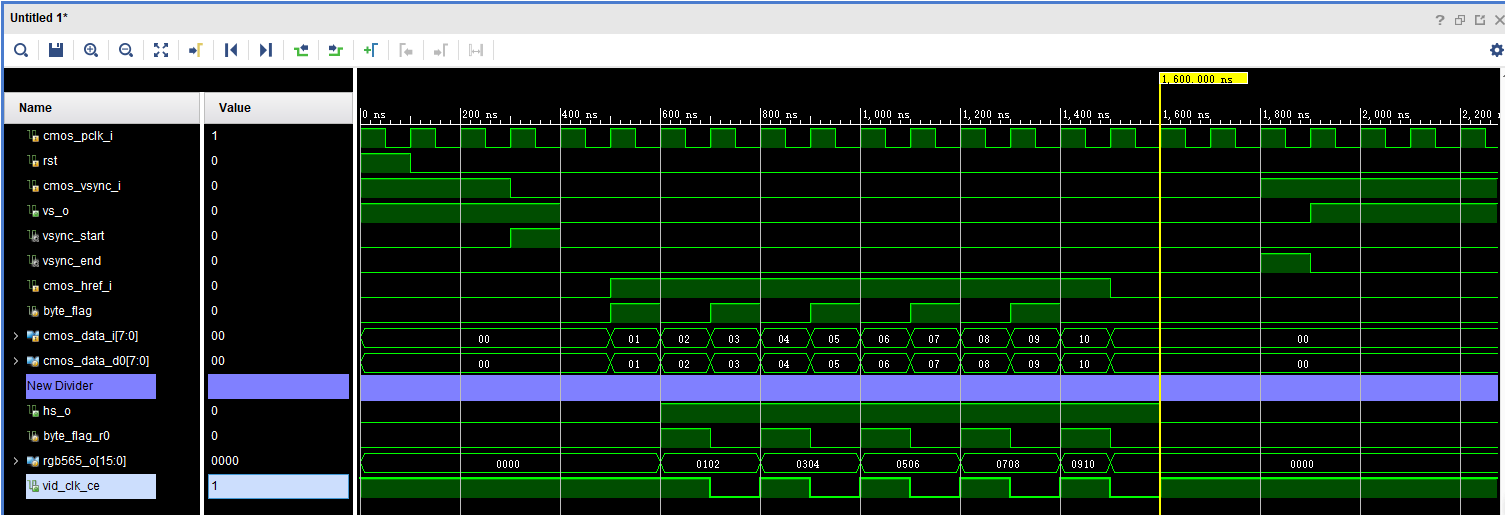

关于像素的输出使能信号的生成

assign vs_o = vsync_d[];

assign hs_o = href_d[];

assign vid_clk_ce = (byte_flag_r0&hs_o)||(!hs_o);

仿真结果:

当hs_o 为高时,摄像头输出有效数据,2个2个一起,每当数据进行更新时,ce信号产生,当输出的是消隐区数据的时候,ce信号一直使能。

module signal_test_1(

input wire cmos_pclk_i,

input wire rst,

input wire [:]cmos_data_i,

input wire cmos_href_i,

input wire cmos_vsync_i,

output wire hs_o,

output wire vs_o,

output wire vid_clk_ce

);

/*parameter[5:0]CMOS_FRAME_WAITCNT = 4'd15;*/

// 对行场信号进行边沿检测处理

reg[:]vsync_d = 'b11;

reg[:]href_d = 'b00;

wire vsync_start;

wire vsync_end;

//vs signal deal with.

always@(posedge cmos_pclk_i)

begin

vsync_d <= {vsync_d[],cmos_vsync_i};

href_d <= {href_d[],cmos_href_i};

end

assign vsync_start = vsync_d[]&(!vsync_d[]); //捕捉vsync信号的下降沿

assign vsync_end = (!vsync_d[])&vsync_d[]; //捕捉vsync信号的上升沿

/*reg[6:0]cmos_fps = 0;

//frame count.

always@(posedge cmos_pclk_i)

begin

if(rst)

begin

cmos_fps <= 7'd0;

end

else if(vsync_start) //每当一场开始的时候,计数器加一,难道是一帧只有一场?

begin

cmos_fps <= cmos_fps + 7'd1;

end

//计数到了CMOS_FRAME_WAITCNT时,就保持这个数值不变(15)

else if(cmos_fps >= CMOS_FRAME_WAITCNT)

begin

cmos_fps <= CMOS_FRAME_WAITCNT;

end

end*/

//在一定区域内,将时钟cmos_pclk_i 进行二分频

reg byte_flag = ;

always@(posedge cmos_pclk_i)

begin

if(rst)

byte_flag <= ;

else if(cmos_href_i) //控制信号,固定区域

byte_flag <= ~byte_flag;

else

byte_flag <= ;

end

//将byte_flag 延时一拍,从仿真图中才可以看出此处的用意

reg byte_flag_r0 = ;

always@(posedge cmos_pclk_i)

begin

if(rst)

byte_flag_r0 <= ;

else

byte_flag_r0 <= byte_flag;

end

//接收摄像头的数据,当href为高电平时,采集数据,当为低电平时,用0填充

reg [:] cmos_data_d0 = ;

always@(posedge cmos_pclk_i)

begin

if(rst)

cmos_data_d0 <= 'd0;

else if(cmos_href_i)

cmos_data_d0 <= cmos_data_i; //MSB -> LSB

else if(~cmos_href_i)

cmos_data_d0 <= 'd0;

end

reg [:] rgb565_o = ;

always@(posedge cmos_pclk_i)

begin

if(rst)

rgb565_o <= 'd0;

//当href为高电平,byte_flag 为高时候,对rgb565数据进行拼装

else if(cmos_href_i & byte_flag)

rgb565_o <= {cmos_data_d0,cmos_data_i}; //MSB -> LSB

else if(~cmos_href_i)

rgb565_o <= 'd0;

end

assign vs_o = vsync_d[];

assign hs_o = href_d[];

assign vid_clk_ce = (byte_flag_r0&hs_o)||(!hs_o);

/*

add_force {/signal_test_1/cmos_pclk_i} -radix hex {1 0ns} {0 50000ps} -repeat_every 100000ps

add_force {/signal_test_1/rst} -radix hex {1 0ns} {0 100ns}

add_force {/signal_test_1/cmos_href_i} -radix hex {0 0ns} {1 500ns} {0 1500ns}

add_force {/signal_test_1/cmos_data_i} -radix hex {0 0ns} {1 500ns} {2 600ns} {3 700ns} {4 800ns} {5 900ns} {6 1000ns}\

{7 1100ns} {8 1200ns} {9 1300ns} {10 1400ns} {0 1500ns}

add_force {/signal_test_1/cmos_vsync_i} -radix hex {1 0ns} {0 300ns} {1 1800ns}

*/

endmodule

源程序与注释:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2018/05/17 13:22:09

// Design Name:

// Module Name: cmos_decode

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

////////////////////////////////////////////////////////////////////////////////// module cmos_decode(

//system signal.

input cmos_clk_i, //cmos senseor clock.

input rst_n_i, //system reset.active low.

//cmos sensor hardware interface.

input cmos_pclk_i, //input pixel clock.

input cmos_href_i, //input pixel hs signal.

input cmos_vsync_i, //input pixel vs signal.

input[:]cmos_data_i, //data.

output cmos_xclk_o, //output clock to cmos sensor.

//user interface.

output hs_o, //hs signal.

output vs_o, //vs signal.

output reg [:] rgb565_o, //data output

output vid_clk_ce

); parameter[:]CMOS_FRAME_WAITCNT = 'd15; //复位信号延时5个时钟周期

reg[:] rst_n_reg = 'd0;

//reset signal deal with.

always@(posedge cmos_clk_i)

begin

rst_n_reg <= {rst_n_reg[:],rst_n_i};

end // 对行场信号进行边沿检测处理

reg[:]vsync_d;

reg[:]href_d;

wire vsync_start;

wire vsync_end;

//vs signal deal with.

always@(posedge cmos_pclk_i)

begin

vsync_d <= {vsync_d[],cmos_vsync_i};

href_d <= {href_d[],cmos_href_i};

end

assign vsync_start = vsync_d[]&(!vsync_d[]); //捕捉vsync信号的下降沿

assign vsync_end = (!vsync_d[])&vsync_d[]; //捕捉vsync信号的上升沿 reg[:]cmos_fps;

//frame count.

always@(posedge cmos_pclk_i)

begin

if(!rst_n_reg[])

begin

cmos_fps <= 'd0;

end else if(vsync_start) //每当一场开始的时候,计数器加一,难道是一帧只有一场?

begin

cmos_fps <= cmos_fps + 'd1;

end //计数到了CMOS_FRAME_WAITCNT时,就保持这个数值不变(15)

else if(cmos_fps >= CMOS_FRAME_WAITCNT)

begin

cmos_fps <= CMOS_FRAME_WAITCNT;

end

end //wait frames and output enable.

reg out_en;

always@(posedge cmos_pclk_i)

begin

if(!rst_n_reg[])

begin

out_en <= 'b0;

end //当计数器达到CMOS_FRAME_WAITCNT(15)时,产生一个使能信号

else if(cmos_fps >= CMOS_FRAME_WAITCNT)

begin

out_en <= 'b1;

end //没有达到条件时候,保持原信号不变

else

begin

out_en <= out_en;

end

end //output data 8bit changed into 16bit in rgb565.

reg [:] cmos_data_d0;

reg [:]cmos_rgb565_d0;

reg byte_flag;

always@(posedge cmos_pclk_i)

begin

if(!rst_n_reg[])

byte_flag <= ; //产生一个标志位,每当href为高 电平时,产生跳变

else if(cmos_href_i)

byte_flag <= ~byte_flag;

else

byte_flag <= ;

end //为什么在这里打一拍

reg byte_flag_r0;

always@(posedge cmos_pclk_i)

begin

if(!rst_n_reg[])

byte_flag_r0 <= ;

else

byte_flag_r0 <= byte_flag;

end //接收摄像头的数据,当href为高电平时,采集数据,当为低电平时,用0填充

always@(posedge cmos_pclk_i)

begin

if(!rst_n_reg[])

cmos_data_d0 <= 'd0; else if(cmos_href_i)

cmos_data_d0 <= cmos_data_i; //MSB -> LSB else if(~cmos_href_i)

cmos_data_d0 <= 'd0;

end //重要的来了

always@(posedge cmos_pclk_i)

begin

if(!rst_n_reg[])

rgb565_o <= 'd0; //当href为高电平,byte_flag 为高时候,对rgb565数据进行拼装

else if(cmos_href_i & byte_flag)

rgb565_o <= {cmos_data_d0,cmos_data_i}; //MSB -> LSB else if(~cmos_href_i)

rgb565_o <= 'd0;

end assign vid_clk_ce = out_en ? (byte_flag_r0&hs_o)||(!hs_o) : 'b0;

assign vs_o = out_en ? vsync_d[] : 'b0;

assign hs_o = out_en ? href_d[] : 'b0;

assign cmos_xclk_o = cmos_clk_i; endmodule

verilog 代码分析与仿真的更多相关文章

- 串口接收端verilog代码分析

串口接收端verilog代码分析 `timescale 1ns / 1ps ////////////////////////////////////////////////////////////// ...

- 串口发送端verilog代码分析

串口发送端verilog代码分析 `timescale 1ns / 1ps ////////////////////////////////////////////////////////////// ...

- VGA设计(原理说明。Verilog代码实现,仿真结果)

各类显示屏的显示原理大部分是利用人眼的视觉暂留效应.比如之前的数码管显示就是设计每个周期内各个小段按顺序显示,来达到显示一个数字的效果. VGA同理,显示屏在显示时是一个像素一个像素地显示,在人眼看来 ...

- 学会使用Hdlbits网页版Verilog代码仿真验证平台

给大家推荐一款网页版的 Verilog代码编辑仿真验证平台,这个平台是国外的一家开源FPGA学习网站,通过“https://hdlbits.01xz.net/wiki/Main_Page” 地址链接进 ...

- Verilog代码规范I

Verilog代码规范I "规范"这问题 "规范"这个富含专业气息的词汇(个人感觉),其实规范这种东西,就是大家都约定熟成的东西,一旦你不遵守这个东西,专业人士 ...

- Xilinx Vivado的使用详细介绍(1):创建工程、编写代码、行为仿真

Xilinx Vivado的使用详细介绍(1):创建工程.编写代码.行为仿真 Author:zhangxianhe 新建工程 打开Vivado软件,直接在欢迎界面点击Create New Projec ...

- STM32F103片外运行代码分析

STM32F103片外运行代码分析 STM32F103有三种启动方式: 1.从片内Flash启动: 2.从片内RAM启动: 3.从片内系统存储器启动,内嵌的自举程序,用于串口IAP. 无法直接在片外N ...

- Verilog代码和FPGA硬件的映射关系(一)

代码和硬件之间的映射关系是一个很奇妙的过程,也展现出人类的智慧.单片机内部的硬件结构都是固定的,无法改变,我们通过代码操作着寄存器的读写,来执行各种复杂的任务.FPGA的硬件结构并不像单片机一样是固定 ...

- Verilog代码和FPGA硬件的映射关系(二)

大家可能会有这样的疑问,我们编写的Verilog代码最终会在FPGA上以怎样的映射关系来实现功能呢?我们以一个最简单的组合逻辑与门为例来向大家说明.RTL代码如下所示: //------------- ...

随机推荐

- 20190318wdVBA_替换下划线

Sub 替换下划线() Selection.HomeKey wdStory Selection.Find.ClearFormatting Selection.Find.Font.Underline = ...

- ActiveRecord Nested Atrributes 关联记录,对嵌套属性进行CURD

设置了Nested attributes后,你可以通过父记录来更新/新建/删除关联记录. 使用: #accepts_nested_attributes_for class method. 例如: cl ...

- redis的发布订阅、持久化存储、redis的主从复制

redis的发布订阅 1. 创建redis配置文件 vim /opt/redis_conf/reids-6379.conf mkdir /data/6379 redis-server redis-6 ...

- 字节顺序标记——BOM,Byte Order Mark

定义 BOM(Byte Order Mark),字节顺序标记,出现在文本文件头部,Unicode编码标准中用于标识文件是采用哪种格式的编码. 介绍 UTF-8 不需要 BOM,尽管 Unico ...

- .net asp 实现json 格式跨域访问 的方法

在<configuration> 配置目录下添加允许跨域的头部信息 //webapi 默认的web.config有配置 //1)删除 下面参数 否者WEB API 会 出现405 错误 没 ...

- html 存放PDF文档

<object classid="clsid:CA8A9780-280D-11CF-A24D-444553540000" width="100%" hei ...

- js parseInt()与Number()区别

说到转换成数字类型,我首先想到的是parseInt()方法,后来接触多了才发现还有一个Number()方法,同样是转换成数字类型,这两种方法有什么不同的呢? 1.parseInt(): pa ...

- vue-新建项目-构建-打包-环境切换

一.新建项目 二.运行 npm install npm run start 三.多环境切换 踩坑后总结的方法.. 首先看到package.json 前面的参数都是命令.比如“start”的意思就是np ...

- Java servlet 实现的简易购物车

首页 2.购买页 3.购物车页 1. 首页代码 发送一个post请求 <!DOCTYPE html><html lang="en"><head> ...

- 1095 解码PAT准考证

PAT 准考证号由 4 部分组成: 第 1 位是级别,即 T 代表顶级:A 代表甲级:B 代表乙级: 第 2~4 位是考场编号,范围从 101 到 999: 第 5~10 位是考试日期,格式为年.月. ...