verilog-产生axis数据流

首先这是产生aixs数据流的代码

`timescale 1ps/1ps `default_nettype none module

axis_switch_0_example_master #(

parameter integer C_MASTER_ID =

)

(

/**************** Stream Signals ****************/

output reg m_axis_tvalid = ,

input wire m_axis_tready,

output wire [-:] m_axis_tdata,

output wire [/-:] m_axis_tkeep,

output reg m_axis_tlast = ,

output wire [-:] m_axis_tuser,

/**************** System Signals ****************/

input wire aclk,

input wire aresetn,

/**************** Done Signal ****************/

output reg done =

); /**************** Local Parameters ****************/

localparam integer P_M_TDATA_BYTES = / ;

localparam integer P_M_TUSER_BYTES = ;

localparam [-:] P_M_PACKET_SIZE = ( - );

localparam [-:] P_M_PACKET_NUM = ;

localparam [-:] P_M_SINGLES_NUM = ;

localparam [-:] P_M_DONE_NUM = ;

localparam integer P_M_NUM_MI_SLOTS = ;

localparam integer P_M_NUM_SI_SLOTS = ;

localparam [P_M_NUM_MI_SLOTS*P_M_NUM_SI_SLOTS-:] P_M_CONNECTIVITY_ARRAY = 'b11;

localparam [*P_M_NUM_SI_SLOTS-:] P_M_NUM_CONNECTED_MI_ARRAY = {'d2};

localparam integer P_M_NUM_CONNECTED_MI = P_M_NUM_CONNECTED_MI_ARRAY[C_MASTER_ID*+:]; /**************** Internal Wires/Regs ****************/

genvar i;

generate

for(i=; i<P_M_TDATA_BYTES; i=i+) begin: tdata_g

reg [-:] tdata_i = 'h00;

end

endgenerate

generate

for(i=; (i<P_M_TUSER_BYTES-); i=i+) begin: tuser_g

reg [-:] tuser_i = 'h00;

end

endgenerate

reg [( - (*(P_M_TUSER_BYTES-)) - ):] tuser_i;

reg [-:] pcnt_i = 'h0000;

reg [-:] tcnt_i = 'h0000;

wire done_i;

wire transfer_i;

wire areset = ~aresetn;

reg [-:] areset_i = 'b00; /**************** Assign Signals ****************/

assign m_axis_tkeep = {P_M_TDATA_BYTES{'b1}};

generate

for(i=; i<P_M_TDATA_BYTES; i=i+) begin: tdata_assign_g

assign m_axis_tdata[*i +: ] = tdata_g[i].tdata_i[:];

end

endgenerate

generate

for(i=; i<P_M_TUSER_BYTES; i=i+) begin: tuser_assign_g

if(i == (P_M_TUSER_BYTES - )) begin: tuser_assign_upper_g

assign m_axis_tuser[- : *i] = tuser_i;

end

else begin: tuser_assign_lower_g

assign m_axis_tuser[*i +: ] = tuser_g[i].tuser_i[:];

end

end

endgenerate

assign transfer_i = m_axis_tready && m_axis_tvalid; generate

if(!P_M_NUM_CONNECTED_MI) begin: unconnected_master_g

assign done_i = 'b1;

end

else begin: connected_master_g

assign done_i = (transfer_i && (pcnt_i == P_M_DONE_NUM - 'b1) && (tcnt_i == P_M_PACKET_SIZE));

end

endgenerate // Register Reset

always @(posedge aclk) begin

areset_i <= {areset_i[], areset};

end //**********************************************

// TDATA

//**********************************************

generate

for(i=; i<P_M_TDATA_BYTES; i=i+) begin: tdata_incr_g

always @(posedge aclk) begin

if(areset) begin

tdata_g[i].tdata_i <= 'h00;

end

else

begin

tdata_g[i].tdata_i <= (transfer_i) ? (tdata_g[i].tdata_i + 'b1) : (tdata_g[i].tdata_i);

end

end

end

endgenerate //**********************************************

// TUSER

//**********************************************

generate

for(i=; (i<P_M_TUSER_BYTES-); i=i+) begin: tuser_incr_g

always @(posedge aclk) begin

if(areset) begin

tuser_g[i].tuser_i <= {( - (*i)){'b1}};

end

else

begin

tuser_g[i].tuser_i <= (transfer_i) ? (tuser_g[i].tuser_i - 'b1) : (tuser_g[i].tuser_i);

end

end

end

endgenerate always @(posedge aclk) begin

if(areset) begin

tuser_i <= {( - (*(P_M_TUSER_BYTES-))){'b1}};

end

else

begin

tuser_i <= (transfer_i) ? (tuser_i - 'b1) : tuser_i;

end

end //**********************************************

// TVALID

//**********************************************

always @(posedge aclk) begin

if(areset) begin

m_axis_tvalid <= 'b0;

end

else

begin

// TVALID

if(done_i) begin

m_axis_tvalid <= 'b0;

end

else if(areset_i == 'b10) begin

m_axis_tvalid <= 'b1;

end

else begin

m_axis_tvalid <= m_axis_tvalid;

end

end

end //**********************************************

// TLAST

//**********************************************

always @(posedge aclk) begin

if(areset) begin

m_axis_tlast <= 'b0;

end

else

begin

// TLAST

if(areset_i == 'b10) begin

m_axis_tlast <= 'b1;

end

else if((pcnt_i >= (P_M_SINGLES_NUM - 'b1)) && transfer_i && m_axis_tlast) begin

m_axis_tlast <= 'b0;

end

else if(tcnt_i == (P_M_PACKET_SIZE - 'b1) && transfer_i) begin

m_axis_tlast <= 'b1;

end

else begin

m_axis_tlast <= m_axis_tlast;

end

end

end //**********************************************

// PCNT, TCNT, DONE

//**********************************************

always @(posedge aclk) begin

if(areset) begin

pcnt_i <= 'h0000;

tcnt_i <= 'h0000;

done <= 'b0;

end

else

begin

// DONE

done <= (done_i) ? 'b1 : done; // Increment counters

tcnt_i <= (transfer_i) ? (m_axis_tlast ? 'h0000 : (tcnt_i + 1'b1)) : tcnt_i;

pcnt_i <= (transfer_i && m_axis_tlast) ? (pcnt_i + 'b1) : pcnt_i;

end

end endmodule `default_nettype wire

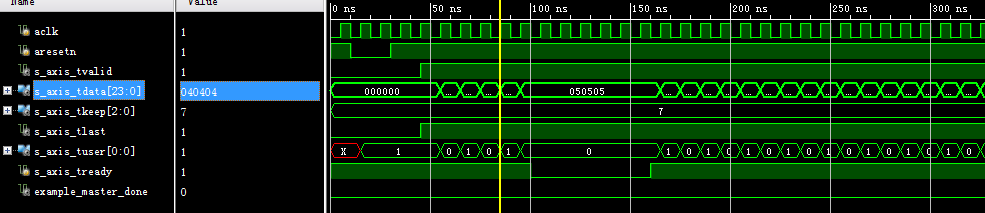

这里是仿真的代码

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2017/08/02 15:17:37

// Design Name:

// Module Name: test_axis_tb

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

////////////////////////////////////////////////////////////////////////////////// module test_axis_tb( ); reg aclk=;

reg aresetn=;

wire s_axis_tvalid;

wire [-:]s_axis_tdata;

wire [/-:] s_axis_tkeep;

wire s_axis_tlast;

wire [-:]s_axis_tuser;

reg s_axis_tready=;

wire example_master_done;

// Example master #0

axis_switch_0_example_master #(

.C_MASTER_ID ( )

) inst_axis_switch_0_example_master_0 (

.aclk ( aclk ),

.aresetn ( aresetn ),

.m_axis_tvalid ( s_axis_tvalid),

.m_axis_tdata ( s_axis_tdata ),

.m_axis_tkeep ( s_axis_tkeep ),

.m_axis_tlast ( s_axis_tlast ),

.m_axis_tuser ( s_axis_tuser),

.m_axis_tready ( s_axis_tready ),

.done ( example_master_done )

);

always # aclk=~aclk;

initial begin

# s_axis_tready=;

# s_axis_tready=;

end

initial begin # aresetn=;

# aresetn=;

end

endmodule

verilog-产生axis数据流的更多相关文章

- axis 数据流

产生数据流的代码 模板 重新修改了下 :]axis_data_cnt='d0; :]axis_data_frame_cnt='d0; :]delay_cnt='d0; initial begin ...

- Verilog的数据流、行为、结构化与RTL级描述

Verilog语言可以有多种方式来描述硬件,同时,使用这些描述方式,又可以在多个抽象层次上设计硬件,这是Verilog语言的重要特征. 在Verilog语言中,有以下3种最基本的描述方式: 数据流描述 ...

- VHDL:信号、端口以及和Verilog的区别

1.信号 信号是描述硬件系统的基本数据对象,它的性质类似于连接线.信号可以作为设计实 体中并行语句模块间的信息交流通道. 信号作为一种数值容器,不但可以容纳当前值,也可以保持历史值(这决定于 ...

- 硬件描述语言Verilog设计经验总结

一.硬件描述语言Verilog 粗略地看Verilog与C语言有许多相似之处.分号用于结束每个语句,注释符也是相同的(/* ... */和// 都是熟悉的),运算符"=="也用来测 ...

- Verilog HDL程序设计——基本要素

Verilog基本上熟悉了,继续整理一下Verilog的学习笔记吧.前面记载了Verilog的结构,写Verilog的结构有了,但是该怎么写呢?在写之前就得了解一下Verilog的一些基本要素了,也就 ...

- verilog 介绍

Verilog HDL Verilog HDL是在C语言的基础上发展起来的一种硬件描述语言,语法较自由.VHDL和Verilog HDL两者相比,VHDL的书写规则比Verilog HDL烦琐一些,但 ...

- 【接口时序】3、UART串口收发的原理与Verilog实现

一.软件平台与硬件平台 软件平台: 1.操作系统:Windows-8.1 2.开发套件:ISE14.7 3.仿真工具:ModelSim-10.4-SE 硬件平台: 1.FPGA型号:XC6SLX45- ...

- FIR滤波原理及verilog设计

FIR(Finite Impulse Response)Filter:有限冲激响应滤波器,又称为非递归线性滤波器. FIR滤波器的冲击响应是一个值为滤波器抽头系数的采样序列,其脉冲响应由有限个采样值构 ...

- 关于Verilog中的几种赋值语句

1. 连续赋值语句(Continuous Assignments) 连续赋值语句是Verilog数据流建模的基本语句,用于对线网进行赋值,等价于门级描述,是从更高的抽象角度来对电路进行描述.连续赋值语 ...

随机推荐

- JQuery-change/select/submit

<!DOCTYPE html> <html lang="en"> <head> <meta charset="UTF-8&quo ...

- day 9 - 2 函数练习

1.写函数,检查获取传入列表或元组对象的所有奇数位索引对应的元素,并将其作为新列表返回给调用者. def func(lis): print(lis[1::2]) #取偶数 return lis[::2 ...

- 算法-链的操作(一)-合并两个排序的链接(no.25)

合并两个排序的链接(no.25) 把下面连个排好序的链,从小到大排序链接. list1 : 1 -> 6 -> 8 list2 : 2-> 5 -> 9 def merge(h ...

- #6284. 数列分块入门 8(区间询问等于一个数 cc 的元素,并将这个区间的所有元素改为 c)

题目链接:https://loj.ac/problem/6284 题目大意:中文题目 具体思路:还是和sqrt那个题的思路相同的,标记每一块的值是不是相同的,注意lazy下标的下放. AC代码: #i ...

- 小玩意--自定义log记录

之前在帮TCL运维项目时,因某些原因,决定单就经销商相关业务中摒弃经典的log4j日志,改为每日自定义生成并写入相关日志,我遂写了一个util,代码如下:p.s.实现的思路很简单,仅为每次需要记录时, ...

- Javascript - ExtJs - 常用方法和属性

常用方法和属性(Common methods and attributes) ExtJs中的对象 Ext.Component Ext组件对象,表示一个可渲染的组件. Ext.dom.Element E ...

- ASP.NET MVC - WEB API

ASP.NET WEB API 与WEB API有关的类型 HttpMessageHandler(System.Net.Http)(消息处理器) 表示Http请求的处理程序,处理程序类似于Http管道 ...

- Zookeeper学习笔记1

参考:从Paxos到Zookeeper分布式一致性原理与实践 从ACID到CAP/BASE ACID 事务(Transaction),一般是指要做的或所做的事情.在计算机术语中是指访问并可能更新数据库 ...

- 在Apache Struts中利用OGNL注入

前言 本文简要介绍了Apache Struts的OGNL注入缺陷,文章中介绍使用简单的应用程序复现OGNL注入.深入研究针对公共漏洞,并理解这类漏洞. 内容 安装Apache Tomcat服务器(入门 ...

- Yara VS2017出现LINK : fatal error LNK1104: 无法打开文件“msvcrt.lib”

解决方法1 搜索msvcrt.lib所在的路径 C:\Program Files (x86)\Microsoft Visual Studio\2017\Professional\VC\Tools\MS ...