双口RAM,值得研究

在FPGA设计过程中,使用好双口RAM,也是提高效率的一种方法。

官方将双口RAM分为简单双口RAM和真双口RAM。

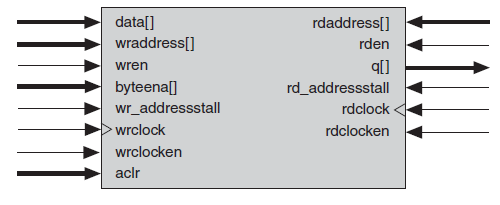

简单双口RAM只有一个写端口,一个读端口。

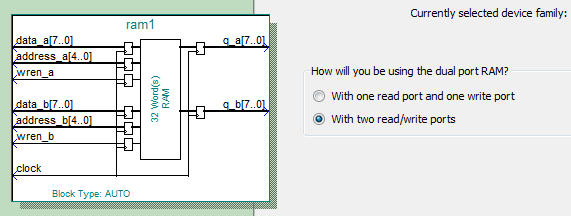

真双口RAM分别有两个写端口和两个读端口。

无论是简单双口RAM还是真双口RAM,在没有读操作的情况下,应将读使能rden信号拉成低电平,节省功耗。

在两种情况下,都应当避免read-during-write,虽然可在软件中进行设置,但是,作为设计者,应当尽量避免此种情况。

对于真双口RAM,还应当避免两个读端口或者两个写端口同时操作同一个地址,RAM中并没有此种冲突解决电路,设计者应该避免这种冲突。

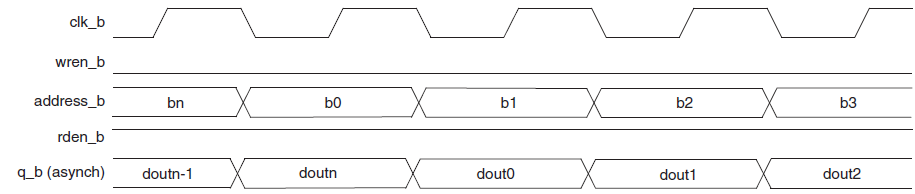

无论是那种双口RAM,读时序图是相同的。

当读使能有效时,数据会在时钟下一个上升沿从Q端输出。

真双口RAM给设计带来很多便利。在高速存储中,需要对连续的数据同时处理,使用简单双口RAM只能读取一个数据,而使用真双口RAM可以同时读取两个数据,这样明显提高读取速度以及处理速度。

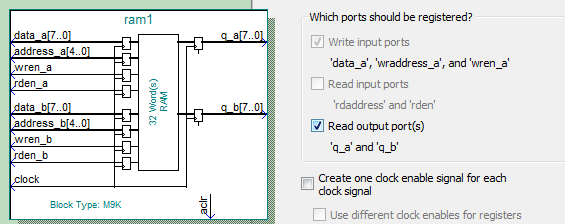

调用真双口RAM,如图设置。

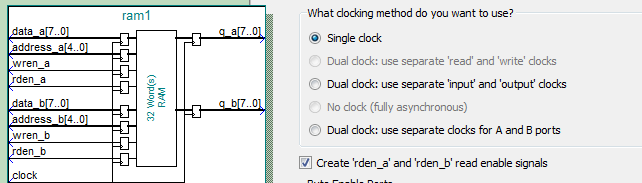

这里可以设置时钟方案,而读使能rden并非必须信号。当使用rden信号时,此信号高电平有效,当不使用rden信号时,给定地址,下一个脉冲数据从q端口送出。

这里的设置非常重要,当选中read output ports时,q端会增加一级寄存器。虽然这样增加流水线能够提高电路的速度,但同时从读使能有效到最终数据有效将会多延迟一个时钟周期。在设计中要格外注意。根据设计自行设置。

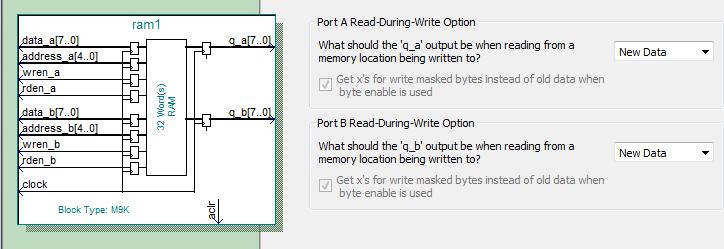

上面两张图是指定对同一地址操作时的输出。作为设计者,应尽量在自己的设计中避免这种情况发生。

真双口RAM用好了是非常省时间的。之前我们文章中提到硬件FFT的实现,在实现过程中,使用基2的设计方案,需要同时读取两个RAM数据,这种情况下可以使用真双口RAM提高效率。

版权所有权归卿萃科技 杭州FPGA事业部,转载请注明出处

作者:杭州卿萃科技ALIFPGA

原文地址:杭州卿萃科技FPGA极客空间 微信公众号

扫描二维码关注杭州卿萃科技FPGA极客空间

双口RAM,值得研究的更多相关文章

- 【iCore1S 双核心板_FPGA】例程十七:基于双口RAM的ARM+FPGA数据存取实验

实验现象: 核心代码: module DUAL_PORT_RAM( input CLK_12M, inout WR, input RD, input CS0, :]A, :]DB, output FP ...

- 用嵌入式块RAM IP核配置一个双口RAM

本次设计源码地址:http://download.csdn.net/detail/noticeable/9914173 实验现象:通过串口将数据发送到FPGA 中,通过quartus II 提供的in ...

- 单口 RAM、伪双口 RAM、真双口 RAM、单口 ROM、双口 ROM 到底有什么区别呢?

打开 IP Catalog,搜索 Block Memory Generator,即可看到其 Memory Type 可分为 5 中,分别是单口 RAM(Single Port RAM).伪双口 RAM ...

- FMC与FPGA双口ram通讯

硬件环境:ARM+FPGA通过FMC互联,STM32F767和 EP4CE15F23I7 FMC设置,STM的系统时钟HCLK为216MHz /* FMC initialization functio ...

- 单口RAM、双口RAM、FIFO

单口与双口的区别在于,单口只有一组数据线与地址线,因此读写不能同时进行.而双口有两组数据线与地址线,读写可同时进行.FIFO读写可同时进行,可以看作是双口. 双口RAM分伪双口RAM(Xilin ...

- 【iCore4 双核心板_FPGA】例程十六:基于双口RAM的ARM+FPGA数据存取实验

实验现象: 核心代码: int main(void) { /* USER CODE BEGIN 1 */ int i; int address,data; ; ]; ]; char *p; /* US ...

- 单双口RAM

// Quartus II Verilog Template// Simple Dual Port RAM with separate read/write addresses and// singl ...

- 【知识强化】第三章 存储系统 3.5 双口RAM和多模块存储器

下面我们进入双端口RAM和多模块存储器的学习.这是提高我们的存储器的访存速度的一些措施. 我们之前已经讲过我们的主存和CPU是进行连接的,那么这就导致了一个问题就是说,随着我们现代科技的发展,计算机的 ...

- 【iCore3 双核心板_FPGA】实验十九:基于双口RAM的ARM+FPGA数据存取实验

实验指导书及代码包下载: http://pan.baidu.com/s/1pLReIc7 iCore3 购买链接: https://item.taobao.com/item.htm?id=524229 ...

随机推荐

- JS中call和apply区别有哪些 记录

一.call和apply区别 传递参数的方式.用法上不同,主要是参数不完全同 (1).B.Function.call(A,arg,arg) 这个例子是讲A对象“调用”B对象的Function(某个具体 ...

- Spring入门1. IoC入门实例

Spring入门1. IoC入门实例 Reference:Java EE轻量级解决方案——S2SH 前言: 之前学习过关于Spring的一点知识,曾经因为配置出现问题,而总是被迫放弃学习这些框架技术, ...

- 关于vue+element-ui的table多选禁用某个按钮

在我做的项目中,有这样一个需求:当table多选没有勾选数据的时候禁用掉导出按钮 效果如图: 当选择一个时候可以导出这行的数据 在按钮定义 :disabled="selected ...

- wget 认知及常用命令【转载】

https://www.cnblogs.com/lxz88/p/6278268.html https://www.cnblogs.com/cindy-cindy/p/6847502.html

- 《Effective C++》第4章 设计与声明(1)-读书笔记

章节回顾: <Effective C++>第1章 让自己习惯C++-读书笔记 <Effective C++>第2章 构造/析构/赋值运算(1)-读书笔记 <Effecti ...

- 使用 create-react-app 构建 react应用程序

原文 http://blog.csdn.net/github_squad/article/details/57452333#

- selected多次点击不生效

表单下拉选项使用selected设置选中时,发现第一次默认选中成功,在页面不刷新的情况下操作(比如ajax),虽然selected属性设置了,但是默认选中不生效. 解决办法1 可能是浏览器缓存问题,在 ...

- React-Native进阶_5.导航 Naviagtion

有这样一个组件 他可以控制页面跳转 返回,在移动端叫做导航控制器, 在RN中叫路由 我们使用的 react-native-navigation 是一个开源组件库介绍:A complete nativ ...

- 神奇的 ViewDragHelper,让你轻松定制拥有拖拽能力的 ViewGroup

为了吸引大家的注意力,先给大家看一张动图: 相信这种效果大家都见过吧?我第一次见到这样的效果时,心里也痒痒的,急于想实现这种功能,后来因为拖延症的问题,就一直没有去弄这件事.现在这段时间,工作比较轻闲 ...

- Objective C - 2 - 随机数,可变字符串,字符串,SubString

int main(int argc, const char * argv[]) { @autoreleasepool { NSString *outputString = @"1234567 ...