内存,寄存器和cache的区别与联系

1. 寄存器是中央处理器内的组成部份。寄存器是有限存贮容量的高速存贮部件,它们可用来暂存指令、数据和位址。在中央处理器的控制部件中,包含的寄存器有指令寄存器(IR)和程序计数器(PC)。在中央处理器的算术及逻辑部件中,包含的寄存器有累加器(ACC)。

2. 内存包含的范围非常广,一般分为只读存储器(ROM)、随机存储器(RAM)和高速缓存存储器(cache)。

3. 寄存器是CPU内部的元件,寄存器拥有非常高的读写速度,所以在寄存器之间的数据传送非常快。

4. Cache :即高速缓冲存储器,是位于CPU与主内存间的一种容量较小但速度很高的存储器。由于CPU的速度远高于主内存,CPU直接从内存中存取数据要等待一定时间周期,Cache中保存着CPU刚用过或循环使用的一部分数据,当CPU再次使用该部分数据时可从Cache中直接调用,这样就减少了CPU的等待时间,提高了系统的效率。Cache又分为一级Cache(L1 Cache)和二级Cache(L2 Cache),L1 Cache集成在CPU内部,L2 Cache早期一般是焊在主板上,现在也都集成在CPU内部,常见的容量有256KB或512KB L2 Cache。

总结:大致来说数据是通过内存-Cache-寄存器,Cache缓存则是为了弥补CPU与内存之间运算速度的差异而设置的的部件。

http://blog.csdn.net/csuyishuan/article/details/52073421

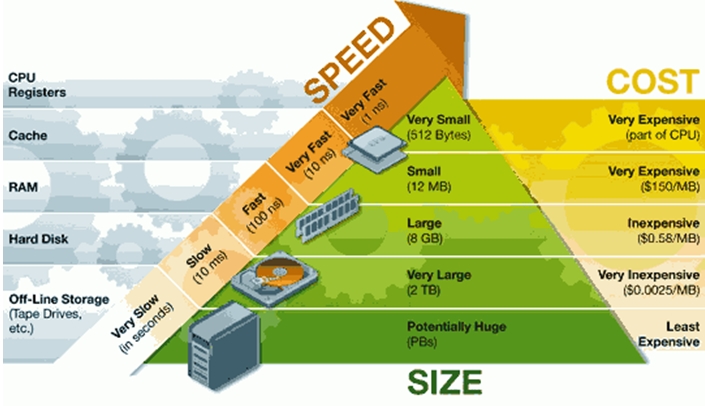

首先看一下计算机的存储体系(Memory hierarchy)金字塔

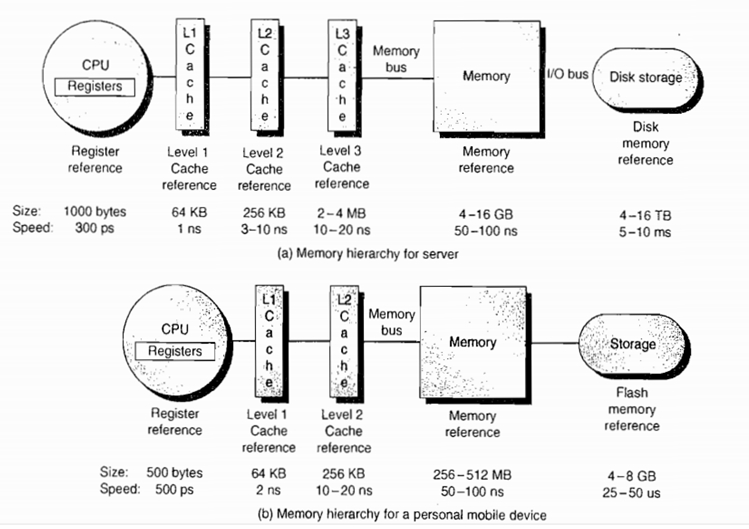

其次我们看看一个计算机的存储体系

Register

寄存器是CPU的内部组成单元,是CPU运算时取指令和数据的地方,速度很快,寄存器可以用来暂存指令、数据和地址。在CPU中,通常有通用寄存器,如指令寄存器IR;特殊功能寄存器,如程序计数器PC、sp等。

Cache

缓存即就是用于暂时存放内存中的数据,若果寄存器要取内存中的一部分数据时,可直接从缓存中取到,这样可以调高速度。高速缓存是内存的部分拷贝。

CPU <--- > 寄存器<--- > 缓存<--- >内存

寄存器的工作方式很简单,只有两步:(1)找到相关的位,(2)读取这些位。

内存的工作方式就要复杂得多:

(1)找到数据的指针。(指针可能存放在寄存器内,所以这一步就已经包括寄存器的全部工作了。)

(2)将指针送往内存管理单元(MMU),由MMU将虚拟的内存地址翻译成实际的物理地址。

(3)将物理地址送往内存控制器(memory controller),由内存控制器找出该地址在哪一根内存插槽(bank)上。

(4)确定数据在哪一个内存块(chunk)上,从该块读取数据。

(5)数据先送回内存控制器,再送回CPU,然后开始使用。

内存的工作流程比寄存器多出许多步。每一步都会产生延迟,累积起来就使得内存比寄存器慢得多。

为了缓解寄存器与内存之间的巨大速度差异,硬件设计师做出了许多努力,包括在CPU内部设置缓存、优化CPU工作方式,尽量一次性从内存读取指令所要用到的全部数据等等。

RAM-memory

即内存,是用于存放数据的单元。其作用是用于暂时存放CPU中的运算数据,以及与硬盘等外部存储器交换的数据。

HardDisk

硬盘

作者:时国怀

链接:http://www.zhihu.com/question/20075426/answer/16354329

来源:知乎

著作权归作者所有,转载请联系作者获得授权。

一条汇编指令大概执行过程是(不是绝对的,不同平台有差异):

取指(取指令)、译码(把指令转换成微指令)、取数(读内存里的操作数)、计算(各种计算的过程,ALU负责)、写回(将计算结果写回内存),有些平台里,前两步会合并成一步,某些指令也不会有取数或者回写的过程。

再提一下CPU主频的概念:首先,主频绝对不等于一秒钟可以执行的指令个数,每个指令的执行成本是不同的,比如x86平台里汇编指令INC就比ADD要快,具体每个指令的时钟周期可以参考intel的手册。

为什么要提主频?因为上面的执行过程中,每个操作都需要占用一个时钟周期,对于一个操作内存的加法,就需要5个时钟周期,换句话说,500Mhz主频的CPU,最多执行100MHz条指令。

仔细观察,上面的步骤里不包括寄存器操作,对于CPU来说读/写寄存器是不需要时间的,或者说如果只是操作寄存器(比如类似mov BX,AX之类的操作),那么一秒钟执行的指令个数理论上说就等于主频,因为寄存器是CPU的一部分。

然后寄存器往下就是各级的cache,有L1 cache,L2,甚至有L3的,以及TLB这些(TLB也可以认为是cache),之后就是内存,前面说寄存器快,现在说为什么这些慢:

对于各级的cache,访问速度是不同的,理论上说L1cache(一级缓存)有着跟CPU寄存器相同的速度,但L1cache有一个问题,当需要同步cache和内存之间的内容时,需要锁住cache的某一块(术语是cache line),然后再进行cache或者内存内容的更新,这段期间这个cache块是不能被访问的,所以L1cache的速度就没寄存器快,因为它会频繁的有一段时间不可用。

L1 cache下面是L2 cache,甚至L3 cache,这些都有跟L1 cache一样的问题,要加锁,同步,并且L2比L1慢,L3比L2慢,这样速度也就更低了。

最后说说内存,内存的主频现在主流是1333左右吧?或者1600,单位是MHz,这比CPU的速度要低的多,所以内存的速度起点就更低,然后内存跟CPU之间通信也不是想要什么就要什么的。

内存不仅仅要跟CPU通信,还要通过DMA控制器与其它硬件通信,CPU要发起一次内存请求,先要给一个信号说“我要访问数据了,你忙不忙?”如果此时内存忙,则通信需要等待,不忙的时候,通信才能正常。并且,这个请求信号的时间代价,就是够执行几个汇编指令了,所以,这是内存慢的一个原因。

另一个原因是:内存跟CPU之间通信的通道也是有限的,就是所谓的“总线带宽”,但,要记住这个带宽不仅仅是留给内存的,还包括显存之类的各种通信都要走这条路,并且由于路是共享的,所以任何请求发起之间都要先抢占,抢占带宽需要时间,带宽不够等待的话也需要时间。

以上两条加起来导致了CPU访问内存更慢,比cache还慢。

举个更容易懂的例子:

CPU要取寄存器AX的值,只需要一步:把AX给我拿来,AX就拿来了。

CPU要取L1 cache的某个值,需要1-3步(或者更多):把某某cache行锁住,把某个数据拿来,解锁,如果没锁住就慢了。

CPU要取L2 cache的某个值,先要到L1 cache里取,L1说,我没有,在L2里,L2开始加锁,加锁以后,把L2里的数据复制到L1,再执行读L1的过程,上面的3步,再解锁。

CPU取L3 cache的也是一样,只不过先由L3复制到L2,从L2复制到L1,从L1到CPU。

CPU取内存则最复杂:通知内存控制器占用总线带宽,通知内存加锁,发起内存读请求,等待回应,回应数据保存到L3(如果没有就到L2),再从L3/2到L1,再从L1到CPU,之后解除总线锁定。

磁盘缓存和内存缓存的区别

内存缓存

高速缓存(英语:cache,英语发音:/kæʃ/ kash [1][2][3],简称缓存),其原始意义是指访问速度比一般随机存取存储器(RAM)快的一种RAM,通常它不像系统主存那样使用DRAM技术,而使用昂贵但较快速的SRAM技术。

原理

Cache一词来源于1967年的一篇电子工程期刊论文。其作者将法语词“cache”赋予“safekeeping storage”的涵义,用于电脑工程领域。

当CPU处理数据时,它会先到Cache中去寻找,如果数据因之前的操作已经读取而被暂存其中,就不需要再从随机存取存储器(Main memory)中读取数据——由于CPU的运行速度一般比主内存的读取速度快,主存储器周期(访问主存储器所需要的时间)为数个时钟周期。因此若要访问主内存的话,就必须等待数个CPU周期从而造成浪费。

提供“缓存”的目的是为了让数据访问的速度适应CPU的处理速度,其基于的原理是内存中“程序执行与数据访问的局域性行为”,即一定程序执行时间和空间内,被访问的代码集中于一部分。为了充分发挥缓存的作用,不仅依靠“暂存刚刚访问过的数据”,还要使用硬件实现的指令预测与数据预取技术——尽可能把将要使用的数据预先从内存中取到缓存里。

CPU的缓存曾经是用在超级计算机上的一种高级技术,不过现今电脑上使用的的AMD或Intel微处理器都在芯片内部集成了大小不等的数据缓存和指令缓存,通称为L1缓存(L1 Cache即Level 1 On-die Cache,第一级片上高速缓冲存储器);而比L1更大容量的L2缓存曾经被放在CPU外部(主板或者CPU接口卡上),但是现在已经成为CPU内部的标准组件;更昂贵的CPU会配备比L2缓存还要大的L3缓存(level 3 On-die Cache第三级高速缓冲存储器)。

概念的扩充

如今缓存的概念已被扩充,不仅在CPU和主内存之间有Cache,而且在内存和硬盘之间也有Cache(磁盘缓存),乃至在硬盘与网络之间也有某种意义上的Cache──称为Internet临时文件夹或网络内容缓存等。凡是位于速度相差较大的两种硬件之间,用于协调两者数据传输速度差异的结构,均可称之为Cache。

地址镜像与变换

主条目:CPU缓存#组相联

由于主存容量远大于CPU缓存的容量,因此两者之间就必须按一定的规则对应起来。地址镜像就是指按某种规则把主存块装入缓存中。地址变换是指当按某种镜像方式把主存块装入缓存后,每次访问CPU缓存时,如何把主存的物理地址(Physical address)或虚拟地址(Virtual address)变换成CPU缓存的地址,从而访问其中的数据。

缓存置换策略

主条目:CPU缓存#置换策略、分页和缓存文件置换机制

主存容量远大于CPU缓存,磁盘容量远大于主存,因此无论是哪一层次的缓存都面临一个同样的问题:当容量有限的缓存的空闲空间全部用完后,又有新的内容需要添加进缓存时,如何挑选并舍弃原有的部分内容,从而腾出空间放入这些新的内容。解决这个问题的算法有几种,如最久未使用算法(LRU)、先进先出算法(FIFO)、最近最少使用算法(LFU)、非最近使用算法(NMRU)等,这些算法在不同层次的缓存上执行时拥有不同的效率和代价,需根据具体场合选择最合适的一种。

磁盘缓存

磁盘缓存

16MB缓冲区的硬盘

磁盘缓存(Disk Buffer)或磁盘快取(Disk Cache)实际上是将下载到的数据先保存于系统为软件分配的内存空间中(这个内存空间被称之为“内存池”),当保存到内存池中的数据达到一个程度时,便将数据保存到硬盘中。这样可以减少实际的磁盘操作,有效的保护磁盘免于重复的读写操作而导致的损坏。

磁盘缓存是为了减少CPU透过I/O读取磁盘机的次数,提升磁盘I/O的效率,用一块内存来储存存取较频繁的磁盘内容;因为内存的存取是电子动作,而磁盘的存取是I/O动作,感觉上磁盘I/O变得较为快速。

相同的技巧可用在写入动作,我们先将欲写入的内容放入内存中,等到系统有其它空闲的时间,再将这块内存的资料写入磁盘中。

大小

现在的磁盘通常有32MB或64MB缓存。旧的硬盘则有8MB或16MB。

内存,寄存器和cache的区别与联系的更多相关文章

- Linux操作系统中内存buffer和cache的区别--从free命令说起(转)

原文链接:http://os.51cto.com/art/200709/56603.htm 我们一开始,先从Free命令说起. Free free 命令相对于top 提供了更简洁的查看系统内存使用情况 ...

- Linux内存管理机制中buffer和cache的区别

Linux内存管理机制中buffer和cache的区别理解linux内存管理,需要深入了解linux内存的各个参数含义和规则,下面介绍一下Linux操作系统中内存buffer和cache的区别. Fr ...

- Linux 内存buffer与cache区别_003

一.首先大概了解一下计算机CPU.Cache.Buffer.内存.硬盘.SWAP CPU也称为中央处理器(CPU,Central Processing Unit)是一块超大规模的集成电路,是一台计算机 ...

- linux的top下buffer与cache的区别、free命令内存解释

buffer: 缓冲区,一个用于存储速度不同步的设备或优先级不同的设备之间传输数据 的区域.通过缓冲区,可以使进程之间的相互等待变少,从而使从速度慢的设备读入数据 时,速度快的设备的操作进程不发 ...

- Buffer和Cache的区别

- Linux Free命令各数字含义及Buffer和Cache的区别

Linux Free命令各数字含义及Buffer和Cache的区别 Free 命令的各数字含义 命令演示 [root@vm1 ~]# free total used free shared buffe ...

- linux free命令中buffer与cache的区别

linux free命令中buffer与cache的区别 2012-05-15 个评论 收藏 我要投稿 linux free命令中buffer与cache的区别 ~$ ...

- free命令、buffer与cache的区别

freefree 命令相对于top 提供了更简洁的查看系统内存使用情况: # free total used free shared buffers cached Mem: 255988 231704 ...

- Linux内存中的Cache真的能被回收么?

在Linux系统中,我们经常用free命令来查看系统内存的使用状态.在一个RHEL6的系统上,free命令的显示内容大概是这样一个状态: [root@tencent64 ~]# free ...

随机推荐

- 关闭WPS屏保

WPS作为国产的Office,可谓是越来越流氓,无缘无故给你弄个屏保,不好好做Office就知道如何圈钱,或许这就是国内IT行业和国外的差距吧. 我用的WPS内部版本是:10.1.0.7311 如何查 ...

- QT笔记 -- (4) 为QLabel添加鼠标响应方法2

1.实现 bool eventFilter(QObject *target,QEvent *event) 函数内容如下: bool eventFilter(QObject *target,QEvent ...

- ARC下dealloc过程及.cxx_destruct的探究

我是前言 这次探索源自于自己一直以来对ARC的一个疑问,在MRC时代,经常写下面的代码: - (void)dealloc { self.array = nil; self.string = nil; ...

- JSON string 在内存中转流 MemoryStream 代码,以及需要注意的问题utf-8问题

MemoryStream ms = new MemoryStream(System.Text.Encoding.UTF8.GetBytes("字符串"); string str = ...

- Vim常用命令及配置方案

Vim常用命令及配置方案 几句话 很久之前就接触到vim,初学那阵觉得vim很酷炫,但确实对新手不是很友好.我也就简单看了下基本操作就上手了,但又不是长期在vim下工作,这就导致了每一次重新使用v ...

- MyBatis中抽象方法中多个参数的问题

在使用MyBatis时,接口中的抽象方法只允许有1个参数,如果有多个参数,例如: Integer updatePassword( Integer id, String ...

- 获取mapper

static UpdateLogMapper updateLogMapper = (UpdateLogMapper)SpringContextUtil.getBean(UpdateLogMapper. ...

- django 开发之给admin 模块添加富文本编辑器

第一步下载kindeditor http://kindeditor.net/demo.php 下载下来后放到静态文件static 下面的js下面 接着在admin 模块文章类下引入这富文本编辑器: ...

- 题解 洛谷 P3376 【【模板】网络最大流】

本人很弱,只会Dinic.EK与Ford-Fulkerson...(正在学习ISAP...) 这里讲Dinic... Dinic:与Ford-Fulkerson和的思路相似(话说好像最大流求解都差不多 ...

- 【BZOJ 1483】[HNOI2009]梦幻布丁

[链接] 我是链接,点我呀:) [题意] 在这里输入题意 [题解] 链表,启发式合并. 把x变成y,和y全都变成x. 不论是前者还是后者.连续段的个数都是相同的,不影响结果. 那么我们把x,y中出现次 ...