IP核引发的关于定,浮点数的认识

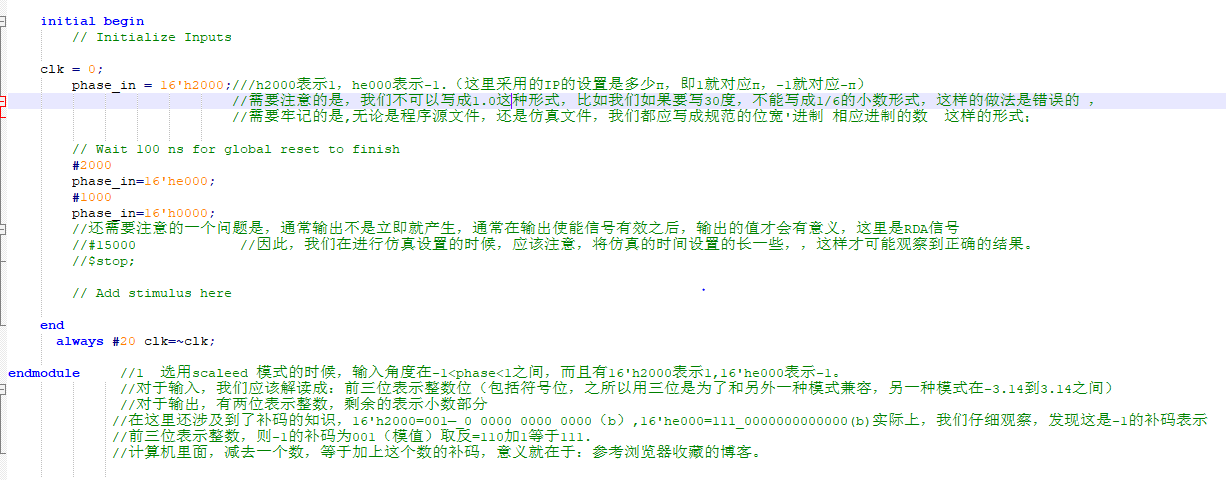

上面是一段关于CORDIC_IP测试文件,用于计算给定角度的sin值和cos值,关于数值表示规则在此不再重复,仅仅说明以下3点:

1 数采用原码,反码,补码,本身并没有正确与否之分(这一点很重要,我们不能认为只有补码的表示是正确的),有的只是适用场合,采用补码的方式能够使得使得加法和减法变得统一,而采用原码自然也有它的好处。

2 在编写Verilog文件时,不管是源文件,还是测试文件,出现小数是一种错误的做法(准确的说直接将小数作为输入输出信号或者中间变量,或者作为测试信号)都是不正确的。永远需要记住的是,数的表示永远是 :位宽+'进制+相应进制下的数。这才是开发环境 以及FPGA本身所允许的数据格式。(否则会出现不太满意的数据)。

3 2说明了我们对于想要处理的小数,通常要通过某种规则转化成符合数表示方式的数,有定点表示和浮点表示两种方法,在FPGA中,更多的是定点数,因此更多的采用定点的转换方法。需要额外注意的是,这一步转换,需要我们自己完成,而不能够通过开发环境完成!

下面通过乘法器IP核进一步直观阐述上述3 :

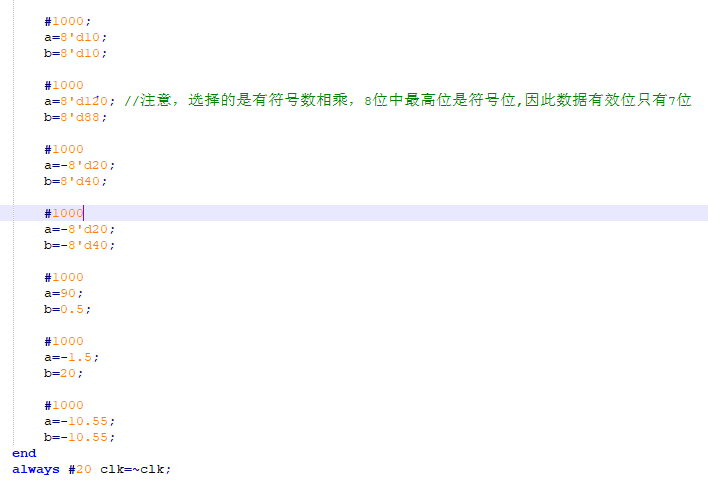

上述图是乘法器IP核的验证代码,其中a和b作为输入,p作为输出.从图中看出来,本人想通过赋值小数给测试信号输入端,来验证小数相乘(其实已经违背了数据的表示格式),观察输出波形如下:

观察上图,发现,对于符号数(带符号整数)的计算是正确的,但是发现输入的小数被近似成了整数,实际上这并不是我们希望得到的,我们想要得到的是小数的结果(需要注意的是,尽管这里显示的是十进制,但也只能显示整数,不能显示小数),而且计算结果也不对。

这提示我们:当面临小数输入(不管是仿真,还是实际中需要把数据输入到模块中去),必须要通过某种手段将这些小数转化成整数,进行乘法计算,再通过某种手段将结果变成我们要的小数(虽然我们不能直观的在波形上看出来)。但是在实际的数据处理中要求我们要这儿做,而这种方式就是:小数定点化(再次强调FPGA中定点数使用的更多)

同时也额外的得到这样的信息:FPGA中乘法器的IP核是定点的,而不是浮点的。

关于对数本身的理解:

在计算机中,并没有类似于,整数,小数,正数,负数这些概念.实际上也并不存在诸如,反码,补码,这些概念。唯一有一个概念就是计数器。计数器反应了数的本质。

对于有符号数,应该有这样一个认识:比如4位计数器,当我们记到0111也就是7的时候,再加1变成了1000,也就是-8,即最大的正数加1变成了最小的负数,同样的,最小的负数减一变成了最大的正数,这个概念我们一定要十分的明确,在我们进行计数的时候,这一点要尤其明确!!!!!1关键在于计数本身就是一个轮回的概念!!!!!这也反应了计算机对于数理解的本质!!!

IP核引发的关于定,浮点数的认识的更多相关文章

- 7 Series GTP IP核使用总结 IP核配置篇

FPGA内嵌收发器相当于以太网中的PHY芯片,但更灵活更高效,线速率也在随着FPGA芯片的发展升级.本文对7系列FPGA内部高速收发器GTP IP核的配置和使用做些简单的总结,以备后续回顾重用.本文是 ...

- xilinx IP核配置,一步一步验证Xilinx Serdes GTX最高8.0Gbps

版权声明:本文为博主原创文章,未经博主允许不得转载. https://blog.csdn.net/u010161493/article/details/77658599 目录(?)[+] 之前 ...

- 基于Virtext6平台的GTX IP核基本设置说明

本工程基于以下条件使用: 板卡:DBF板v3.0 芯片型号:Virtex6 315T ISE版本:14.7 IP核版本: v6_gtxwizard : 1.12 一.IP核配置进行流程 第一页配置:线 ...

- 使用FDATOOL生成xilinx中FIR滤波器IP核的系数

1.在MATLAB命令窗口输入fdatool后回车,打开“Filter Designer & Analysis Tool”工具界面: 2.点击左下角的Set quantization para ...

- 调用altera IP核的仿真流程—下

调用altera IP核的仿真流程—下 编译 在 WorkSpace 窗口的 counter_tst.v上点击右键,如果选择Compile selected 则编译选中的文件,Compile All是 ...

- 调用altera IP核的仿真流程—上

调用altera IP核的仿真流程—上 在学习本节内容之后,请详细阅读<基于modelsim-SE的简单仿真流程>,因为本节是基于<基于modelsim-SE的简单仿真流程>的 ...

- (转)modelsim10.0C编译ISE14.7的xilinx库(xilinx ip核)

原地址modelsim10.0C编译ISE14.7的xilinx库(xilinx ip核) 1.打开D:\Xilinx\14.7\ISE_DS\ISE\bin\nt64\compxlibgui.e ...

- Lattice 的 DDR IP核使用调试笔记之DDR 的 仿真

—— 远航路上ing 整理于 博客园.转载请标明出处. 在上节建立完工程之后,要想明确DDR IP的使用细节,最好是做仿真.然后参考仿真来控制IP 核. 仿真的建立: 1.在IP核内的以下路径找到以下 ...

- Lattice 的 DDR IP核使用调试笔记之工程建立

DDR3的IP核的使用相当重要,尤其是对视频处理方面. 下面接收DDR3 的IP 核的生成步骤. 1. 选择DDR IP核的生成路径.名字以及哪种语言之后就可以设置DDR IP 的参数了. 2.选择存 ...

随机推荐

- 爬虫入门实例:利用requests库爬取笔趣小说网

w3cschool上的来练练手,爬取笔趣看小说http://www.biqukan.com/, 爬取<凡人修仙传仙界篇>的所有章节 1.利用requests访问目标网址,使用了get方法 ...

- C#从http上拿返回JSON数据

C#如何拿到从http上返回JSON数据? 第一章:C#如何拿到从http上返回JSON数据? 第二章:C#如何解析JSON数据?(反序列化对象) 第三章:C#如何生成JSON字符串?(序列化对象) ...

- Elixir 单元测试

概述 elixir 中自带了单元测试框架 ExUnit ,其中提供单元测试的一系列,主要包含以下模块: ExUnit: 单元测试框架 ExUnit.Assertions: 断言 ExUnit.Case ...

- CISCO 动态路由(RIP)

RIP(路由信息协议):是一种内部网关协议(IGP),是一种动态路由选择协议,基于距离矢量算法(DistanceVectorAlgorithms),使用“跳数”(即metric)来衡量到达目标地址的路 ...

- Word中的通配符随意组合进行批量替换或删除某些内容

长文档需要批量修改或删除某些内容的时候,我们可以利用Word中的通配符来搞定这一切,当然,前提是你必须会使用它.通配符的功能非常强大,能够随意组合替换或删除我们定义的规则内容,下面易老师就分享一些关于 ...

- 百度云资源下载加速软件推荐:proxyee-down

百度云是个好东西(现在叫百度网盘不过我还是习惯叫百度云),2个T的免费容量可以存视频.软件包等各式文件,就是下载速度有点让人看不下去,不开会员的话就算你是百兆光纤还是量子通信都是被限速的,做为一个商业 ...

- Linux /var/log下的各种日志文件详解

1)/var/log/secure:记录登录系统存取数据的文件;例如:pop3,ssh,telnet,ftp等都会记录在此. 2)/var/log/wtmp:记录登录这的信息记录,被编码过,所以必须以 ...

- UVA1616-Caravan Robbers(二分)

Problem UVA1616-Caravan Robbers Accept: 96 Submit: 946Time Limit: 3000 mSec Problem Description Lon ...

- [2] TensorFlow 向前传播算法(forward-propagation)与反向传播算法(back-propagation)

TensorFlow Playground http://playground.tensorflow.org 帮助更好的理解,游乐场Playground可以实现可视化训练过程的工具 TensorFlo ...

- python入门学习:2.列表简介

python入门学习:2.列表简介 关键点:列表 2.1 列表是什么2.2 修改.添加和删除元素2.3 组织列表 2.1 列表是什么 列表,是由一系列按特定顺序排列的元素组成.你可以创建包含字母表 ...