寄存器,移位寄存器的电路原理以及verilog代码实现

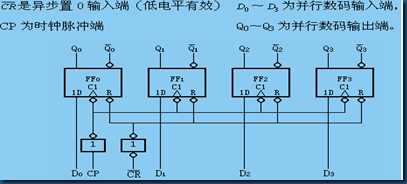

寄存器:用以存放二进制代码的电路,下图为由维特阻塞D触发器组成的4位数码寄存器:

逻辑功能分析:

1.异步端CR置0时,输出置0;

2.同步并行置数:D0~D3为4个输入代码,当CP上升沿到达时,D0~D3被同时并行置入。

3.在置数端为1,CP端为0时,保持不变。

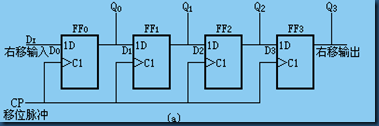

2.移位寄存器:具有存放数码和使数码逐位右移或左移的电路称为移位寄存器。

移位寄存器按照不同的分类方法可以分为不同的类型。 如果按照移位寄存器的移位方向来进行分类, 可以分为左移移位寄存器、移位寄存器和双向移位寄存器等;如果按照工作方式来分类,可以分为串入/串出移位寄存器、串入/并出移位寄存器和并入/串出移位寄存器等。

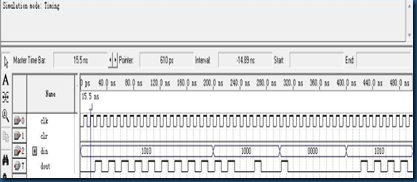

以下为异步清零的4位并入串出移位寄存器(输入为并行数据,输出为串行数据)

module reg_bc(clk,clr,din,dout);

input clk,clr; // 输入时钟端,清零端(高电平有效)

input[3:0] din; // 数据输入端

output dout; // 数据输出端

reg[1:0] cnt;

reg[3:0] q;

reg dout;

always@(posedge clk) // 时钟上升沿触发

begin

cnt<=cnt+1; //cnt 自加 1

if(clr) // 判断清零信号是否有效

begin

q<=4'b0000; //q 置 置 0

end

else

begin

if(cnt>0) // 判断 cnt 是否大于 0

begin

q[3:1]<=q[2:0]; //q 中的值向左移 1 位

end

else if(cnt==2'b00) // 判断 cnt 是否为 0

begin

q<=din; //把 把 din 的值赋予 q

end

dout<=q[3]; //把 把 q 的最高位输出

end

end

寄存器,移位寄存器的电路原理以及verilog代码实现的更多相关文章

- verilog代码 想法验证---与寄存器输出有关

verilog代码 想法验证---与寄存器输出有关 1. module test_mind( input wire clk, input wire reset, input wire i, outpu ...

- 【接口时序】6、IIC总线的原理与Verilog实现

一. 软件平台与硬件平台 软件平台: 1.操作系统:Windows-8.1 2.开发套件:ISE14.7 3.仿真工具:ModelSim-10.4-SE .ChipScope 硬件平台: 1. FPG ...

- 【接口时序】4、SPI总线的原理与Verilog实现

一. 软件平台与硬件平台 软件平台: 1.操作系统:Windows-8.1 2.开发套件:ISE14.7 3.仿真工具:ModelSim-10.4-SE 硬件平台: 1. FPGA型号:Xilinx公 ...

- SPI总线的原理与Verilog实现

转载地址:https://www.cnblogs.com/liujinggang/p/9609739.html 一. 软件平台与硬件平台 软件平台: 1.操作系统:Windows-8.1 2.开发套件 ...

- FPGA边沿检测Verilog代码

FPGA边沿检测Verilog代码(上升沿,下降沿,双边沿) 实现思路:用两个一位寄存器直接异或可以实现 代码实现: module edge_detect( input clk, input rs ...

- Verilog代码规范I

Verilog代码规范I "规范"这问题 "规范"这个富含专业气息的词汇(个人感觉),其实规范这种东西,就是大家都约定熟成的东西,一旦你不遵守这个东西,专业人士 ...

- u-boot移植总结(三)(转)S3C2440对Nand Flash操作和电路原理(基于K9F2G08U0A)

S3C2440对Nand Flash操作和电路原理(基于K9F2G08U0A) 转载自:http://www.cnblogs.com/idle_man/archive/2010/12/23/19153 ...

- 串口接收端verilog代码分析

串口接收端verilog代码分析 `timescale 1ns / 1ps ////////////////////////////////////////////////////////////// ...

- verilog 代码分析与仿真

verilog 代码分析与仿真 注意:使用vivado 自带的仿真工具, reg和wire等信号需要赋予初始值 边沿检测 module signal_test( input wire cmos_pcl ...

随机推荐

- mosquitto: error while loading shared libraries: libwebsockets.so.12: cannot open shared object file

错误描述: # mosquitto -c /etc/mosquitto/mosquitto.conf -dmosquitto: error while loading shared libraries ...

- List/Map 导出到表格(使用注解和反射)

Java 的 POI 库可以用来创建和操作 Excel 表格,有时候我们只需要简单地将 List 或 Map 导出到表格,样板代码比较多,不够优雅.如果能像 Gson 那样,使用注解标记要导出的属性, ...

- 第一阶段:Java基础 1.JAVA开发介绍---6. Java基本数据类型

Java 的两大数据类型: 内置数据类型(基本数据类型) 引用数据类型 本数据类型: Java语言提供了八种基本类型.六种数字类型,一种字符类型,还有一种布尔型. byte,short,int,lon ...

- 物联网学习笔记三:物联网网关协议比较:MQTT 和 Modbus

物联网学习笔记三:物联网网关协议比较:MQTT 和 Modbus 物联网 (IoT) 不只是新技术,还是与旧技术的集成,其关键在于通信.可用的通信方法各不相同,但是,各种不同的协议在将海量“事物”连接 ...

- CDN: trunk Repo update failed - CocoaPods

解决方案: 1.podfile文件中添加source源: source 'https://github.com/CocoaPods/Specs.git' 2.执行 pod repo remove t ...

- 91.用js遍历原生json数据

<!doctype html> <html lang="en"> <head> <meta charset="UTF-8 ...

- CTFd平台搭建以及一些相关问题解决

CTFd平台搭建以及一些相关问题解决 一.序言 因为想给学校工作室提高一下学习氛围,随便带学弟学妹入门,所以做了一个ctf平台,开源的平台有CTFd和FBCTF,因为学生租不起高端云主机所以只能选择占 ...

- .NET异步资料收集

个人认为应该是.NET关于并行编程 / 异步编程最权威的内容来源(虽然看起来里面的内容离现在已经好几年了,但是大部分内容都不过时) https://devblogs.microsoft.com/pfx ...

- 关于mybaits的注解@Param

一.含义 @param作为dao层的注解,为了解决多个参数时,参数类型不一致的问题. <select id="findEmpById" resultType="co ...

- Centos 7 中的ulimit -n 65535 对进程的文件句柄限制不生效??

今日闲来无事,就看群里大佬吹牛逼了,偶然一条技术疑问提出来了,神奇啊,作为广大老司机技术交流群体竟然还有这么深入的研究? 大佬问:这个文件句柄限制怎么设置了/etc/security/limits.c ...