单周期CPU设计的理论基础

写在前面:本博客内容为本人老师原创,严禁任何形式的转载!本博客只允许放在博客园(.cnblogs.com),如果您在其他网站看到这篇博文,请通过下面这个唯一的合法链接转到原文!

本博客全网唯一合法URL:http://www.cnblogs.com/acm-icpcer/p/9291767.html

1.指令集设计:

CPU的指令类型根据其操作的不同,可以分为下面七类。

(1)计算类指令(Computational)

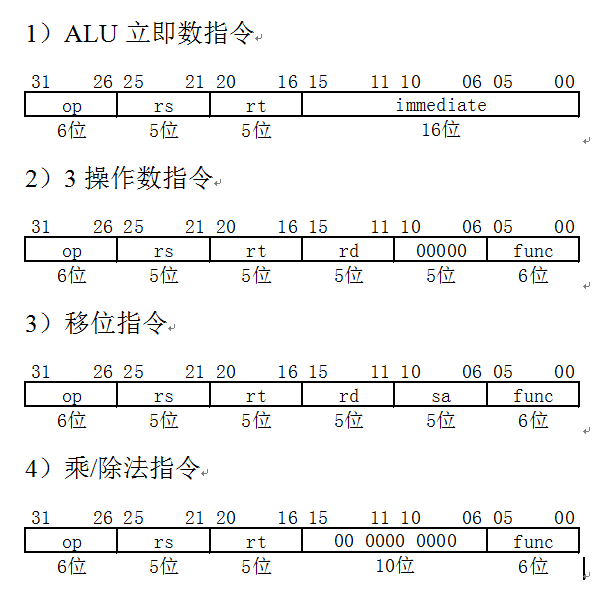

计算类指令用于执行算术操作,乘/除,逻辑操作和对寄存器进行移位操作。这些指令有两种类型:寄存器类型和立即数类型。寄存器类型的指令使用两个源寄存器的值作为源操作数,立即数类型使用一个寄存器和立即数作为源操作数。根据操作的不同,这些指令分为下面4种:

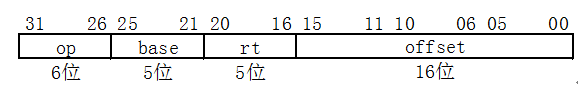

(2)Load/Store指令

Load和Store指令都为立即数(I-type)类型,用来在存储器和通用寄存器之间的储存和装载数据。值得一提的是MIPS指令集只有该类指令访问内存,而其他指令都在寄存器之间进行,所以指令的执行速度较高。该类指令只有基址寄存器的值加上扩展的16位有符号立即数一种寻址模式,数据的存取方式可以是字节(byte)、字(word)和双字(Double word)。

指令格式:

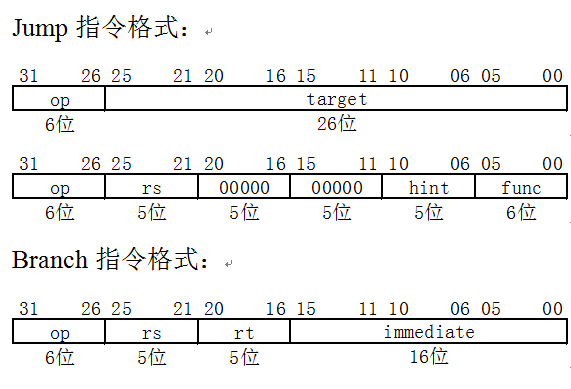

(3)跳转/分支指令(jump & branch)

跳转和分支指令改变程序流。所有的跳转和分支指令都会产生的一个延迟槽(delay slot)。紧跟着跳转/分支指令后的指令(delay slot中的指令)也被执行,然后在跳转目的的第一条指令从存储器中取出并执行,这是在指令的流水线执行时获得更高效率。

(4)寄存器传送指令

寄存器传送指令用来在系统的通用寄存器(GPR)、乘除法专用寄存器(HI、LO)之间传送数据,这些指令分为有条件传送和无条件传送2种类型。

(5)专用指令

专用指令用来产生软件中断,当执行这类指令的时候,CPU产生异常并转入中断处理程序。这些指令有系统调用(Syscall),暂停(Break)和Trap指令等,主要用于软件的异常处理。

(6)协处理器指令

协处理器指令对协处理器进行操作。协处理器的Load和Store指令是立即数类型,每个协处理器指令的格式依协处理器不同而不同。

(7)系统控制协处理器(CP0)指令

系统控制协处理器(CP0)指令执行对CP0寄存器的操作来控制处理器的存储器并执行异常处理。

本实验设计只选取了20条典型的MIPS指令来描述CPU逻辑电路的设计方法。下表列出了本实验的所涉及到的20条MIPS指令。

20条MIPS指令

|

R型指令 |

|||||||

|

指令 |

[31:26] |

[25:21] |

[20:16] |

[15:11] |

[10: 6] |

[5:0] |

功能 |

|

Add |

000000 |

rs |

rt |

rd |

000000 |

100000 |

寄存器加 |

|

Sub |

000000 |

rs |

rt |

rd |

000000 |

100010 |

寄存器减 |

|

And |

000000 |

rs |

rt |

rd |

000000 |

100100 |

寄存器与 |

|

Or |

000000 |

rs |

rt |

rd |

000000 |

100101 |

寄存器或 |

|

Xor |

000000 |

rs |

rt |

rd |

000000 |

100110 |

寄存器异或 |

|

Sll |

000000 |

00000 |

rt |

rd |

sa |

000000 |

左移 |

|

Srl |

000000 |

00000 |

rt |

rd |

sa |

000010 |

逻辑右移 |

|

Sra |

000000 |

00000 |

rt |

rd |

sa |

000011 |

算术右移 |

|

Jr |

000000 |

rs |

rt |

rd |

000000 |

001000 |

寄存器跳 |

|

I型指令 |

|||||||

|

Addi |

001000 |

rs |

rt |

immediate |

立即数加 |

||

|

Andi |

001100 |

rs |

rt |

immediate |

立即数与 |

||

|

Ori |

001101 |

rs |

rt |

immediate |

立即数或 |

||

|

Xori |

001110 |

rs |

rt |

immediate |

立即数异或 |

||

|

Lw |

100011 |

rs |

rt |

offset |

取数据 |

||

|

Sw |

101011 |

rs |

rt |

offset |

存数据 |

||

|

Beq |

000100 |

rs |

rt |

offset |

相等转移 |

||

|

Bne |

000101 |

rs |

rt |

offset |

不等转移 |

||

|

Lui |

001111 |

00000 |

rt |

immediate |

设置高位 |

||

|

J型指令 |

|||||||

|

J |

000010 |

address |

跳转 |

||||

|

Jal |

000011 |

address |

调用 |

||||

R型指令的op均为0,具体操作由func指定。rs和rt是源寄存器号,rd是目的寄存器号。移位指令中使用sa指定移位位数。

I型指令的低16位是立即数,计算时需扩展到32位,依指令的不同需进行零扩展和符号扩展。

J型指令的低26位是地址,是用于产生跳转的目标地址。

2.总体电路设计:

本实验所设计的单周期CPU的总体电路结构如图所示。

本实验所设计的CPU主要组成部分有:运算器(ALU)、控制器(Control Unit)、寄存器堆(Register Files)、取指电路及相关基础部件(如选择器)等构成。

具体的代码实现请看:

Verilog HDL语言实现的单周期CPU设计(全部代码及其注释)

tz@COI HZAU

2018/7/10

单周期CPU设计的理论基础的更多相关文章

- 单周期cpu设计代码解读

目录 写在前面 单周期cpu设计代码讲解 概念回顾 Verilog代码讲解 写在前面 欢迎转载,转载请说明出处. 单周期cpu设计代码讲解 概念回顾 一.电子计算机的部件 分为:中央处理器(cpu). ...

- 单周期CPU设计

终于有点时间了,恰好多周期的设计也已经完成,其实只想写写多周期的,无奈单周期补上才好,哈哈哈~ —————+—————黄金分割线—————+————— 首先要理解什么叫单周期CPU(与后面多周期CPU ...

- Verilog HDL语言实现的单周期CPU设计(全部代码及其注释)

写在前面:本博客为本人原创,严禁任何形式的转载!本博客只允许放在博客园(.cnblogs.com),如果您在其他网站看到这篇博文,请通过下面这个唯一的合法链接转到原文! 本博客全网唯一合法URL:ht ...

- P4-verilog实现mips单周期CPU

最近对学习的掌控可能出现了问题,左支右绌,p2挂了,p2.p3.p4.p5每周在计组花的连续时间少了很多,学习到的东西也少了很多,流水线都还没真正开始写,和别人比落后了一大截,随笔自然就荒废了,我得尽 ...

- 为什么现在使用多周期CPU,而单周期CPU被弃用?

最初设计的CPU结构简单,内部不复杂.之所以制造它是为了让机器自动跑程序,算数. 早期CPU都是单周期的,人们没考虑那么多,性能啥的.就让CPU每个时钟周期跑一个指令,这些时钟周期等长.这样下来,有的 ...

- 使用logisim搭建单周期CPU与添加指令

使用logisim搭建单周期CPU与添加指令 搭建 总设计 借用高老板的图,我们只需要分别做出PC.NPC.IM.RF.EXT.ALU.DM.Controller模块即可,再按图连线,最后进行控制信号 ...

- Vivado实战—单周期CPU指令分析

引言 不知道你是否和我有过同样的感受,<计算机组成原理>这门学科学起来如此的艰难:一节课下来,教室黑板上留下了满满的 "足迹",看上去也挺简单的,不就是 0 和 1 ...

- 单周期CPU

一个时钟周期执行一条指令的过程理解(单周期CPU): https://blog.csdn.net/a201577F0546/article/details/84726912 单周期CPU指的是一条指令 ...

- 使用Verilog搭建一个单周期CPU

使用Verilog搭建一个单周期CPU 搭建篇 总体结构 其实跟使用logisim搭建CPU基本一致,甚至更简单,因为完全可以照着logisim的电路图来写,各个模块和模块间的连接在logisim中非 ...

随机推荐

- 大数高精度计算库gmp简介

1.编译安装,我用的ubuntu18.04 $sudo apt-get install m4 //默认没安装,gmp用这个 $tar -jvxf gmp-.tar.bz2 //解压 $cd gmp- ...

- 译:4.RabbitMQ Java Client 之 Routing(路由)

在上篇博文 译:3.RabbitMQ 之Publish/Subscribe(发布和订阅) 我们构建了一个简单的日志系统 我们能够向许多接收者广播日志消息. 在本篇博文中,我们将为其添加一个功能 - ...

- 【iCore4 双核心板_ARM】例程七:WWDG看门狗实验——复位ARM

实验原理: STM32内部包含窗口看门狗,通过看门狗可以监控程序运行,程序运行错误时,未在 规定时间喂狗(提前或超时),自动复位ARM,本实验通过按键按下,停止喂狗,从而产 生复位. 核心代码: in ...

- Linux expect 使用(免密登录跳板机)

登录公司的跳板机是挺麻烦的事,首先要ssh,然后输入密码,有的公司可能还要动态密码,前两步操作都是固定的,所以能免去前两步的操作就会方便很多(线上出问题也能尽快登上去,免得紧张密码一直输错,哈哈哈). ...

- 树莓派做路由器_配置防火墙filter和nat转发_转载

转自:https://blog.csdn.net/hustsselbj/article/details/45866681 如果用树莓派当作路由器转发有线和无线网络,则需要对iptables进行相关配置 ...

- Java编程的逻辑 (83) - 并发总结

本系列文章经补充和完善,已修订整理成书<Java编程的逻辑>,由机械工业出版社华章分社出版,于2018年1月上市热销,读者好评如潮!各大网店和书店有售,欢迎购买,京东自营链接:http: ...

- Memcached 总结 启动多个Memcached服务 配置文件详解

一. 1.解压下载的安装包到指定目录. 2.服务安装,使用管理员权限运行以下命令: c:\memcached\memcached.exe -d install 二.同一台Windows机器中启动多个M ...

- [Bayes] Improve HMM step by step

以下是HMM,当emission probability变为高斯时,只需改变其中相关部分即可,也就是下图最后一行. 如下可见,在优化过程中套路没有太大的影响,但变为高斯后表达变得更精确了呢. 当然,这 ...

- [Algorithm] Warm-up puzzles

闲下来后,需要讲最近涉及到的算法全部整理一下,有个indice,方便记忆宫殿的查找 MIT的算法课,地球上最好:https://ocw.mit.edu/courses/electrical-engin ...

- Kubernetes – Ingress

用户在 Kubernetes 上部署的服务一般运行于私有网络,Pod和Service 提供了 hostPort,NodePort等参数用于暴露这些服务端口到K8S节点上,供使用者访问.这样的方法有明显 ...