System Verilog MCDF(二)

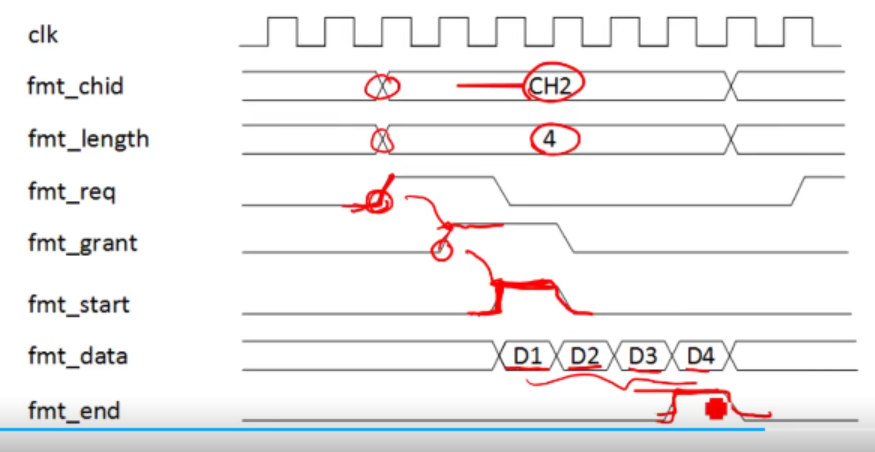

整形器的接口时序:

reg,grant是维持了两个clk的。

chid ,length在发送数据期间不可以变化。

第一个data数据必须在start上升沿的同一个clk发送。

reg,grant两者之间至少相差一个clk。

grand表示自己的内存足够存储要求数据的长度的空间。表示的数据包能够接受。

data必须连续的发送,之间不能够有间隔。

end是在最后一个data的一开始就拉高。

System Verilog MCDF(二)的更多相关文章

- System Verilog MCDF(一)

- 【转】uvm 与 system verilog的理解

http://www.cnblogs.com/loves6036/p/5779691.html 数字芯片和FPGA的验证.主要是其中的功能仿真和时序仿真. 验证中通常要搭建一个完整的测试平台和写所需要 ...

- system verilog中的跳转操作

在verilog中,使用disable声明来从执行流程中的某一点跳转到另一点.特别地,disable声明使执行流程跳转到标注名字的声明组末尾,或者一个任务的末尾. verilog中的disable命令 ...

- system verilog中的类型转换(type casting)、位宽转换(size casting)和符号转换(sign casting)

类型转换 verilog中,任何类型的任何数值都用来给任何类型赋值.verilog使用赋值语句自动将一种类型的数值转换为另一种类型. 例如,当一个wire类型赋值给一个reg类型的变量时,wire类型 ...

- 一段比较有意思的代码——介绍system verilog中的新增幅值语句

system verilog中新加了很多幅值语句,虽然都只适用于阻塞幅值,但是在某些场合中非常实用. 下面是一段有意思的代码,覆盖了一些用法. package definitions; typedef ...

- System Verilog基础(一)

学习文本值和基本数据类型的笔记. 1.常量(Literal Value) 1.1.整型常量 例如:8‘b0 32'd0 '0 '1 'x 'z 省略位宽则意味着全位宽都被赋值. 例如: :] sig1 ...

- (转)新手学习System Verilog & UVM指南

从刚接触System Verilog以及后来的VMM,OVM,UVM已经有很多年了,随着电子工业的逐步发展,国内对验证人才的需求也会急剧增加,这从各大招聘网站贴出的职位上也可以看出来,不少朋友可能想尽 ...

- System Verilog随笔(1)

测试文件该怎么写? 首先看一个简单代码案例: `timescale 1ns/10ps //1 module test; //2 intput wire[15:0] a; output reg[15 ...

- System Verilog基础(二)

这一篇笔记主要记录Procedural,Process,Task and function,Interface和Communication中值得注意的点. 1.Procedural 写testbenc ...

随机推荐

- Manjaro 蓝牙连接问题

1 问题描述 蓝牙不能连接,或者连接上了没有声音. 2 解决方案 首先确保相应软件包存在: sudo pacman -S bluez bluez-utils pulseaudio-bluetooth ...

- Salesforce学习之路(七)Visualforce结合Reports展示图表

Salesforce作为一款CRM系统,个人觉得最重要的环境便是在于数据的展示和联动,而Salesforce也本身提供了相当强大的功能,Report在展示图表的方面十分强大,前段时间更是宣布以157亿 ...

- Word 查找和替换字符串方法

因为项目需要通过word模板替换字符串 ,来让用户下载word, 就在网上找了找word查找替换字符串的库或方法,基本上不是收费,就是无实现,或者方法局限性太大 .docx 是通过xml来存储文字和其 ...

- SQL 查询的执行顺序

SELECT语句的完整语法如下 SELECT DISTINCT <select_list> FROM <left_table> <join_type> JOIN & ...

- 不可不知的CSS小技巧

一.表单部分 1.禁止textarea文本域的缩放 resize:none; 2.去除初始化textarea下拉条 overflow:auto; 3.如何让表单中的选项按钮,点击文字也能选中? < ...

- vue2整个项目中,数据请求显示loading图----------未完成阅读,码

一般项目中,有时候会要求,你在数据请求的时候显示一张gif图片,然后数据加载完后,消失.这个,一般只需要在封装的axios中写入js事件即可.当然,我们首先需要在app.vue中,加入此图片.如下: ...

- hdu4869 费马小+快速幂

思路:费马小+快速幂 无论怎么翻,每一步的1出现的可能个数的奇偶性是一样的,因为奇数 - 偶数 = 奇数,偶数 - 偶数 = 偶数,有一张牌被重叠了,那么就减去一个偶数2,所以怎么重叠都不 ...

- UVA11388GCD LCM

题意: 输入两个整数G,L,找出两个正整数a,b使得gcd(a ,b)=G,lcm(a ,b)=L,如果有多组解,输出最小的a的那组,如果没解,输出-1. 思路: 比较简单,如 ...

- Django中图形验证码(django-simple-captcha)

django-simple-captcha 在网站开发的登录页面中,经常会需要使用到图形验证码来验证.在Django中,django-simple-captcha库包提供了图形验证码的使用. 下面我们 ...

- 注解配置定时器Scheduling

注解配置定时器配置 package com.demo; import org.springframework.context.annotation.Configuration; import org. ...