FPGA知识大梳理(四)FPGA中的复位系统大汇总

本文整合特权(吴厚航)和coyoo(王敏志)两位大神的博文。我也很推崇这两位大神的书籍,特权的书籍要偏基础一下,大家不要一听我这么说就想买coyoo的。我还是那一句话,做技术就要step by step。闲言少叙,直入正题。

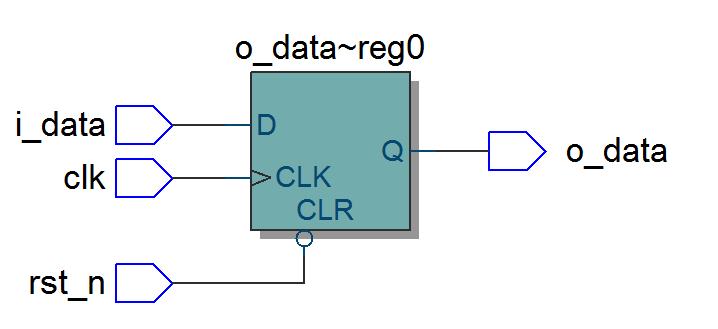

一,异步复位

先看这个电路,就是异步复位的例子。reset使用了reg的复位端

用代码实现的话是这个样子

module reset_test (

clk ,

rst_n ,

i_data,

o_data

); input clk ;

input rst_n ;

input i_data ;

output reg o_data ; always @ (posedge clk or negedge rst_n)

if(!rst_n) o_data <= 'd0 ;

else o_data <= i_data ; endmodule

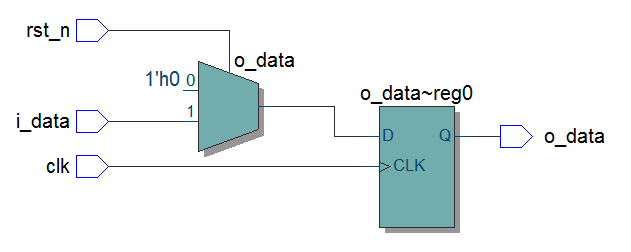

二,同步复位

首先也是先看电路,这是QuartusPrime15.1综合同步复位程序后的 RTL Viewer

代码如下

module reset_test (

clk ,

rst_n ,

i_data,

o_data

); input clk ;

input rst_n ;

input i_data ;

output reg o_data ; always @ (posedge clk )

if(!rst_n) o_data <= 'd0 ;

else o_data <= i_data ; endmodule

细心的同学有没有发现,很多的博文里面贴出的电路图,输入端那里不是一个2选1多路选择器,而是一个与门。所以我才说明我的综合器是QuartusPrime15.1。当然这个不是重点,重点是同步复位比异步复位多用了器件。数据也是多穿过一个器件。

对比:

异步复位的优点:1,节省了器件,这个在ASIC中显的尤为重要。2,减小了数据路径的传播延时。提高了系统响应频率。3,即刻生效,不依赖于时钟是否到来。

异步复位的缺点:由于reset信号时序是不定的,reset释放的时候会让异步复位系统出现亚稳态。

同步复位的优点:1,降低了亚稳态的出现。注意是降低了,而不是完全消除。如果reset毛刺或者是触发时间点不在clock上升沿的setup和hold时间内那就万事大吉,可是如果不是这个时间点,依然会有亚稳态。2,有利于时序分析。由于同步的reset信号必须由clock捕获到才有效,所以容易被时序分析工具分析到它的余量slack

同步复位的缺点:1,多使用了器件。2,增加了数据路劲传输时间

节省器件和增大F是asic的必争之地,所以目前大神们也喜欢在它身上进行改进,叫 异步复位的同步释放

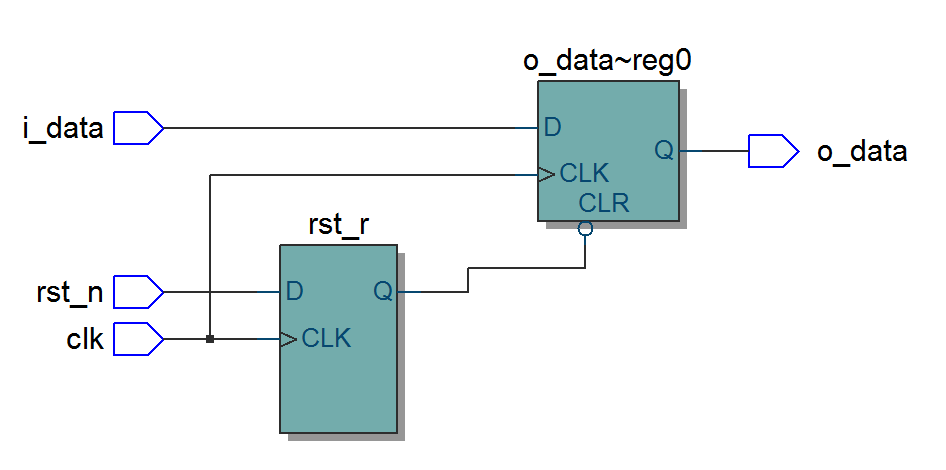

3,异步复位的同步释放第一版

此种方式是事先将reset信号打一拍,去除了reset的毛刺同时,reset释放的时候也能实现与clock同步。表面上看可以说是一个完美的方案。

然而问题出来了,一梦君曾经在面试一个岗位的时候被问过这个异步复位同步释放的问题,当我画出电路图的时候,面试官当即问我一句:如果clock挂了,你的系统岂不是还不能复位了?我顿时哑口无言。随后只好说,你说的没错,这个确实没有考虑到。当然我说这个绝对不是想去责怪谁,如果没有这些大神们在博客上奉献着他们的技术资料,我们不可能了解到这么多,只怪自己没有去深究。同时也希望读者们能深究我的博文缺陷。

这里非常感谢白菜小弟,在 FPGA知识大梳理(三)verilogHDL语法入门(2)知识汇总这篇博文中指出 “assign中使用的 blocking ”这一句话的原本意思是想告诉大家assign后面是使用 “=”,而不能使用“<=”。这么理解是没有错,但是表述不对,根据VerilogHDL_2001_standard,assign是Continuous assignments (连续性赋值语句)不存在阻塞非阻塞之分,阻塞非阻塞只针对于procedural assignment(过程性赋值语句) ,所以assign后面当然是“=”。

好了,说了这么多,该回到这个同步复位的异步释放问题上来了

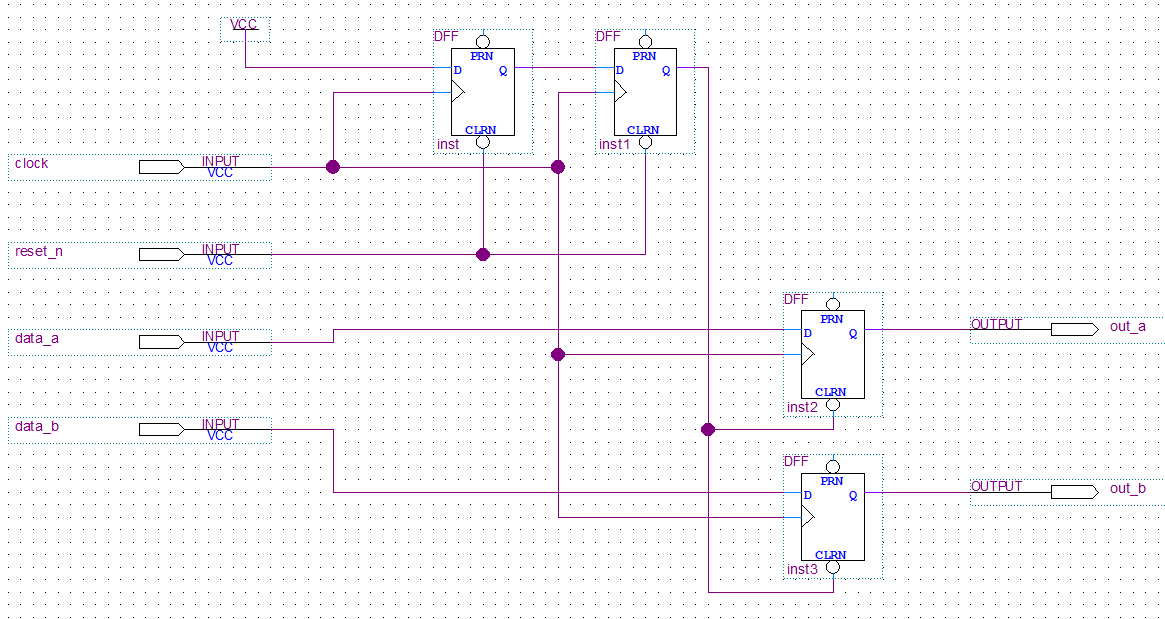

4,改进型的异步复位同步释放

程序是

//`default_nettype none module reset_test (

clock ,

reset_n ,

data_a,

data_b,

out_a,

out_b

); input clock,reset_n ;

input data_a,data_b ;

output out_a,out_b ; reg reg1 ,reg2 ;

reg reg3 ,reg4 ;

wire rst_n ; assign out_a = reg1 ,

out_b = reg2 ,

rst_n = reg4 ; always @ (posedge clock or negedge reset_n)

if(!reset_n) begin

reg3 <= 'd0 ;

reg4 <= 'd0 ;

end

else begin

reg3 <= 'd1 ;

reg4 <= reg3 ;

end always @ (posedge clock or negedge rst_n)

if(!rst_n) begin

reg1 <= 'b0 ;

reg2 <= 'd0 ;

end

else begin

reg1 <= data_a ;

reg2 <= data_b ;

end endmodule

reg3,reg4 . 异步复位产生rst_n ,由于异步复位的及时性,所有的reg都会复位。reset_n释放后,只有在clock到来之后,VCC传输到rst_n系统才会运转。所以实现了同步释放。

这个样子就万事大吉了吗?还缺一点点。在reset_n前面需要加一个滤波去抖的模块才算完美。如果你觉得有更完美的方案,欢迎提出来!

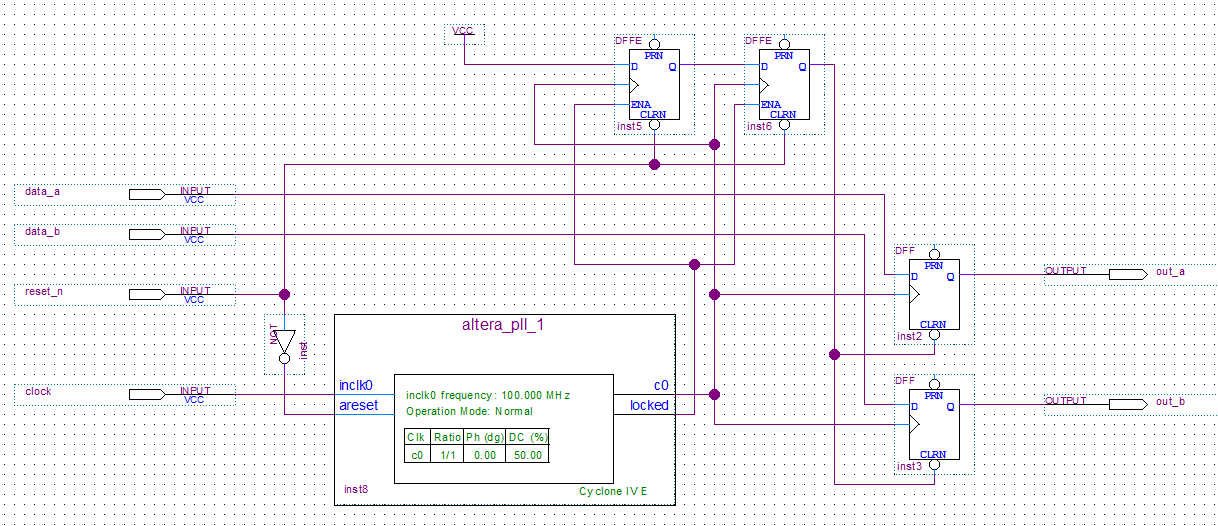

5,异步复位同步释放PLL版

在绝大多数的 工程中需要使用到PLL,那么有PLL的工程复位系统又有点不一样了哦。

也就是在pll没有准备好的时候,系统还是在复位的状态等待

代码实现是

module reset_test (

clock ,

reset_n ,

data_a,

data_b,

out_a,

out_b

); input clock,reset_n ;

input data_a,data_b ;

output out_a,out_b ; reg reg1 ,reg2 ;

reg reg3 ,reg4 ;

wire rst_n ;

wire pll_clk ,pll_lock; assign out_a = reg1 ,

out_b = reg2 ,

rst_n = reg4 ; always @ (posedge clock or negedge reset_n)

if(!reset_n) begin

reg3 <= 'd0 ;

reg4 <= 'd0 ;

end

else if(pll_lock) begin //pll clock is ready

reg3 <= 'd1 ;

reg4 <= reg3 ;

end

else begin

reg3 <= 'd0 ;

reg4 <= 'd0 ;

end //data flow -------------------------------

always @ (posedge clock or negedge rst_n)

if(!rst_n) begin

reg1 <= 'b0 ;

reg2 <= 'd0 ;

end

else begin

reg1 <= data_a ;

reg2 <= data_b ;

end altera_pll_0 U_0 (

.areset (!reset_n) ,

.inclk0 (clock),

.c0 (pll_clk),

.locked (pll_lock)

); endmodule

这复位算是告一段落了。如果你有更好的设计,请赐教。

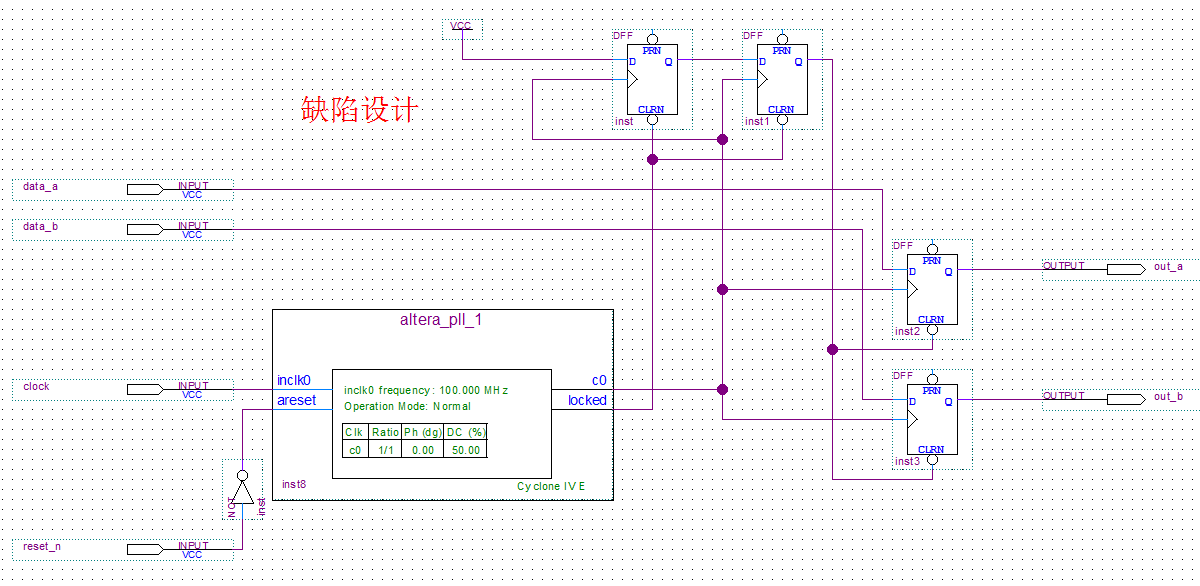

最后留下一个小问题,也是一梦君本人之前一直用的复位方式。如下图。 或者是inst(reg3)和inst1(reg4)都没有,直接将pll_locked直接连接到后续data flow部分的reset端。读者自行对比哦,哈哈

FPGA知识大梳理(四)FPGA中的复位系统大汇总的更多相关文章

- FPGA基础入门篇(四) 边沿检测电路

FPGA基础入门篇(四)--边沿检测电路 一.边沿检测 边沿检测,就是检测输入信号,或者FPGA内部逻辑信号的跳变,即上升沿或者下降沿的检测.在检测到所需要的边沿后产生一个高电平的脉冲.这在FPGA电 ...

- FPGA设计中的复位

(1)异步复位与同步复位的写法 1.异步复位与同步复位的区别? 同步复位:若复位信号在时钟有效边沿到来时刻为有效,则执行一次复位操作. 优点: 1)同步复位是离散的,所以非常有利于仿真器的仿真: 2) ...

- FPGA做正则匹配和网络安全,究竟有多大的优势?

FPGA做正则匹配和网络安全,究竟有多大的优势? 西电通院专用集成电路课程学习 云导播 网络安全已经被提升为国家战略的高度,高校里面的新增的一级学科,去年9月份,中央网信办.教育部公布了“一流网络安全 ...

- 逆向知识第十四讲,(C语言完结)结构体在汇编中的表现形式

逆向知识第十四讲,(C语言完结)结构体在汇编中的表现形式 一丶了解什么是结构体,以及计算结构体成员的对其值以及总大小(类也是这样算) 结构体的特性 1.结构体(struct)是由一系列具有相同类型或不 ...

- Expo大作战(四)--快速用expo构建一个app,expo中的关键术语

简要:本系列文章讲会对expo进行全面的介绍,本人从2017年6月份接触expo以来,对expo的研究断断续续,一路走来将近10个月,废话不多说,接下来你看到内容,讲全部来与官网 我猜去全部机翻+个人 ...

- Expo大作战(十四)--expo中消息推送的实现

简要:本系列文章讲会对expo进行全面的介绍,本人从2017年6月份接触expo以来,对expo的研究断断续续,一路走来将近10个月,废话不多说,接下来你看到内容,讲全部来与官网 我猜去全部机翻+个人 ...

- 关于Xilinx FPGA JTAG下载时菊花链路中的芯片数量

关于Xilinx FPGA JTAG下载时菊花链路中的芯片数量 emesjx | 2014-08-13 13:13:30 阅读:1793 发布文章 当一个系统中含有多片(2片以上)Xil ...

- FPGA设计经验谈 —— 10年FPGA开发经验的工程师肺腑之言

FPGA设计经验谈 —— 10年FPGA开发经验的工程师肺腑之言 2014年08月08日 14:08 看门狗 关键词: FPGA 作者:friends 从大学时代第一次接触FPGA至今已有10多 ...

- 寻找数组中的第K大的元素,多种解法以及分析

遇到了一个很简单而有意思的问题,可以看出不同的算法策略对这个问题求解的优化过程.问题:寻找数组中的第K大的元素. 最简单的想法是直接进行排序,算法复杂度是O(N*logN).这么做很明显比较低效率,因 ...

随机推荐

- hdu-4468-Spy-KMP+贪心

题目链接: http://acm.hdu.edu.cn/showproblem.php?pid=4468 题目意思: 给你一个串r,求一个串s,使得s的前缀1+s的前缀2+s的前缀3+...+s的前缀 ...

- 利用CSS3特性巧妙实现漂亮的DIV箭头

DIV箭头用于表现DIV内容的指向,是使用非常普遍的一种表现形式,例如新浪微博的消息转发: 还有傲游网站的导航条: 像傲游账户上方这种箭头更需要多幅图片以表现箭头和hover的效果. 传统的实现方式都 ...

- log4j.xml配置示例

这是log4j1.x版本讲解,log4j-1.2.16.jar 1. 一般的log4j.xml的两种配置方式: 1.Logger 完成日志信息的处理定义输出的层次和决定信息是否输出DEBUG&l ...

- Oracle查询表结构的常用语句

1. 查询表结构基本信息 select * from user_tables t,user_tab_comments c where c.table_name = t.table_name and t ...

- 删除除了 id 号不同,其他都相同的学生冗余信息

删除除了 id 号不同,其他都相同的学生冗余信息2.学生表 如下:id 号 学号 姓名 课程编号 课程名称 分数1 2005001 张三 0001 数学 692 2005002 李四 0001 数学 ...

- HiveQL与SQL区别

转自:http://www.aboutyun.com/thread-7327-1-1.html 1.Hive不支持等值连接 SQL中对两表内联可以写成:select * from dual a,dua ...

- sqlserver存储过程及易错点

create PROCEDURE [dbo].[xiao_adduser] @username NVARCHAR(), @password NVARCHAR(), @adddate DATETIME ...

- Expression Language

EL找不到属性会返回"" page –- request --- session --- application ------------------------------- ...

- (转)C++笔记:面向对象编程基础

非常棒的总结 http://blog.csdn.net/liufei_learning/article/details/21312701 面向对象编程基础 面向对象编程基于三个基本概念: 数据抽象-类 ...

- 【原创】Libjpeg 库使用心得(一) JPEG图像DCT系数的获取和访问

[原创]继续我的项目研究,现在采用Libjpeg库函数来进行处理,看了库函数之后发现C语言被这些人用的太牛了,五体投地啊...废话不多说,下面就进入正题. Libjpeg库在网上下载还是挺方便的,这里 ...