FPGA Asynchronous FIFO设计思路

FPGA Asynchronous FIFO设计思路

将一个多位宽,且在不停变化的数据从一个时钟域传递到另一个时钟域是比较困难的。

同步FIFO的指针比较好确定,当FIFO counter达到上限值时候,FIFO为满,当FIFO counter为0时,FIFO为空。

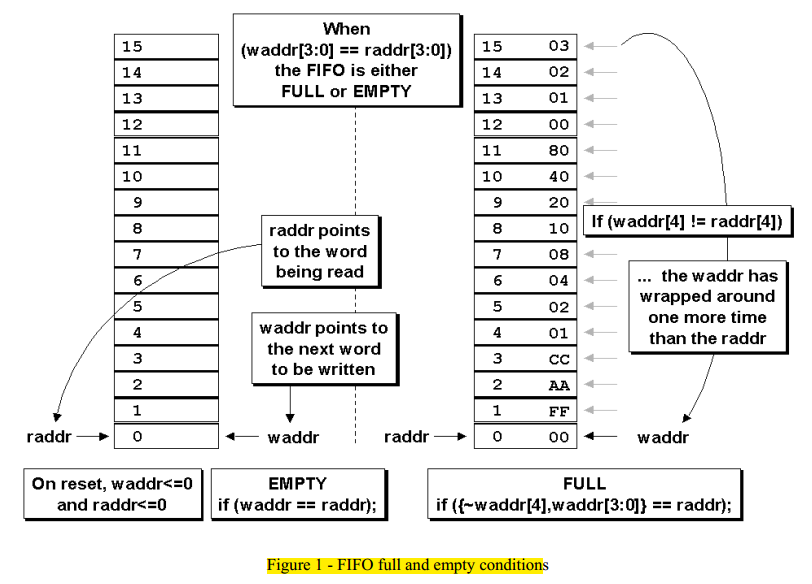

异步FIFO有writer pointer 和 read pointer两个指针,writer pointer 总是指向下一个要被写入的位置,read pointer 总是指向下一个将被读出的数据。没有必要使用这样一种机制:接受端的用户逻辑先给一个时钟周期到FIFO,使得指针指向将要读出的数,然后接收端在用一个时钟周期来锁存读出的数据。

怎样判定FIFO的空满,当写指针追上读指针时候,FIFO为满,当读指针追上写指针时候,FIFO为空,既然当FIFO为空和满的时候,都是读指针和写指针相等,那该怎么判断空满呢,在读写指针前面多加一位,当读写指针走过FIFO最后一个地址的时,并从头再来,这个时候最高位进行翻转,其他地址位进行清零处理。如果,读写指针最高位相同,说明他们翻转的次数相同,这种情况只有读在写指针的后面,快要空。如果读写指针最高位不同,说明他们翻转的次数不同,这种只能是写指针在读指针的后面,快要满。

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer: chensimin

//

// Create Date: 2018/10/24 17:31:22

// Design Name:

// Module Name: beh_fifo

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

////////////////////////////////////////////////////////////////////////////////// module beh_fifo #( parameter ASIZE = ,

parameter DSIZE = )

( input wire wclk,

input wire wrst_n,

input wire winc,

input wire [DSIZE- : ] wdata, output wire wfull,

output wire rempty, input wire rclk,

input wire rrst_n,

input wire rinc,

output wire [DSIZE- : ] rdata ); //--------------------------------------------------------------

//写一个数据,指针加一

parameter MEMDEPTH = << ASIZE;

reg [ASIZE : ] wptr;

reg [DSIZE- : ] ex_mem [ : MEMDEPTH-]; always @(posedge wclk or negedge wrst_n)

begin

if(!wrst_n)

wptr <= ;

else if(winc && !wfull)

begin

ex_mem[wptr[ASIZE- : ]] <= wdata;

wptr <= wptr + ;

end

end //--------------------------------------------------------------

//将rptr读指针,同步到wclk时钟域,打了三拍

reg [ASIZE : ] wrptr3;

reg [ASIZE : ] wrptr2;

reg [ASIZE : ] wrptr1; always @(posedge wclk or negedge wrst_n)

begin

if(!wrst_n)

{wrptr3, wrptr2, wrptr1} <= ;

else

{wrptr3, wrptr2, wrptr1} <= {wrptr2, wrptr1, rptr};

end //--------------------------------------------------------------

//读指针加一

reg [ASIZE : ] rptr;

always @(posedge rclk or negedge rrst_n)

begin

if(!rrst_n)

rptr <= ;

else if(rinc && !rempty)

rptr <= rptr + ;

end //--------------------------------------------------------------

//将写指针同步到读指针时钟域

reg [ASIZE : ] rwptr3;

reg [ASIZE : ] rwptr2;

reg [ASIZE : ] rwptr1; always @(posedge rclk or negedge rrst_n)

begin

if(!rrst_n)

{rwptr3, rwptr2, rwptr1} <= ;

else

{rwptr3, rwptr2, rwptr1} <= {rwptr2, rwptr1, wptr};

end //-------------------------------------------------------------- assign rdata = ex_mem[rptr[ASIZE- : ]];

assign rempty = (rptr == rwptr3);

assign wfull = (( wptr[ASIZE-:] == wrptr3[ASIZE-:] ) &&

( wptr[ASIZE] != wrptr3[ASIZE] )); endmodule

以上只是一个很粗糙的FIFO模型,并不能拿来综合和使用。(待续................)

FPGA Asynchronous FIFO设计思路的更多相关文章

- FPGA Asynchronous FIFO设计思路(2)

FPGA Asynchronous FIFO设计思路(2) 首先讨论格雷码的编码方式: 先看4bit的格雷码,当MSB为0时,正向计数,当MSB为1时,即指针已经走过一遍了,最高位翻转,此时的格雷码是 ...

- FPGA学习:VHDL设计灵活性&不同设计思路比较

概要 由于VHDL编程实现数字电路具有很高的灵活性,为多种不同的思路编写实现同一种功能提供了可能.这些不同的设计思路,在耗费资源,可靠性,速度上也有很大的差异,往往需要我们根据实际需求和资源条件选择适 ...

- 基于FPGA的异步FIFO设计

今天要介绍的异步FIFO,可以有不同的读写时钟,即不同的时钟域.由于异步FIFO没有外部地址端口,因此内部采用读写指针并顺序读写,即先写进FIFO的数据先读取(简称先进先出).这里的读写指针是异步的, ...

- 小梅哥FPGA数字逻辑设计教程——基于线性序列机的TLC5620型DAC驱动设计

基于线性序列机的TLC5620型DAC驱动设计 目录 TLC5620型DAC芯片概述: 2 TLC5620型DAC芯片引脚说明: 2 TLC5620型DAC芯片详细介绍: 3 TLC ...

- FPGA异步时钟设计中的同步策略

1 引言 基于FPGA的数字系统设计中大都推荐采用同步时序的设计,也就是单时钟系统.但是实际的工程中,纯粹单时钟系统设计的情况很少,特别是设计模块与外围芯片的通信中,跨时钟域的情况经常不可避免. ...

- TYPESDK手游聚合SDK服务端设计思路与架构之一:应用场景分析

TYPESDK 服务端设计思路与架构之一:应用场景分析 作为一个渠道SDK统一接入框架,TYPESDK从一开始,所面对的需求场景就是多款游戏,通过一个统一的SDK服务端,能够同时接入几十个甚至几百个各 ...

- 分享一个CQRS/ES架构中基于写文件的EventStore的设计思路

最近打算用C#实现一个基于文件的EventStore. 什么是EventStore 关于什么是EventStore,如果还不清楚的朋友可以去了解下CQRS/Event Sourcing这种架构,我博客 ...

- ENode框架单台机器在处理Command时的设计思路

设计目标 尽量快的处理命令和事件,保证吞吐量: 处理完一个命令后不需要等待命令产生的事件持久化完成就能处理下一个命令,从而保证领域内的业务逻辑处理不依赖于持久化IO,实现真正的in-memory: 保 ...

- WebGIS中快速整合管理多源矢量服务以及服务权限控制的一种设计思路

文章版权由作者李晓晖和博客园共有,若转载请于明显处标明出处:http://www.cnblogs.com/naaoveGIS/ 1.背景 在真实项目中,往往GIS服务数据源被其他多个信息中心或者第三方 ...

随机推荐

- 制作voc2007数据格式的数据集

最近按照博主分享的流程操作,将自己遇到的难题记录下来,附上原博文链接:https://blog.csdn.net/jx232515/article/details/78680724 使用SSD训练自己 ...

- MySql5.7多实例配置教程

最近朋友在搞在Linux上配置MySql5.7多实例教程,在网上查询了很多资料,一直报各种各样的错误,后来在网上搜了一篇博客,根据其配置,最近是配置成功了 参考配置连接:https://blog.cs ...

- 今天想写一下关于SpringMVC的视图解释器

昨天我写了一下SpringMVC最爱金丹的项目的配置流程,这样搭建完项目之后呢我发现我每个请求都得加个.do什么的后缀,这让我开发得很不爽,于是呢今天就想配置一下这个试图解释器,这样做的目的有两个:第 ...

- re+正则01

# 正则 # 正则 ''' 正则就是带语法的字符串, 用来匹配目标字符串得到想要得字符串结果 ''' # 部分语法: # 1.单独字符 # \d 范围 [0-9] # \D 范围刨除 [^0-9] # ...

- python常量 变量 数据类型 注释 交互 if语句

1.认识python python的创始人吉多·范罗苏姆(Guido van Rossum )龟叔在89年圣诞节开始开发python python属于解释型语言,强类型定义语言. 编译型/解释型:编译 ...

- 使用VMware Workstation 14 Player或者Oracle VM VirtualBox安装Fedora-Workstation-netinst-x86_64-27-1.6操作系统的相关记录

无论是在使用哪个(VMware或者Oracle VM)都遇到了一个问题:即使在安装完Fedoras操作系统之后,进行Reboot还是会进入之前一摸一样的安装界面,相当于再次安装.然而最最有效的解决办法 ...

- git教程:管理修改

转载:管理修改 现在,假定你已经完全掌握了暂存区的概念.下面,我们要讨论的就是,为什么Git比其他版本控制系统设计得优秀,因为Git跟踪并管理的是修改,而非文件. 你会问,什么是修改?比如你新增了一行 ...

- 数组中array==null和array.length==0的区别

//代码public class Test1 { public static void main(String[] args) { int[] a1 = new int[0]; int[] a2 = ...

- docker3

Docker容器的设置资源(cpu,内存)限制: #docker run –memory=200M xxxx-image --vm 1 –verbose #docker run --cpu-s ...

- 利用JQuery 解析MVC控制器传到前台的Json数据

<script type="text/javascript"> function Getweb() { var name = $("#CityName&quo ...