关于音频总线IIS的学习---Verilog

关于音频总线IIS的学习---Verilog

主要思想: 在分析寄存器的值变化的时候,将时钟的边沿分两边来看,边沿之前,边沿之后,在always 块语句里面用来分析判断的寄存器的值,都应该用边沿变化之前的值,边沿之后, always块做操作的寄存器的值才发生变化。

记住,一定是寄存器量(reg定义的),像audio_sck 这种外部输入的异步信号要判断上升沿状态下的即时值。

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer: chensimin

//

// Create Date: 2018/06/08 13:33:40

// Design Name:

// Module Name: iis_s2p

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

////////////////////////////////////////////////////////////////////////////////// module iis_s2p( input wire reset,

input wire clk, // 12.288

input wire audio_sck,

input wire audio_ws ); //-----------------------------------------------

//将外部输入的sck,ws 信号通过时钟clk进行同步采集进来

reg audio_sck_d = ;

reg audio_ws_d = ;

always @(posedge clk or posedge reset)

begin

if(reset)

begin

audio_sck_d <= 'b0;

audio_ws_d <= 'b0;

end else

begin

audio_sck_d <= audio_sck;

audio_ws_d <= audio_ws;

end

end //-----------------------------------------------

//监测audio_sck 信号的下降沿

//疑问:为什么不采用组合逻辑的方式

//assign sck_neg = audio_sck_d & ~audio_sck ;

reg sck_neg = ;

always @(posedge clk or posedge reset)

begin

if(reset)

sck_neg <= 'b0; else if (audio_sck_d & audio_sck)

sck_neg <= 'b1; else

sck_neg <= 'b0;

end endmodule /* add_force {/iis_s2p/clk} -radix hex {1 0ns} {0 5000ps} -repeat_every 10000ps

add_force {/iis_s2p/audio_sck} -radix hex {1 0ns} {0 20000ps} -repeat_every 40000ps

add_force {/iis_s2p/reset} -radix hex {1 0ns} {0 20ns} */

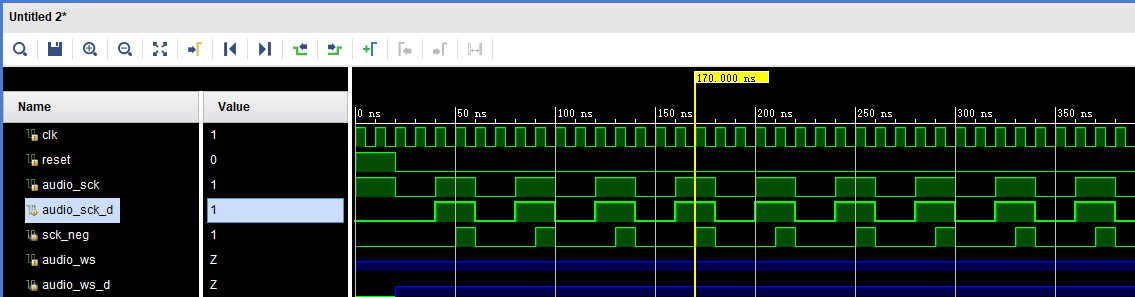

仿真结果:

分析:

1.从仿真结果可以看出为什么不能用通常的assign语句来检测sck的下降沿信号,因为sck_neg为外部输入信号,通过时钟采集存入sck_d寄存器中,两个信号波形完全一样,根本就不会有sck_neg置高的时候。

2.信号过了主时钟,存入寄存器,寄存器值的变化分析方法:

以主时钟的上升沿为边界,分为 :上升沿到来之前, 上升沿,上升沿之后,数据是在上升沿之后进行更新。

对于如下模块:

//-----------------------------------------------

//结合波形图来看,clk上升沿到来之前,寄存器中audio_sck_d的数据为0,clk上升沿时,将audio_sck_d里面的数据进行更新,clk上升沿之后,audio_sck_d里面的数据发生变化

//将外部输入的sck,ws 信号通过时钟clk进行同步采集进来

reg audio_sck_d = ;

reg audio_ws_d = ;

always @(posedge clk or posedge reset)

begin

if(reset)

begin

audio_sck_d <= 'b0;

audio_ws_d <= 'b0;

end else

begin

audio_sck_d <= audio_sck;

audio_ws_d <= audio_ws;

end

end

对于如下模块的分析:

//-----------------------------------------------

//主时钟clk上升沿到来之前,sck_neg,audio_sck_d,audio_sck 均为0 上身沿到来的时候,audio_sck_d, audio_sck信号的值进行更新,从0-1,此时并不满足if(audio_sck_d & audio_sck)的要求

//因此,第一个主时钟clk上升沿之后,sck_neg的值依旧保持为0, 下一个主时钟clk上升沿到来之前,audio_sck_d, audio_sck,的值为1,满足if(audio_sck_d & audio_sck)的要求,因此,在第二个clk上升沿之后,sck_neg的

//的值变为1.

//监测audio_sck 信号的下降沿

//疑问:为什么不采用组合逻辑的方式

//assign sck_neg = audio_sck_d & ~audio_sck ;

reg sck_neg = ;

always @(posedge clk or posedge reset)

begin

if(reset)

sck_neg <= 'b0; else if (audio_sck_d & audio_sck)

sck_neg <= 'b1; else

sck_neg <= 'b0;

end

关于音频总线IIS的学习---Verilog的更多相关文章

- I2S音频总线学习

IIS音频总线学习(一)数字音频技术 一.声音的基本概念 声音是通过一定介质传播的连续的波. 图1 声波 重要指标: 振幅:音量的大小 周期:重复出现的时间间隔 频率:指信号每秒钟变化的次数 声音按频 ...

- IIS原理学习

IIS 原理学习 首先声明以下内容是我在网上搜索后整理的,在此只是进行记录,以备往后查阅只用. IIS 5.x介绍 IIS 5.x一个显著的特征就是Web Server和真正的ASP.NET Appl ...

- I2S音频总线学习(二)I2S总线协议

http://blog.csdn.net/ce123_zhouwei/article/details/6919954

- 【接口时序】6、IIC总线的原理与Verilog实现

一. 软件平台与硬件平台 软件平台: 1.操作系统:Windows-8.1 2.开发套件:ISE14.7 3.仿真工具:ModelSim-10.4-SE .ChipScope 硬件平台: 1. FPG ...

- 【接口时序】4、SPI总线的原理与Verilog实现

一. 软件平台与硬件平台 软件平台: 1.操作系统:Windows-8.1 2.开发套件:ISE14.7 3.仿真工具:ModelSim-10.4-SE 硬件平台: 1. FPGA型号:Xilinx公 ...

- SPI总线的原理与Verilog实现

转载地址:https://www.cnblogs.com/liujinggang/p/9609739.html 一. 软件平台与硬件平台 软件平台: 1.操作系统:Windows-8.1 2.开发套件 ...

- 基于I2C总线的MPU6050学习笔记

MPU6050学习笔记 1. 简述 一直想自己做个四轴飞行器,却无从下手,终于狠下决心,拿出尘封已久的MPU6050模块,开始摸索着数据手册分析,一步一步地实现了MPU6050模块的功能,从MPU60 ...

- iis深入学习资源

iis站点:https://www.iis.net/overview/reliability/richdiagnostictools 感兴趣可以深入学习下iis

- 红外解码编码学习----verilog

在设计中运用红外遥控器可以很好的解决按键缺少的问题,还可以方便的控制产品. 红外发射部分: 红外发射管: 判断红外发射管的好坏 : 电路原理图: 接收部分: 传输的NEC协议: 本实验电路: veri ...

随机推荐

- CentOS7.5下安装Python3.7 --python3

1.将本地安装包上传到远程主机上 scp Python-3.7.0.tgz root@123.206.74.24:/root 2.扩展 安装Python之前安装Python相关的依赖包(主要是u红色部 ...

- 20190319xlVBA_根据考勤数据统计缺勤缺考数据

Sub SubtotalPickFile() Dim StartTime As Variant Dim UsedTime As Variant StartTime = VBA.Timer Dim fi ...

- 康拓展开-排列的hash

对于一个集合内所有元素的排列,康拓展开是一个无冲突的hash法.其规则便是将排列在逻辑上排好序,然后每个排列的序号即是hash值. 关键就在如何快速求出序号和快速还原啦. 首先我们确定一好集合内各元素 ...

- python-html基础操作

介绍: HTML 是网页内容的载体.包括文字,图片,信息等用户浏览的信息CSS 样式是改变内容外观表现.像字体,颜色,背景,边框等JavaScript 是实现网页上的特效效果.如鼠标滑过背景 ...

- 关于contenteditable属性

今天刷刷看看,看到了发说说框,发现居然不是textarea的,百思不得其解围.后来看到contenteditable,心想应该就是这个搞怪的吧,百度了下.w3c的解释是contenteditable属 ...

- StrokePlus常用脚本

1.按照时间创建文本文件并打开 文本文件并没有什么快捷方式,每次都要右键,找新建,找文本文档,临时写点什么还要保存,写名字,懒得写就打aa,bb的,挺烦的. 难点在于用lua没法知道当前鼠标所在的文件 ...

- Andriod Studio两种签名机制V1和V2的区别

Android Studio 2.2以上版本打包apk的时候,我们会发现多了个签名版本(v1.v2)选择,如下图红色方框所示 问题描述(v1和v2) Android 7.0中引入了APK Signat ...

- mysql数据库基础语句训练题

; -- ---------------------------- -- Table structure for course -- ---------------------------- DROP ...

- Linux过滤错误日志

grep -E 'at |Exception|exception|Error|error|Caused by' test.log

- Linux下查看CPU型号,内存大小,硬盘空间的命令

1 查看CPU 1.1 查看CPU个数 # cat /proc/cpuinfo | grep "physical id" | uniq | wc -l 2 **uniq命令:删除重 ...