有限状态机HDL模板

逻辑设计, 顾名思义, 只要理清了 逻辑 和 时序, 剩下的设计只是做填空题而已。

下面给出了有限状态机的标准设计,分别为 VHDL 和 Verilog 代码

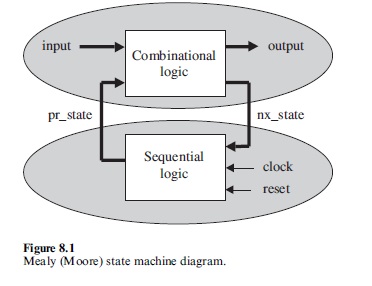

1 有限状态机

2 VHDL模板一

library IEEE;

use ieee.std_logic_1164.all; --! 1) 端口定义

entity <entity_name> is

port

(

DIN : in <data_type>;

RST : in std_logic;

CLK : in std_logic;

DOUT : out <data_type>

);

end <entity_name>; --! 2) 状态定义

architecture <arch_name> of <entity_name> is type state is (IDLE, ST1, ST2, ...);

signal c_state, n_state : state; begin --! 3) 时序逻辑

pfsmsyn: process (rst, clk)

begin

if (rst = '') then

c_state <= IDLE;

elsif (clk'event and clk='') then

c_state <= n_state;

endif;

end process; --! 4) 组合逻辑

pfsmlogic: process (din, c_state)

begin

case c_state is

when IDLE =>

if (din = ...) then

dout <= <value>; -- 输出

c_state <= state1; -- 状态

else ...

end if;

when ST1 =>

... ...

... ...

... ...

when others =>

... ... end case;

end process; end <arch_name>;

3 Verilog模板一

// 1) 端口声明

module fsm(clk, rst, ctrl, dout);

input clk, rst, ctrl;

output [n-:] dout; // n 取决于输出值的位数

reg [n-:] dout; // 2) 状态定义

parameter IDLE = , ST1 = , ST2 = , ST3 = , ....;

reg [m-:] c_state, n_state; // m 取决于‘“状态”数量的位数 // 3) 时序逻辑

always @ (posedge clk or posedge rst)

begin: SEQ

if (rst)

c_state = IDLE;

else

c_state = n_state;

end // 4) 组合逻辑

module @ (ctrl or c_state)

begin: COMB

case (c_state)

IDLE: begin

dout = <value0>;

n_state = ST1;

end

ST1: begin

dout = <value1>;

n_state = ST2;

end

ST2:

. . . . . .

. . . . . .

. . . . . .

endcase

end endmodule

参考资料:

<Circuit Design with VHDL> chapter 8 State Machines

<HDL Chip Design>

有限状态机HDL模板的更多相关文章

- 基于Unity有限状态机框架

这个框架是Unity wiki上的框架.网址:http://wiki.unity3d.com/index.php/Finite_State_Machine 这就相当于是“模板”吧,自己写的代码,写啥都 ...

- 基于Verilog HDL整数乘法器设计与仿真验证

基于Verilog HDL整数乘法器设计与仿真验证 1.预备知识 整数分为短整数,中整数,长整数,本文只涉及到短整数.短整数:占用一个字节空间,8位,其中最高位为符号位(最高位为1表示为负数,最高位为 ...

- 有限状态机FSM(自动售报机Verilog实现)

有限状态机FSM(自动售报机Verilog实现) FSM 状态机就是一种能够描述具有逻辑顺序和时序顺序事件的方法. 状态机有两大类:Mealy型和Moore型. Moore型状态机的输出只与当前状态有 ...

- 如何高效的编写Verilog HDL——进阶版

博主之前写过一篇文章来谈论如何高效的编写Verlog HDL——菜鸟版,在其中主要强调了使用Notepad++来编写Verilog HDL语言的便捷性,为什么说是菜鸟版呢,因为对于新手来说,在还没有熟 ...

- gVim编辑器 模板篇

上文介绍了gVim的常用操作,这次总结一下我自己常用的模板. 安装和配置好gVim后,在Program Files (x86)\Vim目录下有个“_vimrc”文件,双击选择gVim软件打开,在里面添 ...

- html5引擎开发 -- 引擎消息中心和有限状态机 - 初步整理 一

一 什么是有限状态机 FSM (finite-state machine),又称有限状态自动机,简称状态机,是表示有限个状态以及在这些状态之间的转移和动作等行为的数学模型.他对于逻辑以及 ...

- 转载.怎样在Quartus II中转化HDL文件为bsf文件?

步骤1 新建或打开Quartus II工程,用QII自带文本编辑器打开HDL文件. 图1 用QII自带的文本编辑器打开HDL文件 步骤2 选择File>Create / Update>Cr ...

- 算法复习——网络流模板(ssoj)

题目: 题目描述 有 n(0<n<=1000)个点,m(0<m<=1000)条边,每条边有个流量 h(0<=h<35000),求从点 start 到点 end 的最 ...

- win7+vim搭建+verilog HDL IDE

参考地址:http://www.huangdc.com/421 参考文章为2016年,部分更新贴于文章内了 安装下载vim vim在win下叫gvim,下载地址:https://www.vim.org ...

随机推荐

- mysql学习笔记 第九天

order by ,limit 和where子查询的使用 order by: order by 列名1,[列名2],[列名3]...(结果先按列1进行排序,在列1的相同的情况下,再按照列2的排序,以此 ...

- File文件的Api的各种方法

package com.immoc; import java.io.File; import java.io.IOException; public class Fileto { public sta ...

- python 学习之电脑的发展历史

电脑的发展历史 电脑的学名叫计算机,电脑是用来做计算的.在古时候,人们最早使用的计算工具可能是手指,英文单词“digit”既有“数字”的意思,又有“手指“的意思.古人用石头打猎,所以还有可能是石头来辅 ...

- SpringMVC中出现" 400 Bad Request "错误(用@ResponseBody处理ajax传过来的json数据转成bean)的解决方法

最近angularjs post到后台 400一头雾水 没有任何错误. 最后发现好文,感谢作者 SpringMVC中出现" 400 Bad Request "错误(用@Respon ...

- RCA端子颜色(红、白、黄)

RCA端子(红白黄)的作用: 黄:视频 红:左声道 白:右声道 RCA为两口插头,红色代表左声道,白色为右声道,3.5(AUX口)同样为立体声接头,虽然它只有一个端口,同样也具有左右声道分开传输的功能 ...

- Eclipse环境下使用Maven注意事项

在最新版本的Eclipse Java EE IDE for Web Developers中已经包含Maven 2 在File,New中可以看到Maven Project,新建, 按照步骤一路下来,要求 ...

- Webform(内置对象-Response与Redirect、QueryString传值、Repeater删改)

一.内置对象(一)Response - 响应请求对象1.定义:Response对象用于动态响应客户端请示,控制发送给用户的信息,并将动态生成响应.Response对象只提供了一个数据集合cookie, ...

- 2013 最新的 play web framework 版本 1.2.3 框架学习文档整理

Play framework框架学习文档 Play framework框架学习文档 1 一.什么是Playframework 3 二.playframework框架的优点 4 三.Play Frame ...

- javascript获取url信息的常见方法

先以"http://www.cnblogs.com/wuxibolgs329/p/6188619.html#flag?test=12345"为例,然后获得它的各个组成部分. 1.获 ...

- Mybatis学习记录(三)----理解SqlMapConfig.xml文件

SqlMapConfig.xml mybatis的全局配置文件SqlMapConfig.xml,配置内容如下: properties(属性) settings(全局配置参数) typeAliases( ...